基于FPGA芯片XC4VLX25实现软件无线电信号处理平台的设计

可编程逻辑

描述

本设计是针对软件无线电中频信号处理的需求而实现的一个通用硬件平台。

软件无线电是90年代兴起的一种充分结合软件和硬件优势的新技术,该技术源于军事领域对通信系统灵活性的特殊需要。自1992年Joe Mitola提出软件无线电以来,软件无线电在通信系统中的应用日益广泛。软件无线电是一种开放的模块化结构,物理实现上基于一个采用数字无线电(全数字通信收发机)技术的通用硬件平台,通过实时的软件控制,用户能定义该平台的工作模式,从而使一个硬件平台能实时地转变为不同技术标准的通信系统。它是一种实现无线通信的新的体系结构,其显著特点是开放性、可编程性和快速的可配置性。这是继模拟到数字、固定到移动之后,通信领域的又一次重大突破。

传统意义上软件无线电模拟前端之后的硬件主要由以下三个部分组成:高速模数与数模变换器、数字上下变频器和高速数字信号处理器。其中上下变频和信号处理常常有三种实现方式:ASIC、DSP和可编程逻辑器件。由于可编程逻辑器件在可重配置和灵活度上与生俱来的优越性,近些年来,国外市场上出现了一些基于FPGA的软件无线电信号处理通用平台。例如SANDANCE公司的SMT370开发板,NALLATECH公司的XtremeDSP开发套件等。本文介绍了一种自行设计实现的信号处理平台,它是以现场可编程逻辑器件FPGA为处理核心搭建起来的接收与测试的硬件环境。

1. 构成框架

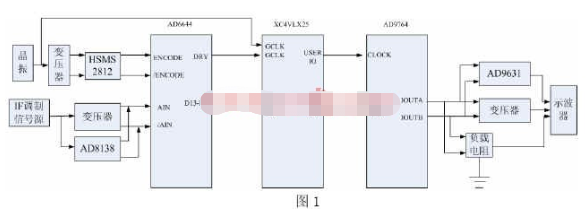

信号处理平台由高速数模转换器AD6644、高速模数转换器AD9764、XILINX公司Virtex-4系列FPGA芯片XC4VLX25、时钟电路和稳压电源电路组成,构成框架如图1所示。模拟中频信号由IF信号源提供,在时钟电路的控制下经AD6644采样以后输入到FPGA芯片。FPGA把该数字信号进行数字下变频和解调处理后送AD9764进行数模转换,最后将模拟输出信号送示波器进行测试。电路布局上分三块区域:输入模拟部分,数字信号处理部分和输出模拟部分,因此整个电路遵从模数混合的高速电路设计原则,采用八层电路板结构,模拟供电和数字供电分开,同时各个不同电压的数字供电也分开,内地层相应的分为模拟地、数字地和模拟地,三块地层分别以ADC和DAC作为交界,并在芯片下面通过磁珠或0Ω电阻分别相连。

2. 模数转换电路设计

2.1工作原理

AD6644是一款分辨率为14位,采样速率可达65MSPS的A/D转换器。它能够精确变换宽带模拟信号,具有100dB的无杂散动态失真范围,典型的SNR为74dB,功耗1.3W。很适合该系统的前端模数转换。

AD6644有互补的模拟输入引脚  和

和 。模拟信号采用差分输入。芯片内部把输入的模拟信号分级进行编码,在每一次编码以后就从总的信号中减去编码值对应的模拟信号的大小,将剩余信号再送往下一级,最后依次得到5位、5位和6位的编码一起送往数字误差校正逻辑修正后即得到14位并行数据输出。

。模拟信号采用差分输入。芯片内部把输入的模拟信号分级进行编码,在每一次编码以后就从总的信号中减去编码值对应的模拟信号的大小,将剩余信号再送往下一级,最后依次得到5位、5位和6位的编码一起送往数字误差校正逻辑修正后即得到14位并行数据输出。

2.2输入电路

AD6644的输入分为时钟输入和模拟信号输入两部分。

时钟从ENCODE和/ENCODE管脚输入。AD6644的采样时钟要求质量高且相位噪声低,如果时钟信号抖动较大,信噪比容易恶化,很难保证14位的精度。为了优化性能,AD6644的采样时钟信号采用差分形式。时钟信号可通过一个变压器或电容交流耦合到ENCODE 和 引脚,这两个引脚在片内被偏置,因此无需外加偏置。本设计中将一个低抖动的时钟信号用变压器从单端变成了差分信号。在变压器的输出端接两个反向的肖特基二级管,把输入到AD6644的时钟信号幅度限制在大约0.8V的峰峰值。

引脚,这两个引脚在片内被偏置,因此无需外加偏置。本设计中将一个低抖动的时钟信号用变压器从单端变成了差分信号。在变压器的输出端接两个反向的肖特基二级管,把输入到AD6644的时钟信号幅度限制在大约0.8V的峰峰值。

模拟信号从 和

和 输入。常常采用直流耦合和交流耦合两种差分的输入方式,这样有利于滤除偶次谐波分量、晶振的反馈信号和共模的干扰信号。AD6644的输入电压范围被偏置到对地2.4V。在使用变压器耦合的模式中,推荐的原副线圈匝数比为1:4。通常在副线圈和AD6644之间用电阻进行隔离,这样就可以限制从A/D器件流向副线圈的动态电流。在使用运放耦合的电路中,通常使用单端——差分转换的运放器AD8138,这种方式可以降低系统成本和电路规模。

输入。常常采用直流耦合和交流耦合两种差分的输入方式,这样有利于滤除偶次谐波分量、晶振的反馈信号和共模的干扰信号。AD6644的输入电压范围被偏置到对地2.4V。在使用变压器耦合的模式中,推荐的原副线圈匝数比为1:4。通常在副线圈和AD6644之间用电阻进行隔离,这样就可以限制从A/D器件流向副线圈的动态电流。在使用运放耦合的电路中,通常使用单端——差分转换的运放器AD8138,这种方式可以降低系统成本和电路规模。

3. FPGA电路设计

本设计选择的XC4VLX25是Virtex-4系列中的一款针对高性能逻辑设计应用的芯片。它包含了24192个逻辑单元,10752个slices,168个分布式RAM和最大1296K的嵌入式块RAM。

Virtex-4系列器件是通过把针对应用生成的比特流数据下载到内部存储器来进行配置的。由于XILINX FPGA的配置存储器是不能掉电保持数据的,因此必须在每次上电的时候都对它进行一次配置。

芯片上有M0,M1和M2三个配置模式管脚,通过它们可以在以下的配置模式中进行选择:串行主模式、串行从模式、并行主模式和并行从模式,这几种模式都是计算机先把数据加载到PROM芯片里面,PROM芯片再对FPGA进行配置。此外比特流还可以通过JTAG口直接进行下载,即JTAG/边界扫描模式。

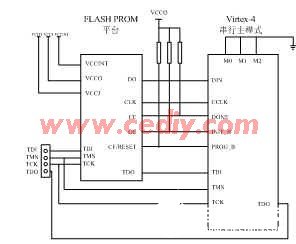

主模式和从模式是根据配置时钟(CCLK)的方向来确定的。在主模式下,FPGA通过内部振荡器来生成配置时钟,而在从模式下,配置时钟管脚(CCLK)是输入属性。本设计的电路板上采用了串行主模式和JTAG模式。

图2

串行主模式只需要少数几个信号就可以把PROM和FPGA的接口进行适配,配置过程中也不需要外部时钟源,因此它也是使用了PROM的各种配置模式中最为常用的。在该模式下,FPGA内部生成配置时钟,当/CF管脚为高电平时数据可以从PROM的D0脚获得,同时 和OE处于使能允许状态。新的数据在每一个时钟上升沿后的很短的时间内建立。电路连线如图2所示。

另外一个常用的配置模式是JTAG模式。一块Virtex-4 FPGA在上电的情况下就可以用计算机通过JTAG电缆直接进行配置。此时只需将上图中FPGA芯片的TCK、TMS、TDI、TDO和JTAG电缆对应的管脚连接起来就可以了。如果使用此模式,M2、M1和M0最好也相应的设置成边界扫描模式,即M2=1,M1=0,M0=1。

在以FPGA为中心设计电路板时需要注意,FPGA的输入输出信号都是高速信号,为了获得陡峭的上升沿和下降沿属性,走线应该尽量短。因此在对关键信号选择对应IO的时候,最好选择芯片最外围的管脚,这样在布线的时候可以使高速信号仅仅分布在最上面的信号层,而不需要通过过孔到电路板的其他层。数字信号和模拟信号应该分别在各自的地层之上的区域进行布线,并行的数字信号线两两之间应该加入地线以排除相互干扰。

4. 数模转换电路设计

Analog Devices公司生产的AD9764是高速D/A器件中适用于FPGA输出信号数模转换的一款芯片。它具有14位分辨率,高达125MSPS的转换速率,极佳的无杂散动态失真范围。差分电流输出为2-20mA, 5V电压下功耗为190mW、3V电压下功耗为45mW,边沿触发锁存。

4.1 工作原理

AD9764由数字和模拟两部分组成。数字部分能工作在125MHz时钟频率上,它包括边沿触发锁存和分段译码逻辑电路。模拟部分包括PMOS电流源、差分开关、1.20V 电压基准和一个基准控制放大器。满量程输出电流由基准控制放大器通过一个外部电阻  所调整,它的变化范围是 2-20mA,外部电阻与基准控制放大器和电压基准 Vrefio相连,由它来设定基准电流

所调整,它的变化范围是 2-20mA,外部电阻与基准控制放大器和电压基准 Vrefio相连,由它来设定基准电流

4.2 输出电路

AD9764的输出方式分为单端输出和差分输出两种,为了便于调试和比较,本设计中把这两种方式都做到了电路板中。

单端输出适用于那些需要单极电压输出的应用。当在Iouta或者Ioutb 和模拟地ACOM之间接入一个合适的负载电阻 Rload时,就可以得到一个正极性的输出电压。这种方式对那些需要获得直流耦合对地参考电压的应用来说不失为一个很好的选择。通常使用 Iouta管脚进行单端输出,因为该管脚的性能比 Ioutb 稍好一些。

除了单端输出,AD9764更多的是使用差分输出。差分输出一般利用变压器或者运放来实现。使用变压器可以为那些频谱处于该变压器通带范围内的信号提供最适宜的抗失真性能。变压器能够滤除信号的偶次谐波分量和很宽频带内的噪声干扰,此外还能提供电路的隔离。不过变压器方式只能提供交流耦合。在使用运放实现差分输出的时候,Iouta 和 Ioutb 两个管脚被配置成负载两个相等阻值的电阻,然后将两个电压信号差分输入到放大器中转化为输出信号。差分操作将有助于消除与Iouta 和 Ioutb 相关的共模误差源,比如噪声、失真和直流偏置。另外,与差分码相关的电流和其产生的电压 Vdiff是单端电压输出的两倍,为负载提供了两倍信号功率。

本文作者创新点:

1. 区别于常见的以DSP作为处理核心的实验平台,本设计采用FPGA器件来对信号进行处理。整个设计以通用性作为考虑重点,搭建了一个灵活的可配置的处理平台。以FPGA器件发展水平为技术基础,在普遍使用PDSP的应用领域使用FPGA来实现数字信号处理,这是一种对已有技术的新应用的探索(这种应用平台很适合于对软件无线电技术的研究)。

2. 采用XILINX新推出的具有强大DSP处理内核的Virtex-4系列FPGA,因而可以在该芯片上实现高性能DSP的应用,这是对FPGA传统功能的拓展。此外以高速、低功耗的系统设计标准来完成芯片的外围输入以及测试电路开发,从而可以发挥该芯片的最佳性能。

责任编辑:gt

-

无线电信号和脉冲信号的区别2024-02-05 3910

-

谁能做拦截无线电信号?2021-10-21 5268

-

软件无线电信号中频与采样频率的选择方法2021-06-10 1111

-

无线电信号的频谱如何划分2020-12-18 3058

-

使用WRAP软件实现民航无线电信号覆盖情况的仿真分析2020-08-06 1909

-

如何实现一种低功耗软件无线电信号处理平台2020-07-20 1017

-

如何利用FPGA设计软件无线电平台?2019-08-02 2268

-

无线电信号的发送和接收2019-03-09 16951

-

和大家分享一个基于6U VPX TMS320C6678+XC7K325T的信号处理板2018-12-19 3626

-

Xilinx_Virtex4-XC4VLX252016-02-17 2264

-

基于FPGA的心电信号处理研究与实现2015-10-30 684

-

利用FPGA实现的中频信号接收平台2010-07-28 925

-

无线电信号的频率及分段2009-06-30 19808

-

无线电信号处理电路图2008-05-12 1163

全部0条评论

快来发表一下你的评论吧 !