高集成度D/A转换器LTC2704-16的功能特性及应用分析

模拟技术

描述

1、概述

LTC2704-16是Linear公司生产的独立4通道16位D/A转换器。该D/A转换器具有4个独立的数模转换通道,转换速度快,可广泛应用于过程控制、工业自动化、增益控制、自检测设备等领域。

2、 LTC2704-16简介

2.1主要特性

LTC2704-16的主要特性如下:6种可编程输出范围:单极性:0 V~5 V,0 V~10 V;双极性:±5 V、±10 V、+2.5 V、-2.5 V~7.5 V;所有片上寄存器串行回读;输出驱动±5 mA;信号抖动《2 nV-sec;INL和DNL为1LSB;44引脚SSOP封装。

2.2引脚功能

LTC2704-16的引脚排列如图1所示,各引脚功能描述如下:

V-:模拟负电源。一般为-15 V,范围为-4.5 V~16.5 V。通常情况下,为了抗干扰需在模拟地之间并联2只1μF的旁路电容。

LDAC:异步DAC装载输入。当LDAC为低电平时,更新所有DAC。

CS/LD:同步片选与装载引脚。

SDI:串行数据输入端。当CS/LD为低电平时,数据在脉冲的上升沿载人。

SRO:串行回读数据输出端。脉冲的下降沿输出数据。回读数据在最后一位地址A0后输出。

SCK:串行时钟端。

CLR:异步清零端。当该引脚为低电平时,所有的码与span B2寄存器全部清零。所有的DAC输出也全部清零。

V+1:模拟电源为DAC的A和B通道提供模拟电源范围为4.5 V~16.5 V,一般为15 V。V+1与V+2不同。通常为了抗干扰应在模拟地之间接2只并联的1 μF的旁路电容。

V+2:模拟电源为DAC的C和D通道提供模拟电源,范围为4.5 V~16.5 V。一般为15 V。通常为了抗干扰应在模拟地之间连接2只并联的1μF的旁路电容。

GND:接地。

AGND:模拟地。

VDD:数字电源,范围为2.7 V~5.5 V。

RFLAG:RESET标志引脚。复位或清零时,该引脚输出低电平;更新命令结束时,该引脚为高电平。

REFG1:DAC的A和B,高阻抗输入,用于抑制噪声。

REFG2:DAC的C和D,高阻抗输入,用于抑制噪声。

REF1:DAC的A和B关联输入。

REF2:DAC的C和D关联输入。

REFM1:转换Amp输出,用于DAC A和DAC B。

REFM2:转换Amp输出,用于DAC C和DAC D。

VOSA、VOSB、VOSC、VOSD:分别为A、B、C、D4个DAC的偏移量调节端。输出范围为±5 V。

C1A、C1B、C1C、C1D:分别为A、B、C、D 4个DAC的反馈电容连接端。该引脚为输出放大器的负反馈输入直接提供输入端口。

RFBA、RFBB、RFBC、RFBD:分别为A、B、C、D 4个DAC的输出反馈电阻引脚。

OUTA、OUTB、OUTC、OUTD:分别为A、B、C、D4个DAC的输出引脚。

AGNDA、AGNDB、AGNDC、AGNDD:分别为A、B、C、D 4个DAC的信号地。

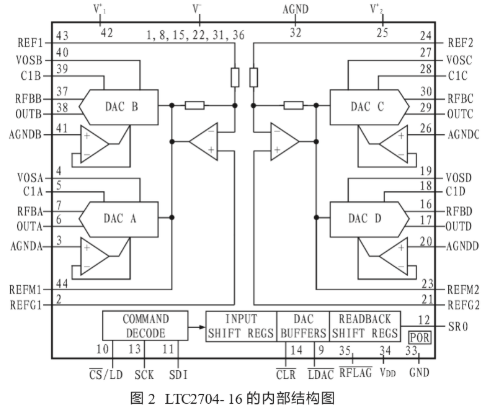

2.2 LTC2704-16的内部结构

图2为LTC2704-16的内部结构图。LTC2704-16共有4个DAC,每个DAC都是独立的,并都有独立的偏移量调节引脚与相应的信号地为AGNDA、AGNDB、AGNDC和AGNDD。LTC2704-16把这4个DAC分为两组,DAC A和DAC B为一组,DAC C和DAC D为一组。每一组共用一只转换放大器。每个DAC都有一个接地端,DAC A和DAC B共用REF1,DAC C和DAC D共用REF2。

2.3 LTC2704-16的工作方式

2.3.1复位与清零

当LTC2704-16上电时,所有的DAC都在5 V模式下,所有的内部DAC寄存器都被置0且DAC的输出全部为0 V。当CLR置低时,系统清零。指令和地址寄存器、数据码和B2缓冲寄存器全置0,DAC输出全置0。而B1缓冲寄存器保留,可使DAC恢复到原来状态。如果CLR在操作中已被声明,则不能保证B1缓冲寄存器的完整性,其内容应采用回读方式校对或取代。

2.3.2休眠模式

当LTC2704-16在休眠模式下,DAC则进入休眠模式。当DAC A和DAC B其中一个处于休眠状态时,而它们共用的转换放大器仍处于工作状态。只有当DAC A和DAC B都处于休眠状态时,共用的转换放大器才处于休眠状态。通过SRO引脚为DAC分配地址和读取DAC状态。第5个LSB位为休眠状态位。

2.3.3串口通讯

当CS/LD为低电平时,SDI引脚的数据在上升沿被装入移位寄存器。LTC2704的最小装载序列为24位:4位指令、4位地址和16位的数据。如果输入序列为32位,前8位必须为零,后面与24位的序列相同。

当CS/LD为低电平时,串行回读输出引脚(SRO)处于开放状态。数据在指令(C3~C0)和地址(A3~A0)之后移入SDI。对于24位的装载序列,16位的数据在第8个至第23个时钟下降沿被移出,控制器在第9个至第24个时钟上升沿将其移入。

当CS/LD为高电平时,SRO引脚处于高阻状态,CS/LD为低电平时,开始装载数据时,SRO输出低电平直到开始回读数据为止。

当异步装载引脚LDAC为低电平时,所有DAC更新数据(数据从缓冲寄存器B1拷贝到B2),CS/LD在操作中必须为高电平。

2.3.4回读功能

每个DAC有两对双缓冲数字寄存器,一对用于DAC码,一对用于输出span。每一个双缓冲寄存器包含B1和B2两个寄存器。B1是保持寄存器,当数据通过读操作被移入B1时,DAC输出不受影响。B2只能通过拷贝Bl的内容才能改变,B2的内容直接控制DAC输出电压和输出范同。

另外,每个DAC都有一个回读寄存器,当DAC接收到回读命令时,4个寄存器中的一个被拷贝到回读寄存器中,然后移位传输到SRO引脚。在任何读或更新指令的16位数据中,SRO都会移出命令指定的寄存器内容。这种循环回读模式可用于减少操作次数。

当设定了DAC的span后,span位是最后4个被移入;当通过SRO校对DAC的span位时,span位最后被移出。当span被回读时,输出DAC的休眠状态。

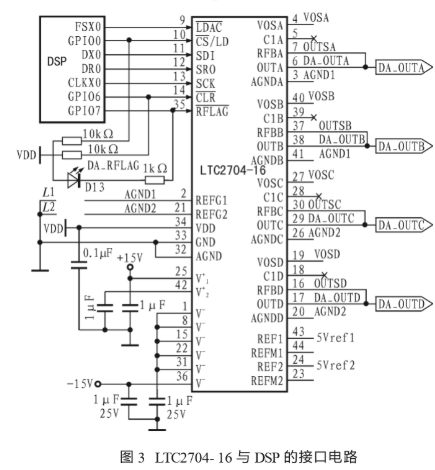

3、LTC2704-16的应用

图3所示为DSP与LTC2704-16的接口电路。DSP采用SPI方式控制DAC,FSX0与LDAC相连,帧同步信号控制LTC2704-16的4个DAC。当FSX0为低电平时,所有DAC更新。采用3个通用I/O端口(GPIO0、GPIO6、GPIO7)分别控制CS/LD、CLR和RFLAG,并都要连接上拉电阻。其中,RFLAG为标志引脚,当RFLAG为低电平时,D13发光。DAC的时钟信号也由DSP的CLKX0引脚提供。

无论是输入还是输出,均在CS/LD为低电平时产生。一般输入或输出序列都采用24位格式。在序列中前4位为指令,然后是4位DAC地址,最后是16位的数据。4位的DAC地址指定由哪个DAC完成指令和处理16位的数据,也可以同时选取所有DAC,同时处理相同的指令与数据。CS/LD为高电平时,SRO处于高阻状态,此时,可更新DAC。DAC的输出范同和输出电压是由B2寄存器决定,由于B2寄存器只能通过拷贝B1的内容才能改变,因此,更新时CS/LD必须为低电平,同时RFLAG变为低电平。当执行清零和复位命令时,除B1以外的所有寄存器全部清零,清零或复位后,DAC从B1寄存器读回原有状态。

LTC2704-16采用串口通信方式,与其他的同类器件相比,无需占用更多引脚就可实现并行数据传输,节省资源。LXC2704-16最大特点是自动校准,每个通道都是独立的,并带有反馈功能,可使数据输出更加精确,抗干扰性更强。同读功能可有效地减少操作次数,节约了CPU资源。

4、结束语

LTC2704-16是一款高集成度D/A转换器,与采用多路DAC输出并分别放大的同类器件相比,设计和布局简单。这款D/A转换器功能强大、结构简单,可广泛应用于工业设备和各种仪器的设计中。

责任编辑:gt

-

全新高集成度的DC/DC转换器LTC31072018-09-27 1422

-

A/D转换器LTC2400功能及应用2018-12-12 4549

-

多通道A/D转换器LTC2704-16及其应用2010-12-14 751

-

12位A/D转换器AD5742009-01-14 5666

-

工业和控制应用的高集成度四通道16 位、SoftSpan、电2009-10-05 1185

-

CS5531/32/33/34 高集成度的模数转换器2010-10-20 1708

-

工业和控制应用的高集成度四通道DAC2017-05-16 1204

-

片上集成A/D转换器分析2017-09-20 724

-

LTC1604:带停机功能的高速16位333ksps采样A/D转换器2021-04-27 830

-

兼容AD7124,国产高集成度模数转换器广泛用于PLC/DCS2024-09-02 1462

-

使用DM365的DCDC转换器的高集成度、高效率电源解决方案2024-10-10 394

-

LTC1603:高性能16位采样A/D转换器的全面解析2026-04-07 489

-

高性能16位采样A/D转换器LTC1608:特性、应用与设计要点2026-04-08 127

-

高性能16位采样A/D转换器LTC1604:特性、应用与设计要点2026-04-09 431

-

详解LTC2704:多功能电压输出数模转换器2026-04-13 75

全部0条评论

快来发表一下你的评论吧 !