基于FPGA技术和CVSD编解码算法实现语音编解码器的设计和仿真研究

可编程逻辑

描述

64 Kbit/s的A律或μ律的对数压扩PCM编码在大容量的光纤通信系统和数字微波系统中已得到广泛应用,但由于占用较大的传输带宽和具有复杂的成帧结构,PCM编码不适合无线语音系统的应用。连续可变斜率增量(Continuously Variable Slope Delta,CVSD)调制以其较低的应用难度、成本和编码速率,较好的语音质量广泛应用于战术通信网、卫星通信、蓝牙等无线语音传输领域。近年来FPGA不断发展演化,并在构架方面针对DSP应用有了显著增强。这些增强使得FPGA能够支持各领域的众多复杂DSP应用,如电信(基站信号处理、雷达信号处理等)、多媒体处理(视频处理、音频信号处理等)及其他应用领域,笔者结合FPCA的灵活性、强大的数字信号处理能力、较短的开发周期,提出了基于FPGA的32 Kbit/s CVSD语音编解码器。

1、 CVSD原理

增量调制(Delta Modulation,DM)用一位编码表示相邻样值的相对大小,从而反映出抽样时刻波形的变化趋势,它分为线性增量调制(Linear Delta Modulation,LDM)和自适应增量调制(Adaptive Delta Modulation,ADM)。LDM中采用固定的量化台阶△,在量化编码的过程中会引起两类失真,一类是斜率过载失真,它是由于量化台阶△过小,跟不上信号波形中斜率陡峭部分造成的,另一类是颗粒失真,它是由于量化台阶△过大,在信号波形斜率较小部分造成的。CVSD是一种自适应增量ADM算法,动态调整量化台阶△的大小随输入信号变化,当输入信号幅度变化率增大时,量化台阶相应增大,当输入信号幅度变化率减小时,量化台阶相应减小。

2、 CVSD编解码算法

2.1 编码算法

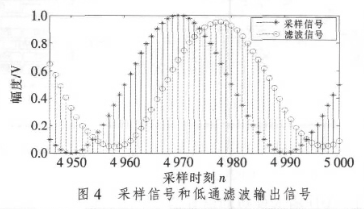

编码算法流程如图1所示,x(n)为输入语音采样信号,采样频率fs=32 kHz,xp(n)为一阶预测值,d(n)为输入采样信号x(n)和一阶预测值xp(n)的差值,β为量阶衰减因子,△0为初始量阶。模块L实现电平转换,输入c(n)=1时输出为+1,输入c(n)=0时输出为-1,因此模块L的输出值为2c(n)-1。

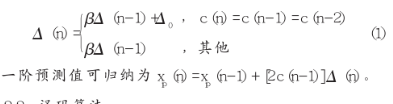

当x(n)≥xp(n)时,d(n)≥0,编码输出c(n)=1,当x(n)《xp(n)时,编码输出c(n)=0。CVSD编码过程中,动态地调整量化台阶△(n),当检测到连续3个编码“1”或者连续3个编码“0”时,说明信号斜率陡峭,这时量阶增大△0。

2.2 译码算法

译码算法流程如图2所示,它是编码的逆过程,由于积分器输出的xQD(n)是阶梯波,有较高的谐波分量,这里通过一个数字低通滤波器平滑积分器的输出。当c(n)=1时,xQD(n)=xQD(n-1)+△(n);当c(n)=0时,xQD(n)=xQD(n-1)-△(n)。其中量阶△(n)的取值同编码算法。

3、 FPGA的设计和实现

3.1 参数设计

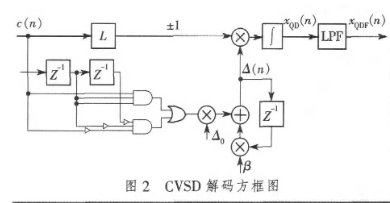

CVSD编译码算法中涉及到量阶衰减因子β、初始量阶△0和低通滤波器系数的设计。量阶衰减因子满足:β=1-T/τ,T表示语音信号的周期,语音信号频率f=300~3 400 Hz,所以周期T=0.29~3.30 ms,τ为音节时间常数,一般情况下τ=5~10ms。△0的选取很重要,如果△0选取过小,会导致初始的一段时间量化的数字信号与输入信号之间存在较大的失真,需要经过较长的时间才能跟踪上输入信号,为减少颗粒失真和过载失真,根据欧洲通信组织标准,结合多次的MATLAB仿真测试,取β=0.855,△0=0.043,如图3所示。

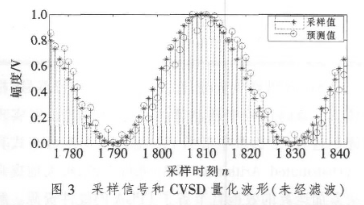

升余弦窗具有较好的旁瓣抑制和阻带衰减,数字低通滤波器设计成14阶升余弦窗有限脉冲响应(Finite Impulse Response,FIR)滤波器,其参数采样率fs=32 kHz由于语音信号频谱集中在300~3 400 Hz,数字低通滤波器通带截止频率设计为fc=4 kHz/32 kHz=0.125,FIR滤波器系数向量B=[0.0029 0.0086 0.02600.058 0 0.1000 0.1400 0.1645 0.1645 0.1400 0.1000 0.058 0 0.0260 0.008 6 0.002 9]。如图4所示,由于信号经过14阶FIR低通滤波器,输出信号与原采样信号相比存在一定的延时,经低通滤波后原信号得到了较好的恢复。

3.2 CVSD编解码器

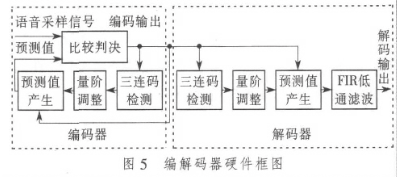

硬件设计时采用自顶向下的设计方法,将编解码器分成各种功能模块。CVSD编码器负责处理采样频率32 kHz采样的16 bit语音信号,由比较判决模块、三连码检测模块、量阶调整模块和预测值产生模块组成,硬件结构如图5所示。比较判决模块将预测值产生模块产生的预测值与语音信号值进行比较,如果输入语音信号值≥预测值,则编码输出“1”,否则编码输出“0”。编码输入三连码检测模块进行三连电平的判决,通过量阶调整模块和预测值产生模块产生动态的量阶和预测值。其中预测值产生模块需要注意防止数据溢出。

CVSD解码器负责处理32 kHz的单比特符号,根据图2,编码过程中预测值的产生模块就已经实现了译码过程,后面数字低通FIR滤波器采用分布式算法(Distributed Arithmetic,DA)进行设计,极大地提高了乘累加运算的效能且节省了FPGA的硬件资源。解码器还需要设计一个时钟产生模块,因为采用分布式算法的14阶的低通滤波器的时钟频率是数据时钟的16倍。

4 、仿真测试

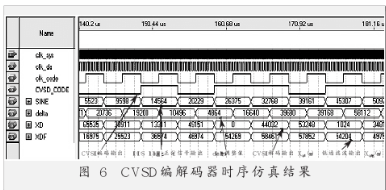

采用Quartus Ⅱ6.0进行开发仿真,verilog语言编程。为了便于软件仿真,设计了DDS信号源,CVSD编码器的输入由正弦信号源DDS模块提供。仿真结果如图6所示。

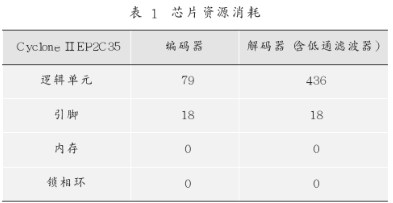

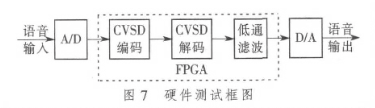

最后在Altera DE2开发板上进行了硬件测试,芯片为Cyclone II EP2C35,编解码器硬件资源消耗见表1。A/D输入模拟的语音信号,采样频率32 kHz,采样信号经编码器、解码器、低通滤波再通过D/A转换输出解码的语音信号,如图7所示。测试结果表明输出语音信号理想,说明设计是可行的。

5、 结束语

CVSD是一种自适应增量脉冲编码调制,对误码有很强的鲁棒性,擅长处理丢失和被损坏的语音采样,编码器是单比特编码,和PCM相比不需要复杂的成帧设备,并且解码器中集成了数字低通滤波器,使得编解码设备简单,综合这些优越性,CVSD特别适合应用于无线语音通信系统,具有很广阔的应用前景。

责任编辑:gt

-

探究SoundStream神经音频编解码器2021-09-23 3757

-

如何控制曼彻斯特编解码器?2021-05-07 2023

-

如何去设计ADPCM语音编解码电路?2021-05-06 1152

-

语音编码和解码免费Speex音频编解码器的微控制器2020-05-29 2523

-

编解码器的工作原理是什么?2020-04-06 3225

-

新唐科技语音频段编解码器简介2019-11-18 2910

-

视频编解码器是什么,编解码器技术原理作用2019-06-24 14891

-

一种高速卷积编解码器的FPGA实现2017-02-07 922

-

音频编解码器技术2012-02-03 5509

-

基于FPGA的曼彻斯特编解码器设计2011-12-28 1206

-

高速并行RS编解码器2010-12-22 927

-

基于FPGA的32Kbit/s CVSD语音编解码器的实现2010-01-12 1185

-

G.726语音编解码器在SoPC中的实现2009-11-30 659

-

什么是音频编解码器?2009-05-03 4274

全部0条评论

快来发表一下你的评论吧 !