基于FPGA XC3S400芯片和ARM相结合实现数据采集系统的设计

可编程逻辑

描述

1、引言

数据采集在工业测控领域里有广泛的应用,它已成为计算机测控系统的一个重要的环节,尤其在设备故障监测系统中,由于各种设备的结构复杂,运动形式多种多样,发生故障的可能部位很难确定,因此我们需要从设备的各个部位来提取大量的、连续的数据作为设备状态的信息,以此来分析、判断设备是否存在故障,这就需要高速、高性能的数据采集系统来保证采集到的数据的实时性;同时,我们需要对同一设备的不同位置的信号进行同步采集,并借助一些手段来提取特征(例如绘制轴心轨迹图)以判断设备的运行状态。传统的数据采集系统设计中,通常采用单片机或DSP作为主控制器来控制ADC、存储器及其他相关的外围电路来工作。但是这些传统的设计中都存在着一些不足,单片机的时钟频率较低且通过软件编程来实现数据采集,难以实现高速、高性能、多通道数据采集系统的要求;DSP虽然速度快,但是它更擅长处理复杂的数学运算,对于数采系统要求的简单高速的读写操作来说,是一种资源的浪费 。而FPGA(现场可编程门阵列)在高速数据采集上具有更大的优点,FPGA体积小、功耗低、时钟频率高、内部延时小、全部控制逻辑由硬件完成,另外编程配置灵活、开发周期短、利用硬件描述语言来编程,可实现程序的并行执行、这将会大大提高系统的性能。

2、系统总体方案

在往复式压缩机状态在线监测系统中,由于压缩机结构复杂、零部件多、运动形式各不相同,发生的故障也就会多种多样,因此需要对各个部件的多个测点的模拟信号进行实时数据采集,同时还要对一些测点周围不同的位置的信号进行同步采集,这就对信号采集的同步性有严格的要求。

多通道的数据采集形式有以下几种:

①各通道模拟信号分别通过信号调理电路后,由多路开关选择后送入1片高速AD转换器件,多路选择开关的切换由硬件或软件控制,从而达到分别转换各通道采来的数据。这种方案所需器件少、硬件电路简单、系统结构小型化,但使用多路开关会带来一系列的信号失真问题,且不能实现信号的真实同步采集,这些问题对AD器件和多路开关都提出了较高的要求。

②各通道模拟信号分别通过信号调理电路后,送入各自对应的AD器件,由系统软、硬件控制各AD的同步采集。采用多片无差别AD芯片来实现各通道采样,与常用的模拟多路开关加单片高速AD芯片,保证了信号采集的同步性和实时性,避免了使用多路开关带来的一系列问题如通道切换过程中尖峰电压的处理、开关导通电阻的影响以及高频采样时噪声的抑制等。

针对往复式压缩机在线监测系统对多路模拟信号采集的实时性和同步性的要求,提出了一种基于FPGA的多通道数据采集的新方案,采用FPGA+ARM相结合的设计,采集主控制逻辑用FPGA来实现,ARM则用来实现采集数据的网络传输控制。本方案中,FPGA向需要同步采样的通道对应的AD芯片提供统一的时钟,使得AD同步地选择相应的通道进行数据的同步采样和转换,其结果由FPGA同步地接收并存储在外部双口RAM对应的存储空间,然后由ARM从相应的双口RAM空间读取数据,并经过网络传输给上位机进行处理。其数据采集系统总体设计如图1所示。

该方案将16路信号分为4组,分别对应4块相同的小电路板,每块小电路板采用4片AD,分别由FPGA控制完成4路信号的采集、转换。4块小电路板最终插在一块大的主电路板上,这样可实现系统小型化的要求。系统外形结构如图2所示,图中标号1、2、3、4分别对应四块小的电路板。

3、 系统主要器件的选型

3.1 FPGA芯片的选型及依据

由于本系统采集通道数较多,实时性和同步性要求较高,要求提供的时钟频率高,内部延时小,因此系统选择Xilinx公司的Spartan3系列XC3S400作为主控制芯片,该芯片具有40万系统门、8064个逻辑单元内嵌18K位块RAM,包含4个时钟管理模块和8个全局时钟网络,最大支持264个用户I/O。这些丰富的片上资源在加上其灵活的编程方式使得该芯片成为最适合的选择。

3.2 AD芯片的选型及依据

在本方案中,考虑到系统的分辨率、通道数、采样率以及接口等要求,本系统AD芯片选用TI公司的ADS8321[3]。ADS8321是TI公司生产的逐次逼近式串行16位微功耗高速A/D转换器,采样频率最高可达100kHz,具有较小的线性度、较低的噪声和功耗,ADS8321具有同步串行SPI/SSI接口,采用这种串行接口输出数据减小了芯片的体积。

4、 FPGA的逻辑设计

4.1 FPGA的逻辑设计思想

本方案中,系统初始化后,首先上位机将采集的参数信息(采样长度、采样频率、采样方式、通道选择、增益倍数等等)传送给ARM主控制器,ARM将这些参数信息存入外部的双口RAM中,然后FPGA再按照RAM里的采集参数信息控制执行,完成采集任务,当采集完成后,FPGA将采集到的数据同步地传送到双口RAM对应的存储空间,供ARM来读取,然后ARM在将读到的数据传送给上位机。

4.2 FPGA模块划分

根据以上的设计思想,整个FPGA逻辑模块划分为:时钟逻辑模块、采样控制模块、串并转换模块、通道选择模块、存储控制模块、接口控制模块。下面具体给出各模块的设计过程。

①时钟逻辑模块。该设计中,外部输入的时钟为50MHz,由于设计中需要多种不同的时钟信号,所以必须设计一个可根据采集需要任意分频的时钟逻辑模块,且必须准确,才能保证整个系统的正常工作。同时该设计采用同步时序电路,它是基于时钟触发沿设计,对时钟的周期、占空比、延时、抖动提出了更高的要求,为此本设计中采用FPGA所带的DCM时钟资源驱动设计的主时钟,已达到最低的时钟抖动和延迟。

②采样控制模块。该模块主要负责控制数据采样和AD转换等,在采样时刻到来时,根据ADS8321芯片的工作特性,在CS信号的控制下,芯片便按照时序进行采样、转换,对于ADS8321要注意当16位转换结果输出完毕后,置位CS或去掉 DCLOCK脉冲,使结果仅输出一次,否则在Dout端会继续输出转换结果,但此时是反过来由最低位到最高位依次输出,直到最高位输出出现重复时,Dout端变成高阻态。

③串并转换模块。由于ADS8321时以串行输出转换结果的,故需要该模块来将串行输出的数据转换为并行输出,该模块主要采用移位寄存器来实现。

④通道选择模块。该模块用来选择需要采样的通道,当ARM主控制器将上位机传来的通道选择控制字写入双口RAM时,通道选择模块根据该信息来进行通道的选择,同时,当数据采集完毕后,该模块还为存储控制模块提供相应的地址信号,以便将对应通道采集来的数据存入对应的空间

⑤存储控制模块。双口RAM用于数据缓存,一是存储各AD芯片转换的数据,二是存储ARM主控制器传来的采集参数信息。它具有真正的双端口,可以同时对其进行数据存取,两端口具有独立的控制线、地址线和数据线。该模块就是根据双口RAM读写时序实现对双口RAM的读写操作,已达到缓存数据的目的。

⑥接口控制模块。该模块为ARM向FPGA及其双口RAM进行交互提供桥梁。当ARM向双口RAM写入采集参数信息时,接口模块要将该信息通知采样控制模块;当ARM读取双口RAM中的数据时,接口模块对ARM的访问地址进行译码,选中对应的存储空间,取出数据。

4.3软件实现

本设计采用自顶向下的设计方法,采用VHDL来分别设计顶层模块和各底层模块,该语言支持自顶向下和基于库的设计方法,并且电路仿真和验证机制以保证设计的正确性。下面以采样控制模块为例来说明其控制算法。

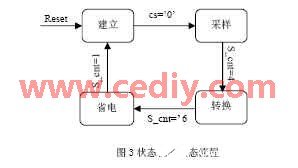

状态机是FPGA内部的指挥单元,它按照固定的节拍往复的运行,本采样控制模块利用状态机来设计,根据ADS8321的工作时序,将状态机分为4个状态周期,分别是建立周期、采样周期、转换周期、省电模式周期,其状态流程如图3所示。

5 、结束语

本文作者创新点是采用FPGA和ARM相结合的设计方法完成高速、多通道、实时的数据采集以及数据的网络传输并采用VHDL编程来实现FPGA各逻辑模块的功能。本设计已通过Modelsim进行的功能仿真和时序仿真,并在Xilinx提供的ISE集成的环境下进行编译、综合、优化、布局布线,并成功的下载到FPGA芯片中。通过对实际信号的采集、测试,系统工作正常,验证了设计结构的合理性,因此是一种比较理想的数据采集方案。

责任编辑:gt

-

如何利用FPGA实现高速连续数据采集系统设计?2021-04-08 2411

-

基于FPGA的高速数据采集系统该怎么设计?2019-09-05 2361

-

如何使用USB2.0和DDR2进行数据采集系统设计与FPGA实现资料概述2018-12-07 2318

-

基于FPGA+AD7609的数据采集系统实现2018-08-09 7653

-

基于FPGA与SRAM数据采集系统设计2018-05-09 3147

-

基于XC3S400和CY7C68013多路数据采集电路的设计2017-11-18 3399

-

【NanoPi2申请】fpga与嵌入式相结合的多媒体数据采集系统2015-12-02 1978

-

谁会spartan3 xc3s400啊!加急!2012-06-14 2657

-

一种新的基于ARM的数据采集系统设计2012-05-22 975

-

XC3S400红色飓风开发板原理图_电路图2012-04-19 5761

-

基于ARM+FPGA的高速同步数据采集2010-08-31 3967

-

基于ARM的蓝牙实时数据采集系统的设计2010-02-02 1438

-

ARM7与FPGA相结合的应用2008-06-17 4819

全部0条评论

快来发表一下你的评论吧 !