关于数字电路的七大知识点

电子说

描述

题目:数制转换

R进制数转换为十进制数:按权展开,相加

十进制数转化为R进制数:整数部分,除R取余法,除到商为0为止。小数部分,乘R取整法,乘到积为0为止。

二进制数转化八进制数:三位一组,整数部分左边补0,小数部分右边补0。反之亦然。

二进制数转化十六进制数:四位一组,整数部分左边补0,小数部分右边补0。反之亦然。

题目:逻辑函数及其化简

公式法

卡诺图法

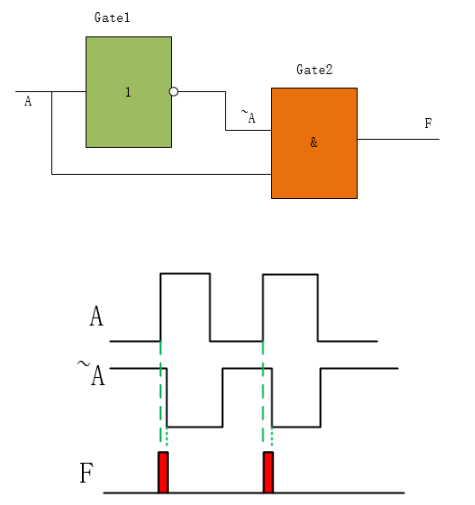

题目:什么是冒险和竞争,如何消除?

下面这个电路,使用了两个逻辑门,一个非门和一个与门,本来在理想情况下F的输出应该是一直稳定的0输出,但是实际上每个门电路从输入到输出是一定会有时间延迟的,这个时间通常叫做电路的开关延迟。而且制作工艺、门的种类甚至制造时微小的工艺偏差,都会引起这个开关延迟时间的变化。

实际上如果算上逻辑门的延迟的话,那么F最后就会产生毛刺。信号由于经由不同路径传输达到某一汇合点的时间有先有后的现象,就称之为竞争,由于竞争现象所引起的电路输出发生瞬间错误的现象,就称之为冒险,FPGA设计中最简单的避免方法是尽量使用时序逻辑同步输入输出。

加滤波电容,消除毛刺的影响

加选通信号,避开毛刺

增加冗余项,消除逻辑冒险。

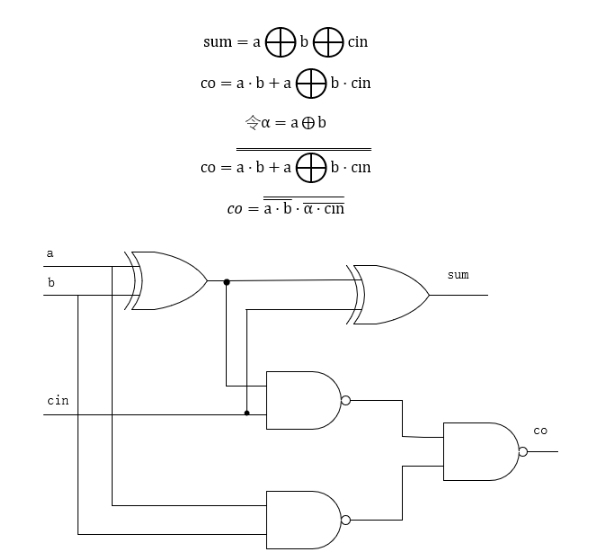

题目:用与非门等设计一个全加法器

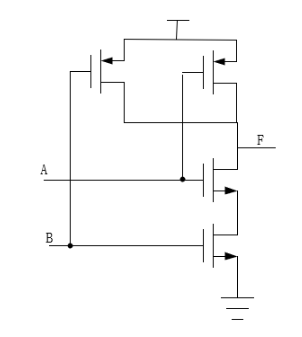

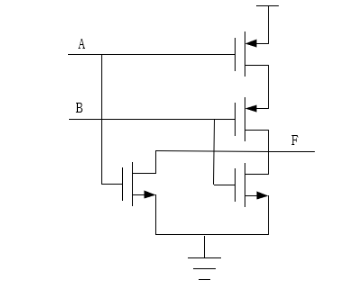

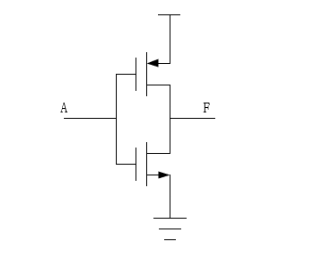

题目:MOS逻辑门

与非门:上并下串(上为PMOS,下为NMOS)

或非门:上串下并(上为PMOS,下为NMOS)

反相器(上为PMOS,下为NMOS)

练习:画出Y = A·B + C的CMOS电路图

Y = (A·B + C)” = ((A·B)’·C’)’,一个反相器,两个而输入与非门。

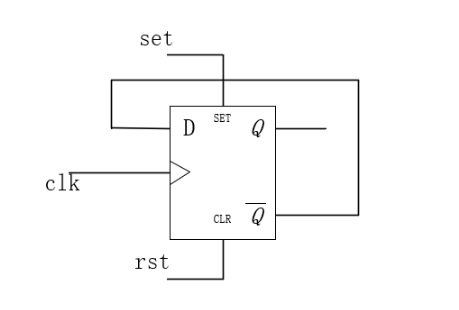

题目:用D触发器带同步高置数和异步高复位端的二分频的电路,画出逻辑电路,Verilog描述。

reg Q;

always @(posedge clk or posedge rst)begin

if(rst == 1‘b1)

Q 《= 1’b0;

else if(set == 1‘b1)

Q 《= 1’b1;

else

Q 《= ~Q;

end

题目:ASIC中低功耗的设计方法和思路(不适用于FPGA)

合理规划芯片的工作模式,通过功耗管理模块控制芯片各模块的Clock,Reset起到控制功耗的目的。

门控时钟(Clockgateing):有效降低动态功耗

多电压供电:通过控制模块的电压来降低功耗

多阈值电压

-

【精选】数字电路知识点总结(东南大学精华版)2021-03-02 1615

-

求大佬分享关于TSMC 0.18um dc数字单元的知识点2021-06-21 1448

-

关于RTC时钟的知识点2021-08-11 2051

-

关于HIP4082电机驱动电路的知识点看完就懂了2021-09-29 4637

-

关于AUTOSAR架构的知识点看完你就懂了2021-10-18 2267

-

关于红外通信的一些问题知识点2016-05-05 1065

-

关于信号完整性的31个知识点汇总2018-06-05 1424

-

数据库设计的七大知识点总结详细资料免费下载2018-10-19 1758

-

数字电子技术重要知识点汇总2022-07-06 1344

-

数字信号处理知识点总结2022-08-15 953

-

数字电路基础知识2022-11-15 2069

-

高速电路设计常见的知识点2023-02-13 2366

-

数字电路基础知识分享12023-05-04 2074

-

数字电路知识点总结2023-05-30 7075

-

数字电位计知识点2023-11-24 618

全部0条评论

快来发表一下你的评论吧 !