基于VHDL语言及SOPC技术实现全数字调频信号发生器的设计

可编程逻辑

描述

一、概述

在常用的信号源及信号处理设计方案中,RC/LC振荡电路频率调整方便,但是它的工作频率稳定度较低。频率稳定度较低导致系统的工作稳定度降低,使其不适用于对精度要求较高的场合。晶振具有稳定且较高的频率,其频率稳定精度可达到10-6以上,但是它的频率是固定不可调的。晶振不能很方便地产生各种频率可变的信号。晶振加锁相环(PLL)电路可结合晶振频率稳定度高和锁相环频率可调的优点,但是输出频率只能成倍的变换,还是不能解决频率可调的根本问题;频率合成器则通过一排晶体振荡器来产生的各种频率的信号,通过开关进行频率混合实现频率合成,但外围电路复杂,分辨率难以提高。

DDS(Direct Digital Frequency Synthesis)技术的出现无疑为我们提供了一种新的选择。DDS技术采用晶振作为系统的时钟,从而提高了输出频率的稳定性;频率控制字及相位累加器的位数决定了频率分辨率,其计算公式为 △f fclk/2N 。这里fclk为系统时钟频率;N为相位累加器的位数。随N增大使得频率分辨率提高;同时频率控制字的可调整性使得系统输出频率非常容易调整。

在此思想指导下,我们应用ALTERA公司的FPGA器件、QuartusⅡ开发环境和NIOS软核等相关的开发工具,采用VHDL语言及SOPC设计思想,辅以必要的模拟与数字转换电路,构成了一个基于DDS技术的数字调频发生器,该设计解决了输出频率在精确度和可调性之间的矛盾。

二、功能说明

本系统由数字式点频信号发生器、扫频信号源和全数字调频发生器三部分组成。

1、信号发生器

具有产生多种波形(如:正弦波、三角波、锯齿波和方波4种波形)的功能。用键盘输入选择上述波形,并可进行相位连续切换。重复频率可调,且相位连续调整,频率步进间隔可扩,输出波形幅度可调整,并具有实时显示输出波形频率和幅度值的功能。

2、扫频信号发生器

具有输出正弦波扫频信号的功能。用键盘输入编辑生成扫频信号,控制输入上、下限及步进频率,可进行随时暂停,并具有扫频延时回放功能。

3、全数字调频发生器

对采样信号进行全数字调频,可以输出具有原信号信息的调频信号,把输入的模拟信号幅度的变化转化为载波频率的变化,简单的实现全数字调频信号发生器。重复频率可调,且相位连续调频,频率步进间隔可扩。

三、系统构成

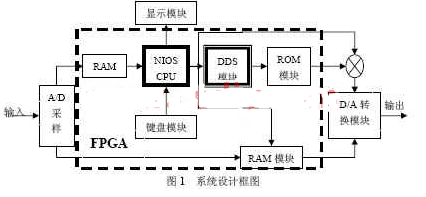

系统设计框图如图1所示:

四、设计描述

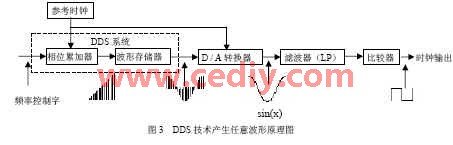

随着电子技术的发展和大规模集成电路制作工艺的提高,DDS(Direct Digital Frequency Synthesis)技术的出现无疑为我们提供了一种选择。但是DDS技术是否适合设计所要求的信号源,而屏蔽掉常规器件的缺点,我们可以通过对DDS技术的简要介绍来解决这个问题。DDS技术产生任意波形原理图如图3所示:

如图所示,DDS系统的参考时钟由晶振产生,输入的频率控制字在参考时钟控制下实现相位累加,截取相位累加器高位产生波形存储器的读数地址。由于波形存储器类似一维向量表,仅需给地址便可取数据。那么将相位累加器输出的相位高位作为输入的地址,波形存储器内部存储的是每一个相位对应的幅度信息。每次访问一个地址,就输出一个幅度值数据。

根据相位与幅度的对应关系获得幅值信息,将幅值信息送往D/A转换器,再经过滤波器即可得到一定频率的输出信号。以固定的速度绕相位环旋转的矢量导致了一个完整周期正弦波的输出。如果向累加器输入的频率控制字改变时,矢量在相位环上的访问速度会相应改变,则输出信号的频率也会改变,即可实现频率可调。

由于兼有这三个方面的优势,DDS技术便成为本次系统设计中信号产生部分的首选。

在本设计作品的实际过程中,我利用ALTERA提供的QuartusⅡ及NIOS在实际的硬件实现上做到高速无缝连接,并利用SOPC设计理念将PLD的最高度设计抽象,弥补了软件和硬件同时集成的空白,由于SOPC Builder是把所有和处理器子系统相关的底层详细资料集中到单个工具中,它具有直观的图形用户接口及自动完成系统集成工作,可直观地连接总线体系,分配从设备端的仲裁优先级,这样就极大的方便了我们的软硬件协同设计工作。

整个系统分为硬件和软件两个部分。

硬件部分包括:A/D转换模块、键盘显示模块和D/A转换模块,其中键盘显示模块采用开发板上所提供的四个按键、两个七段数码管、LED和LCD液晶显示、A/D、D/A、DDS、RAM、ROM模块;

软件部分包括对键盘显示及整个系统联调的NIOS控制编程。

一、 硬件部分

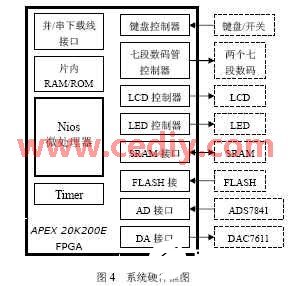

系统硬件框图如图4所示:

1、 键盘显示模块:

键盘模块包括八键开关和四个按键。四个按键中功能分别为:功能切换键,加键,减键和确认键。

显示模块主要由七段数码管、LED和LCD三部分组成。其中七段数码管用于功能识别显示,LED用于确认键识别,而主要的详细数据及模式信息由LCD显示实现。

2、 A/D、D/A转换模块:

A/D模块所用器件是ADS7841,它是一个4通道、12位采样的模拟/数字转换器。D/A转换模块所用器件为DAC7611,它是工作在工业温度范围内的12位数字/模拟转换器。

一帧12位数据完成D/A转换需要12个CLK,而这12个CLK是由系统时钟30分频产生。系统时钟为33.333MHz,经30分频后所得的D/A转换速率应为33.333MHz /30=1.1111 MHz。而访问ROM表的时钟频率应与D/A转换速率同步,所以输出波形的频率受到D/A转换器的限制。如果一个周期访问8个数值,则输出模拟信号的频率最高为1.1111 MHz /8=138887.5Hz,这是理论上的最大频率值。如果采用高速并行D/A转换器,转换速率会大幅提高。而本次设计采用串行D/A转换器的主要原因是因为其能应用于远程串行通信系统。

3、DDS模块:

(1)、相位累加器:相位累加器是DDS的核心部分,用于完成频率控制字的相位累加,随频率控制字的改变进而实现调频的功能。该功能用VHDL硬件描述语言编程实现

(2)、幅度调制:由ROM查表输出的结果(10位)与幅度控制字(2位)通过一级乘法器实现,乘法器利用开发平台内部的快速定制功能对生成的乘法器进行定制。并附加一级锁存单元可以等到波形数据稳定后再向后级电路传送,这样就避免了毛刺的产生。

4、ROM、RAM存储器模块:

ROM存储器实现任意波形数据的存储,根据地址值从ROM表中查找出对应的数据,并将查表所得数据输出到数字/模拟转换模块。存储器不仅要有程序来对它进行控制,更为关键的是在其中存储一个、二分之一或四分之一波形的数据。

RAM模块用于信号的采集处理过程中,A/D转换器完成对输入模拟信号256个点的采样,从A/D转换器输出的采样数据个数为256个,所以RAM的地址位数应为8位

软件部分

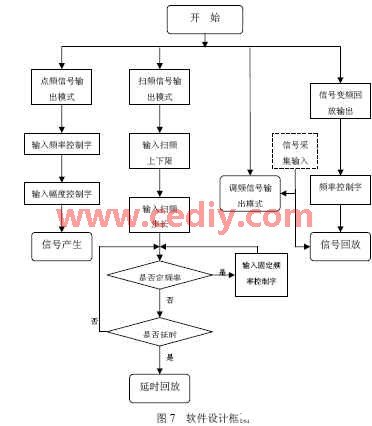

设计框图如图7所示:

1、 键盘显示控制模块:

利用NIOS实现键盘的过程中,由于设计板所提供的仅有四个的按键及八个开关。基本上,键盘显示的控制部分均由PIO赋值及利用其固有的宏命令编制C语言加以实现。

2、 整个系统联调的NIOS控制编程:

编制C程序实现键盘显示模块、DDS模块及A/D、D/A转换模块的控制,其中大量采用了PIO赋值并利用条件语句进行判断状态,PIO送入不同的相应输入字。

五、系统特点

根据实际测量指标,在频率无论是低频还是高频都具有很好的频率调整精度。其相对误差的数学期望都在10-7数量级上,完全可以达到我们的信号发生器的功能指标,同时这样的产品精度也是市场上类似产品所不能比拟的。由于对于晶振而言,其精度也就是10-7,由此,我们设计实现的信号源精度已经达到了针对晶振的精度极限。

在具体的设计实现过程中,我们强调抓住每个具体细节的稳定性。如在硬件乘法器方面,我们都在其后端加入了锁存单元,利用边缘触发防止不定或过多毛刺的产生,从而实现了近乎理想的基于DDS理论的信号产生与处理功能。

六、总结

引入SOPC的设计理念,无疑就是一场IC革命的必然延续。就我们的设计而言,对基于SOPC理念的NIOS系统设计从掌握到充分的运用到实际设计过程中,大概不超过半个月的时间,这点就充分地体现了它的短开发周期优势。

其次,对NIOS而言它是一种软核处理器,因此其硬件可任意添加删除,从而提高了整个系统的运行效果也降低了设计成本。同时对设计人员的技术要求可以大大降低。

再者,在我们的实际设计过程中由于需要大量的乘除运算,无疑利用类似于NIOS的微处理器很容易实现,可避免完全利用硬件描述语言编写所出现的大量毛刺及工作量。

本文作者创新点:能够利用FPGA器件参考DDS理论配合Nios软核微处理器技术,设计实现多种波形数字幅度频率可调的精确调频发生器。该技术的创新点在于输出的调频信号频率从0.0Hz—138887.5000Hz,最小步进可达到为0.0001Hz。在我们对频率的测试结果中,无论是低频还是高频都具有很好的频率调整精度。其相对误差的数学期望都在10-7数量级上。因此就信号的频率精度可靠性而言,与技术相比具有一定的优势。

责任编辑:gt

-

E4437B AgilentE4437B高频信号发生器Agilent E4437B高频信号发生器2018-11-08 1318

-

使用Keysight ESG-D系列实时I/Q基带发生器定制数字调制2019-05-30 1972

-

调频信号发生器的工作原理是什么?2019-10-10 1618

-

怎么实现基于DSP和SOPC数字信号发生器的设计?2021-05-12 1167

-

VHDL语言及其应用 pdf2009-02-12 1035

-

低频信号发生器的使用2009-03-08 8082

-

VHDL语言及其应用2009-07-10 556

-

基于DSP和SOPC数字信号发生器的设计2009-10-22 877

-

调频信号发生器原理及制作2010-05-17 6433

-

用CD4046组成的调频信号发生器2011-06-01 5155

-

基于CD4046的调频信号发生器电路图2012-05-28 7625

-

基于FPGA和DDS的数字调制信号发生器设计2013-04-27 1537

-

比较几种微波信号发生器有什么不同2022-03-18 5257

-

如何选择合适的射频信号发生器2022-04-20 4848

-

低频信号发生器如何调节电压?2024-04-26 1429

全部0条评论

快来发表一下你的评论吧 !