基于FPGA和单片机构成的电子加密系统的设计

可编程逻辑

描述

1、 引言

FPGA/CPLD技术是近年来计算机与电子技术领域的又一场新的革命,为了保护知识产权,出现了各种层次的针对FPGA的安全加密技术。常用的方法有:硬件加密法,软件加密法,可重构加密法等。然而在传统的许多加密技术中,人们通常能够通过对代码的跟踪、分析和PCB板的复制,而实现硬件和软件的非法拷贝。为了进一步提高数字系统的安全性,本文论述了一种基于SHA加密算法的,采用FPGA和DS2432实现的硬件加密技术。不但实现简单而且可有效降低硬件仿制的可能性。

2、 IFF的概念

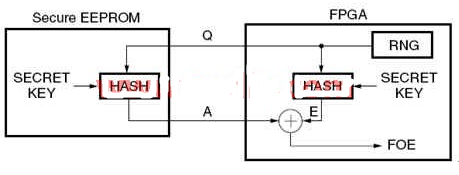

IFF(Identification Friend or Foe)的字面含义为身份鉴别,等效电路如图1所示:

图1 身份鉴别等效电路

在FPGA正式工作前,首先要完成与加密芯片的指令问答,共分如下几步:

(1)FPGA执行随机数产生器(RNG),产生一个随即数Q,并把它送往安全EEPROM中。

(2)安全EEPROM利用仅对设计者开放的密钥,使用HASH函数,进行安全散列算法,对Q进行加密,产生一个信息A。

(3)FPGA使用相同的密钥产生期望的信息E,与来自安全EEPROM的实际信息A进行比较。

(4)如果期望的信息E和实际的信息A相同,则表明这个设计是一个Friend,否则这个设计是一个 Foe,因为这个系统的非法拷贝可能已经发生。

(5)最后,FPGA必须按以下方式进行设计:如果Foe被检测到,系统停止运行,或者以减少的功能运行,只有系统被检测为Friend时,用户设计的功能才能正常的运行。

3、SHA-1算法

SHA-1算法即是安全散列算法,该算法采用十六个32位字 (0≤t≤15)作为输入数据,可用于计算读验证页命令,这十六个32位字来自于密钥、存储器等相关数据以一定的函数关系生成。SHA算法还涉及到一个称为 (0≤t≤79)的八十个32位字的序列,一个称为Kt (0≤t≤79)的八十个32位字的序列,一个布尔函数ft (B,C,D) (0≤t≤79),其中B、C和D为32位字,以及另外三个32位字,称为A,E和TEMP。它们的定义如下:

函数ft (B,C,D) = (B∧C)∨((B\)∧D) (0≤t≤19)

B C D (0≤t≤39)

(B∧C)∨(B∧D)∨(C∧D) (40≤t≤59)

B C D (0≤t≤79)

序列 =  (0≤t≤15)

(0≤t≤15)

(16≤t≤79)

序列Kt = 5A827999h (0≤t≤19)

6ED9EBA1h (20≤t≤39)

8F1BBCDCh (40≤t≤59)

CA62C1D6h (60≤t≤79)

变量A、B、C、D、E初始化如下:

A = 67452301h

B = EFCDAB89h

C = 98BADCFEh

D = 10325476h

E = C3D2E1F0h

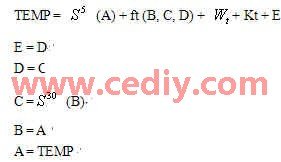

当t从0循环至79,执行了下面的的一系列计算后,160位的MAC是A、B、C、D和E的串联(不考虑任何进位):

主机通过读验证页命令读取MAC,与主机本身计算的MAC值进行比较,以判断是否有非法拷贝产生。

4、DS2432的硬件配置和功能描述

DS2432是一个具有SHA-1引擎、支持1-wire总线的EEPROM存储器,主要用于数字系统的加密、计数等。

(1)硬件配置

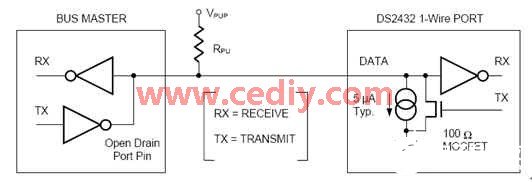

DS2432与外界通过1-wire端口进行通信,其内部等效电路如图2所示:

图2 硬件配置及内部等效电路

由于1-Wire总线只定义了一条数据线,所以,保证在适当的时间驱动总线上的每个器件非常重要,为了达到这一目的,接在1-Wire总线上的每个器件都必须漏极开路和三态输出。具体内容可参阅DS2432的数据手册。

(2)功能描述

DS2432有五个主要的数据部件:1)64位光刻ROM,2)64位暂存器,3)四个32字节的EEPROM页,4)64位寄存器,5)64位密钥存储器和一个512位的SHA-1(安全散列算法)引擎。DS2432根据自己的密钥、指定存储器页的所有数据、自身的注册码和一个3个字节的质询码来计算MAC,主机通过读验证页命令可以获得全部或部分存储器页的数据和一个MAC。利用MAC,主机能够判定存储在DS2432中的密钥是否对某个特定的功能有效。

5、DS2432在Xilinx FPGA 中的应用

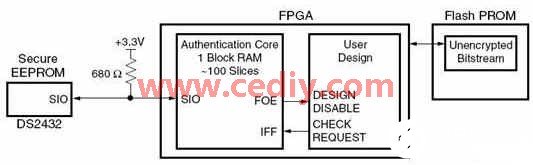

把IFF概念应用于DS2432的安全EEPROM中,一种高级别的安全加密方法便获得了实际的应用,如图3所示:

图3 DS2432在系统中的实际应用

DS2432安全EEPROM与一个Xilinx FPGA之间的连接框图勾画了这种加密技术的思维方法。首先,FPGA从flash ROM中读取程序进行自我配置,当配置完成后,用户设计自动的处于禁止状态。然后,FPGA通过1-wire总线送给DS2432三个字节的随机质询码,并读取DS2432内部存储器的相关数据,DS2432和FPGA共同使用一个只有设计者本人知道的64位密钥,结合相关数据,利用SHA-1算法,分别计算出各自的MAC值。最后,FPGA从DS2432中读取MAC与自己计算的MAC进行比较来判断通信是否成功。

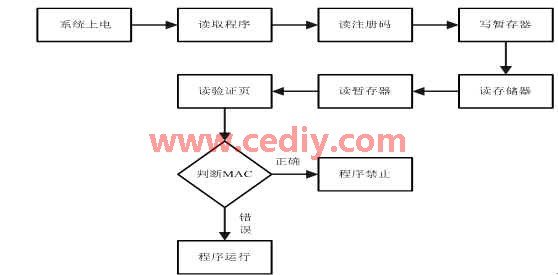

其工作流程如图4所示:

图4 系统身份验证工作流程

由于质询码是由FPGA随机产生的,通信是否成功的判断在FPGA的内部进行,使得系统具有较高的抗追踪性,也使一些使用复制DS2432来破解系统失去了理论上的可操作性。

6、结束语

利用FPGA内部的数据加密内核,使FPGA完成与DS2432通信后的判断在FPGA内部进行,这样就避免了在一些小的系统设计中通过破译程序的机器码而获得程序的解密。并且,由于从FPGA配置信息中获取相应的硬件描述语言代码是非常困难的事情,因此在一个由FPGA和单片机构成的电子系统中,这样的加密方法具有重要的意义和使用价值。

本文的创新点:利用FPGA内部的数据加密内核和由其产生的随机质询码,通过SHA-1算法计算出相应的MAC值,并且在FPGA内部完成指令问答的过程,有效降低了硬件仿制的可能性。

责任编辑:gt

-

单片机构成高精度PWM式12位D-A转换器2016-06-25 4164

-

单片机是如何构成的?2021-03-11 1831

-

如何用单片机实现SRAM工艺FPGA的加密应用?2021-04-08 2890

-

单片机加密方法2006-03-22 1203

-

用单片机实现SRAM工艺FPGA的加密应用2009-04-16 768

-

用51 内核网络单片机构成的远程监控系统2009-05-18 558

-

基于单片机和FPGA的网络数据加密2010-12-24 1005

-

一种基于SRAM的FPGA的加密方法2011-03-16 837

-

用单片机构成的波形发生器电路2011-10-08 1339

-

PIC16F628单片机构成PVS控制系统2012-03-26 3950

-

由可编程逻辑器件与单片机构成的双控制器2017-01-12 886

-

FPGA与单片机实现数据串行通信的解决方案2017-02-11 11861

-

sim900+51单片机构成的系统(包含原理图和PCB)2017-02-27 1635

-

单片机的攻克与加密2017-11-06 710

-

基于单片机和FPGA的网络数据加密实现2023-10-18 419

全部0条评论

快来发表一下你的评论吧 !