德州仪器:GaN器件的直接驱动配置

电源设计应用

描述

Paul L. Brohlin设计和系统经理;Yogesh K. Ramadass模拟设计经理;Cetin Kaya设计工程师

受益于集成器件保护,直接驱动GaN器件可实现更高的开关电源效率和更佳的系统级可靠性。

高电压(600V)氮化镓(GaN)高电子迁移率晶体管(HEMT)的开关特性可实现提高开关模式电源效率和密度的新型拓扑。GaN具有低寄生电容(Ciss、Coss、Crss)和无第三象限反向恢复的特点。这些特性可实现诸如图腾柱无桥功率因数控制器(PFC)等较高频率的硬开关拓扑。由于它们的高开关损耗,MOSFET和绝缘栅双极晶体管(IGBT)实现此类拓扑。本文中,我们将重点介绍直接驱动GaN晶体管的优点,包括更低的开关损耗、更佳的压摆率控制和改进的器件保护。

简介

在设计开关模式电源时,主要品质因数(FOM)包括成本、尺寸和效率。[1]这三个FOM是耦合型,需要考虑诸多因素。例如,增加开关频率可减小磁性元件的尺寸和成本,但会增加磁性元件的损耗和功率器件中的开关损耗。由于GaN的寄生电容低且没有二极管反向恢复,因此与MOSFET和IGBT相比,GaN HEMT具有显著降低损耗的潜力。

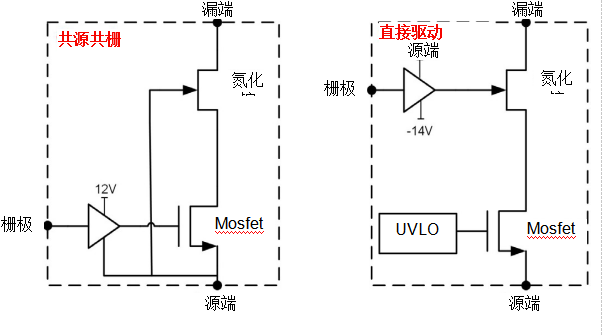

图1:共源共栅驱动和直接驱动配置。 通常来讲,MOSFET/IGBT驱动提供合适的导通和关断电流,以支持输入电容。驱动输出和设备栅极之间的外部电阻控制压摆率,并抑制功率和栅极环路振铃。随着GaN压摆率增加,外部组件增加了过多的寄生电感,无法控制开关。将驱动与GaN器件集成到封装中可最大程度降低寄生电感、降低开关损耗并优化驱动控制。

直接驱动优点

漏端和漏端之间的GaN中存在本征二维电子气层(2-DEG),使该器件在零栅极-漏端电压下导电。出于安全原因,没有偏置电源时,必须关闭开关电源中使用的电源器件,以将输入与输出断开。为模拟增强模式器件,将低压MOSFET与GaN源端串联放置。图1所示为实现此目的的两种不同配置:共源共栅驱动和直接驱动。

现在,我们将对比功耗,并描述与每种方法相关的警告所涉及的问题。

在共源共栅配置中,GaN栅极接地,MOSFET栅极被驱动,以控制GaN器件。由于MOSFET是硅器件,因此许多栅极驱动可用。但由于在GaN器件关闭之前必须将GaN栅极至漏端电容(Cgs)和MOSFET Coss充电至GaN阈值电压,因此该配置具有较高的组合Coss。

在直接驱动配置中,MOSFET是一个直接驱动配置,由栅极驱动器在接地和负电压(VNEG)之间驱动的GaN栅极导通/关断组合器件。此外,MOSFET Coss无需充电。关断GaN Cgs的电流来自较低的偏压电源。较低的电源电压可提供相同的GaN栅极至漏端电荷(Qgs),从而可降低功耗。这些功率效率差异在更高的开关频率下会进一步放大。

反向恢复Qrr损失对于共源共栅配置有效。这是因为在第三象限导通中,MOSFET关断,并通过体二极管导通。

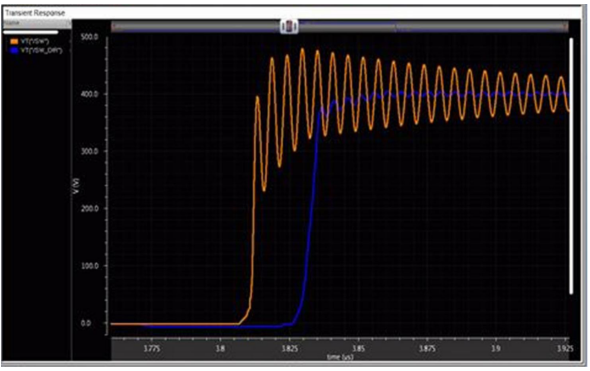

图 2:硬切换操作导致过多振铃。 由于负载电流反向流动,因此MOSFET中存储了电荷。克服反向恢复电荷的电流来自高电压电源,这会导致大量电损失。但在直接驱动配置中,MOSFET始终处于导通状态,且由于其RDSON低,其寄生二极管也不会导通。因此,最终在直接驱动配置中不会出现与Qrr相关的功率损耗。

在共源共栅配置中,由于GaN漏源电容高(Cds)[2,3],处于关断模式的GaN和MOSFET之间的电压分布会导致MOSFET雪崩。可在MOSFET的漏端和漏端之间并联一个电容器[4]予以解决。但这仅适用于软开关应用,并在硬开关应用中导致高功率损耗。

鉴于GaN栅极已连至MOSFET的漏端,因此无法控制共源共栅驱动中的开关压摆率。在硬开关操作中,来自GaN Cgs、MOSFET Coss、MOSFET Qrr的有效Coss的增加,以及由于防止MOSFET崩溃而可能产生的一些电流导通,可能会在初始充电期间导致较高的漏端电流。较高的漏端电流会导致共源共栅驱动中的较高功率损耗。

在MOSFET的漏端充电至足以关闭GaN器件的程度后,从漏端观察到Coss突然下降——加上流经功率环路电感的漏端电流较高——导致共源共栅中开关节点的过度振铃组态。硬开关事件期间的开关波形如图2所示(橙色轨线=共源共栅驱动;蓝色迹线=直接驱动)。在此模拟中,即使直接驱动配置的压摆率较低且振铃较少(直接驱动在50 V/ns时为4.2 W,而共源共栅驱动在150 V/ns时为4.6 W,所有负载电流均为5A),直接驱动配置每次硬开关耗散的能量却更少。

另一方面,直接驱动配置在开关操作期间直接驱动GaN器件的栅极。无偏置电源时,MOSFET栅极被拉至接地,并以与共源共栅配置相同的方式关闭GaN器件。一旦存在偏置电源,MOSFET保持导通状态,其寄生电容和体二极管从电路中移出。直接驱动GaN栅极的优点在于可通过设置对GaN栅极充电的电流来控制压摆率。

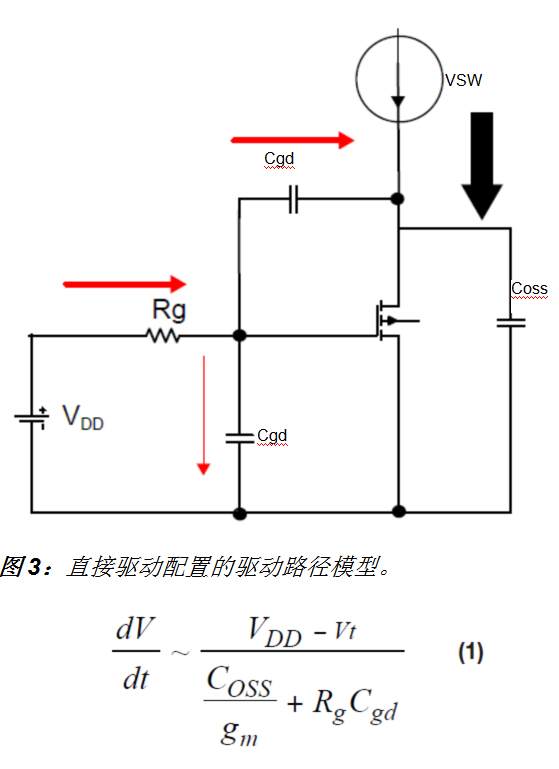

对于升压转换器,驱动电路的简易模型如图3所示。可使用该模型推导公式[1]。

等式1证明:当GaN器件具有足够的栅漏电容(Cgd)时,可通过使用栅极电流通过米勒反馈来控制开关事件的压摆率。对于低Cgd器件,将丢失反馈,且器件的跨导(gm)控制压摆率。 直接驱动配置的另一个优点在于可在栅极环路中增加阻抗,以抑制其寄生谐振。抑制栅极环路还可减少电源环路中的振铃。这降低了GaN器件上的电压应力,并减少了硬开关期间的电磁干扰(EMI)问题。

图2是一个模拟图,显示以功率和栅极环路寄生电感为模型的降压转换器中开关节点振铃的差异。直接驱动配置具有受控的导通,且过冲很少。而共源共栅驱动由于较高的初始Coss、Qrr和较低的栅极环路阻抗而具有较大的振铃和硬开关损耗。

集成栅极驱动的75mΩGaN器件

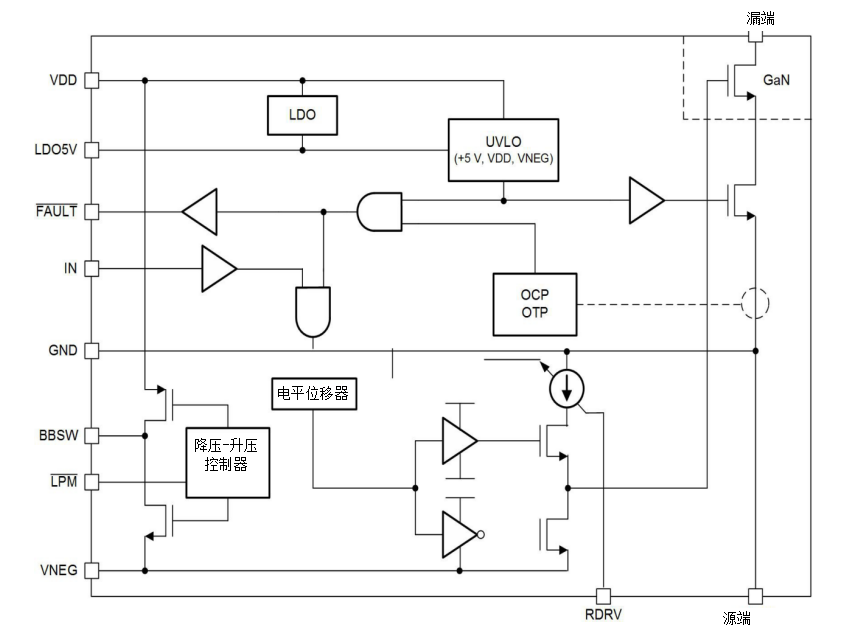

TI的LMG341x系列600V GaN器件是业界首个集成GaN FET外加驱动器和保护功能的器件。它是一个8mm x 8mm四方扁平无引线(QFN)多芯片模块(MCM),包括一个GaN FET和具有集成20V串联FET的驱动。RDSON 的总电阻为75mΩ。

该器件的框图如图4所示。栅极驱动器提供GaN FET的直接驱动能力,并具有内置的降压-升压转换器,以产生关闭GaN FET所需的负电压。栅极驱动使用12V单电源供电,并具有一个内部低压差稳压器(LDO),可产生一个5V电源,为驱动和其他控制电路供电。内部欠压锁定(UVLO)电路使安全FET保持关闭状态,直至输入电压超过9.5V。一旦UVLO超过其自身阈值,降压/升压转换器就会接通并对负电源轨(VNEG)充电。一旦VNEG电源电压超过其自身的UVLO,驱动器便会启用驱动。

与分立的GaN和驱动器相比,LMG341x系列的集成直接驱动实现具有诸多优势。栅极驱动的一个重要方面是在硬开关事件期间控制压摆率。LMG341x系列使用可编程电流源来驱动GaN栅极。

图4:单通道600 V,76ΩGaN FET功率级的框图。

电流源来驱动GaN栅极。电流源提供阻抗以抑制栅极环路,并允许用户以受控的方式对转换率进行编程,转换率从30 V/ns到100 V/ns,以解决电路板寄生和EMI问题。

通过将串联FET集成到驱动集成电路(IC)中,感测FET和电流感测电路可为GaN FET提供过流保护。这是增强整体系统可靠性的关键功能。使用增强型GaN器件时,这种电流检测方案无法实现。当大于40 A的电流流经GaN FET时,电流保护电路会跳闸。GaN FET在发生过流事件后的60 ns内关闭,从而防止裸片过热。

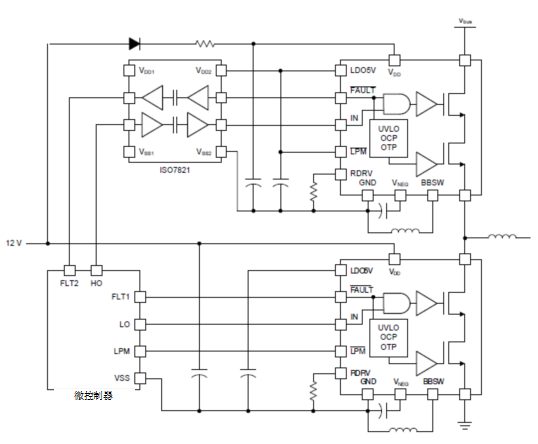

通过将驱动芯片封装在与GaN FET相同的裸片附着垫(DAP)上,驱动芯片处的引线框架可感测GaN器件的温度。驱动可通过在过热事件期间禁用GaN驱动来保护器件。集成的GaN器件还提供FAULT输出,通知控制器由于故障事件而停止了开关。 为使用直接驱动方法验证操作,我们建立了一个半桥板,并将其配置为降压转换器(图5)。此外,我们使用了ISO7831 双向电平位移器来馈送高侧驱动信号,并返回经过电平位移的FAULT信号。

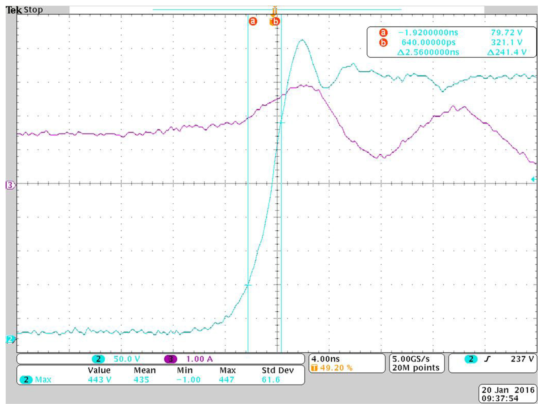

图6中,GaN半桥配置从480V总线、以1.5A的转换速率转换为100V/ns。蓝色迹线是开关节点波形,紫色迹线是电感器电流。

图 5:典型的半桥配置。

硬开关导通稳定,具有约50 V的过冲。此波形使用1 Ghz示波器和探头进行采集,可观察到任何高频振铃。快速的导通时间,外加减小的寄生电容和缺反向恢复电荷,使得基于GaN的半桥配置即使在使用硬开关转换器时也可高效开关。

图 6:降压开关波形示例。

总结

GaN在减小寄生电容和无反向恢复方面所提供的优势为使用硬开关拓扑结构同时保持高效率提供了可能。需要受控的高开关压摆率来更大程度地发挥GaN的优势,而这又需要优化的共封装驱动器和精心的电路板布局技术。 共封装驱动有助于更大程度地减少栅极环路寄生效应,以减少栅极振铃。

利用精心布置的印刷电路板(PCB),优化的驱动器可使设计人员以更小的振铃和EMI来控制开关事件的转换速率。这得益于GaN器件的直接驱动配置而非级联驱动配置。

LMG341x系列器件使设计人员能够以30 V/ns至100 V/ns的压摆率控制各类器件的开关。此外,驱动器还提供过流、过热和欠压保护。

参考文献

1. B.J. Baliga, “Power Semiconductor Device Figure-of-Merit for High Frequency Applications,” IEEE Electron Device Letters, vol. 10, pp. 455-457, 1989.

2. M. Seeman et al., “Advantages of GaN in a High-Voltage Resonant LLC Converter,” IEEE APEC, pp. 476-483, March 2014.

3. S. Bahl et al., “New Electrical Overstress and Energy Loss Mechanism in GaN Cascodes,” APEC 2015.

4. X. Huang et al., “Characterization and Enhancement of 600V Cascode GaN Device,” Virginia Tech 2015 CPES Industry Webinar, March 11, 2015.

5. Download these data sheets: LMG3410R050. LMG3410R070 and LMG3411R070

-

德州仪器部分器件停产通知:设计应对与替代方案2026-04-23 254

-

德州仪器日本会津工厂投产GaN功率半导体2024-10-30 1628

-

德州仪器发布高性能650V GaN IPM,革新电机驱动设计2024-06-18 1719

-

德州仪器发布低功耗氮化镓系列新品2023-12-01 2740

-

德州仪器汽车应用参考设计精选2022-11-07 960

-

德州仪器高性能模拟器件高校应用指南2021-05-31 1880

-

德州仪器转向微型器件的五大理由2019-07-29 2526

-

基于德州仪器GaN产品实现更高功率密度2019-03-01 2791

-

【好书推荐】德州仪器高性能模拟器件在高校中的应用及选型指南2015-07-27 5511

-

德州仪器高性能单片机和模拟器件在高校中的应用-培训2014-03-19 2596

-

德州仪器推荐器件2013-09-03 7321

-

各类NXP FREESCALE,TI(德州仪器)2013-05-11 2691

-

德州仪器(TI)模拟开关资料2012-12-20 5669

-

德州仪器(TI)2011-12-12 2667

全部0条评论

快来发表一下你的评论吧 !