基于DSP的RS232串口连接设计

接口/总线/驱动

描述

本科项目上需要DSP通过RS232串口连接四个设备,可供使用的芯片串口只有一个。

方案一:利用手头器件,简单利用FPGA和max232电平转换芯片采用片选方式设计

verilog代码如下:

module demultiplexer1to4 (out0,out1,out2,out3,in,s2,s1,s0);

output out0,out1,out2,out3;

input in;

input s0,s1,s2 ;

reg out0,out1,out2,out3;

always@(s0 or s1 or s2 or in)

case({s2,s1,s0} )

3‘b001: begin out0 《= in; out1 《= 1’bz; out2 《= 1‘bz; out3 《= 1’bz; end

3‘b011: begin out0 《= 1’bz; out1 《= in; out2 《= 1‘bz; out3 《= 1’bz; end

3‘b010: begin out0 《= 1’bz; out1 《= 1‘bz; out2 《= in; out3 《= 1’bz; end

3‘b110: begin out0 《= 1’bz; out1 《= 1‘bz; out2 《= 1’bz; out3 《= in; end

3‘b111: begin out0 《= in; out1 《= in; out2 《= in; out3 《= in; end

default: begin out0 《= 1’bz; out1 《= 1‘bz; out2 《= 1’bz;out3 《= 1‘bz; end

endcase

endmodule

优势:可实现一对一发送和一对多发送;

缺点:需要器件、接线较多,不可靠。

出现问题:使用一段时间后,数据出现乱码,分析是采用劣质max232芯片所导致,改用网申的美信原装芯片,没有继续出现问题。但劣质max232芯片单独使用电平转换没有问题。

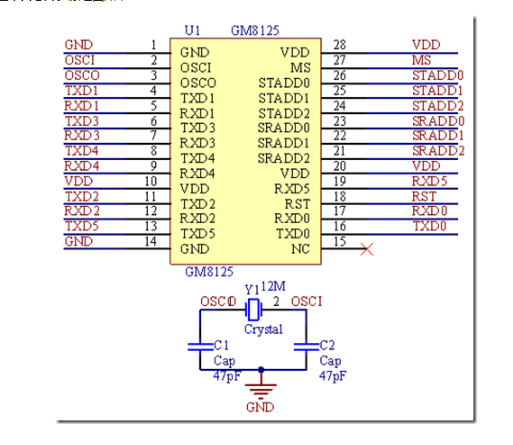

方案二、接着我开始寻找集成芯片用以替代方案一,然后找到了成都国腾微电子有限公司的GM8125一扩五串口芯片。原理图如下:

此芯片缺陷是不能够一对多发送数据,只能一对一,倒也能满足我使用需求。

经过了一个寒假回来,事情变的奇怪了,采用此转换芯片发送的第一组数据出现乱码,后续数据正常。

解决办法,上电后先发送一组无用数据,跳过乱码。当时因为时间关系没有继续查明原因。

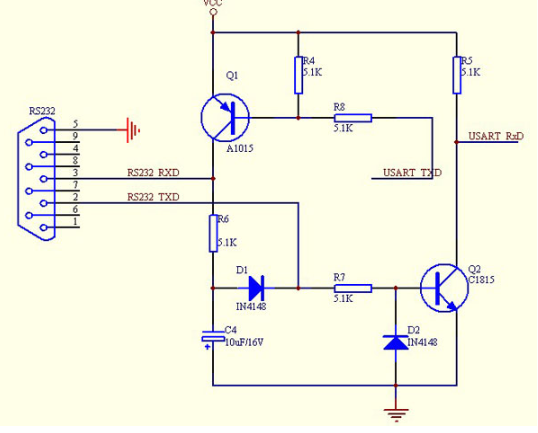

简单自制转换电路(此电路不适用与全双工工作):

RS232高电平: -3~ -15V

RS232低电平: +3~ +15V

RS232传输数据时空闲位为高电平,即-3~ -15V

发送数据时,USART_TXD(TTL或CMOS电平)为高电平,Q1截止,RS232_RXD电平为(0.7V(二极管压降)+RS232_TXD),因RS232_TXD空闲时为高电平,则RS232_RXD也为高电平。

USART_TXD(TTL或CMOS电平)为低电平,Q1导通,RS232_RXD电平近似为VCC,表现在RS232电平上为低电平。

接收数据时,RS232_TXD为高电平,Q2截止,USART_RXD近似为VCC,表现在TTL或CMOS电平上为高电平。

RS232_TXD为低电平,Q2导通,USART_RXD电平接近为0,为低电平。

-

FT232芯片设计的USB转RS232串口原理图2024-10-21 1357

-

rs232接口有啥用?rs232串口接线图 深入理解RS232串口2023-06-01 75934

-

TTL RS232串口通讯模块2022-08-10 2087

-

RS485/RS232串口转Modbus网关2021-12-03 3183

-

RS232串口的缺点有哪些2021-06-08 6388

-

实现RS232串口通信的资料合集2020-07-17 3240

-

天嵌科技TTL转RS232串口-串口模块简介2019-11-11 4638

-

rs232介绍_rs232串口通信程序2018-01-14 12702

-

rs232串口是什么,RS232串口介绍2017-11-01 212144

-

FT232芯片设计的USB转RS232串口线原理图2017-02-28 5272

-

rs232串口通信原理2008-10-14 12121

-

RS232串口通信实验2008-09-22 12551

-

rs232串口通信程序2007-12-25 1434

-

RS232串口电路图2007-06-09 10152

全部0条评论

快来发表一下你的评论吧 !