基于Xilinx XC95144和单片机实现数字频率计的设计

可编程逻辑

描述

一。 引言

数字频率计是电子测试、自动化控制等设备中不可或缺的重要模块,对其精度和成本都提出了较高的要求。最常用和直接的频率测量方法是直接测频法。直接测频法工作原理简单,设计复杂度低。其通过在给定的闸门信号中对待测信号脉冲进行计数,从而算出待测信号的频率。但由于闸门是与基准信号(fr)完全同步,而不是待测信号(ft),所以测量结果有±1个待测信号脉冲的误差,这对低频信号是难以容忍的。多周期同步测频法中闸门的时间不是固定的,而是被测信号的整周期倍。闸门的开闭受门控信号和待测信号的双重控制,以期达到闸门与待测信号完全同步,从而消除±1个待测信号脉冲的误差。多周期同步测频法将误差转移为±1个基准脉冲的误差,而基准信号的频率一般较高,其±1个脉冲误差可忽略不计。多周期同步测频法虽然解决了误差的问题,但其增加了闸门信号的设计难度,而且加重了频率计算部分的负担。

基于此,本文提出了一种采用较小规模CPLD(Xilinx XC95144)和单片机(AT89C51)相结合的数字频率计设计方案。该方案不仅体积小、保密性强,而且设计简单、成本低、精度高、可测频带宽。

二。 数字频率计工作原理

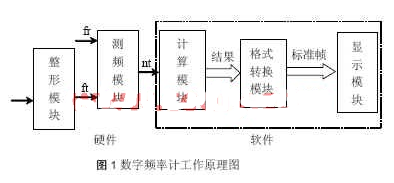

本文提出的基于CPLD和单片机相结合的设计方案不仅能较好地解决误差问题,误差仅小于等于 0.1HZ,同时还通过对软硬件界面的科学划分,在保证性能的基础上,尽最大可能地简化了硬件设计的难度。该方法原理图如图1所示。其中测频模块采用CPLD(Xilinx XC95144)设计完成,其余功能主要由单片机来实现。完成的功能如下:

测频模块:主要是对基准信号fr和待测信号ft的脉冲进行计数,计数周期为1s;

数字处理模块:接收测频模块送出的待测信号脉冲计数值nt,计算出其实际的频率值。然后采用10次求平均的方法逐步求精待测信号频率值;

格式转换模:块负责将计算模块所得的结果转换为显示模块可以识别的帧格式;

整形模块:负责对输入的待测信号进行整形处理(放大、滤波);

显示模块:负责待测信号频率值的显示。

下面将对对其核心模块的设计做一介绍。

三。 数字频率计的设计

3.1 测频模块

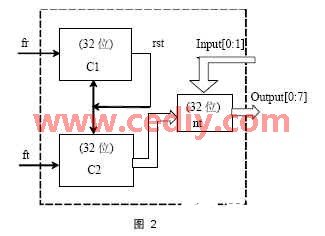

如图2所示,测频模块主要由两个计数器C1和C2组成。其工作过程如下:

C1对基准信号的脉冲进行计数,计数周期为1s;C1计数的同时,C2对待测信号的脉冲进行计数。当C1计数满1s时,门控信号rst有效,其终止C1和 C2的计数,并将C2的计数值锁存至32位寄存器nt中,然后将C1和C2计数值清零;接着rst无效,并开始下一次计数,C1计数不满1s期间rst始终保持无效。

3.2 数据处理模块

数字频率计的核心单元AT89C51,通过控制P3.0和P3.1两个端口将32位寄存器nt的4个字节输出到AT89C51的直接地址30H, 31H, 32H, 33H处。当计数器的值被读到单片机中后,通过调用数据处理模块,对计数值进行相应的处理,求出所测参数的值和单位,最后应将参数值转换为十进制数,再转换为驱动LED数码显示器的段码,包括1个小数点。对计数值的处理运算要用到除法和乘法。为了用8位单片机来处理32位数的二进制到十进制的转换,首先利用字节除法求出每个字节对应的十进制数位值。

如:a100=[30H]/100, a10=([30H] mod 100)/10,a1=[30H] mod 10

其中,a1是频率值的第一个字节的个位, a10是频率值的第一个字节的十位, a100是频率值的第一个字节的百位。

我们将每位十进制数用非压缩BCD码表示,分别存储在AT89C51的直接地址40H~49H。然后通过如下计算:

40H=a1+6*a2+6*a3+6*a4

41H=a10+6*a20+5*a2+6*a30+3*a3+6*a40+a4

42H=a100+6*a200+5*a20+2*a2+6*a300+3*a30+5*a3+6*a400+a40+2*a4

43H=5*a200+2*a20+3*a300+5*a30+5*a3+a400+2*a40+7*a4

44H=2*a200+5*a300+5*a30+6*a3+2*a400+7*a40+7*a4

45H=5*a300+6*a30+7*a400+7*a40+7*a4

46H=6*a300+7*a400+7*a40+6*a4

47H=7*a400+6*a40+a4

48H=6*a400+a40

49H=a400

由于本设计用非压缩BCD码表示十进制数,40H到49H所表示的数值还要进行相应的调整,调整步骤如下: 42H←42H+40H/100

40H←40H mod 100

41H←41H+40H/10

40H←40H mod 10

43H←43H+41H/100

41H←41H mod 100

42H←42H+41H/10

41H←41H mod 10

……

调整后的每位十进制数都符合非压缩BCD码的表示规范。为了减小直接测频法的误差,本设计采用了十次平均逐步求精的方法。因为对同一待测信号,连续两次计数值之差不会超过1,所以可开辟一10字节的队列,初始时全为0,每次先将个位(40H)入队,然后求该队列的平均值,将商返送40H,余数送十分位。为使显示结果尽量精确,可用同样方法填充百分位、千分位、万分位和十万分位。

3.3 格式转换模块

本设计中,将显示模块能识别的计算结果定义为如下帧格式,即每帧由8字节(50H~57H)组成。其中50H表示测量值的第一个有效数字;51H表示52H~56H中还有几个整数位,剩下的为小数部分;57H

表示显示单位。如12159676表示115.967 MHZ,10985435表示1.98543KHZ。

四。 实验结果

为了验证本设计方案的正确性以及先进性,我们做了大量实验,该实验预置计数周期为10s。实验结果如下:

从前三组试验可知,本设计对于整数频率的测量误差为0;第四组试验的误差主要是由显示位数的精度不够引起的,即本设计最多只能显示6位,其余的将舍去,其最大误差是-0.9HZ;后两组试验的误差主要是由非整数频率引起的,这是直接测频法先天决定的,经过十次求平均可将其控制在-0.1HZ以内。

从实验结果可以看出,本方案将部分影响设计复杂度和实现成本的功能移至软件部分来实现,在不考虑显示精度引起的误差的情况下,该方案设计的数字频率计精确度可达99.9%以上,基本上能满足大部分使用领域的要求,且该方案具有设计成本低廉、设计简单、精度高、可测频带宽等优点,值得从事同类开发人员的借鉴。

本文作者创新点在于提出了一种基于CPLD和单片机相结合的设计方案。该方案以直接测频法为基础、软件补偿技术为辅助,大大降低了设计成本和实现复杂度,且较好地解决了误差问题。总之,论文所描述的设计思想先进,对同类使用具有较高参考价值。

责任编辑:gt

-

数字频率计2012-05-20 31941

-

基于fpga的数字频率计msp430单片机显示2015-09-30 7061

-

萌新求助,求一个单片机实现数字频率计的方案2021-11-08 1495

-

数字频率计测频率的基本原理2008-12-01 4161

-

基于单片机和CPLD的数字频率计的设计2008-10-15 1461

-

基于单片机的数字频率计的方案2010-03-24 6826

-

基于verilog语言的数字频率计设计2015-12-08 1712

-

基于51单片机的数字频率计2015-12-17 1767

-

基于Multisim的数字频率计2016-06-21 2684

-

基于单片机的系统硬件数字频率计的设计2017-09-21 1174

-

基于单片机的自动量程数字频率计的设计2017-10-26 1685

-

基于单片机设计的数字频率计文档下载2017-12-21 1315

-

基于51单片机的数字频率计的设计简介2021-05-27 1214

-

基于51单片机的数字频率计的设计讲解2021-07-22 2202

-

基于51单片机的数字频率计原理图2022-04-18 1492

全部0条评论

快来发表一下你的评论吧 !