采用现场可编程门阵列器件实现典型电路的设计方案

可编程逻辑

描述

1引言

在科研和工程中,数据采集系统具有很广泛的应用,针对各类电压型传感器输出的信号伏值不同这种情况,本文提出了一种能够控制增益的数据采集系统。该系统以FPGA作为逻辑控制核心,选用仪表运算放大器AD623作放大电路,ADG704作为模拟开关,通过对FPGA进行编程配置,控制模拟开关选通不同的电阻,选通电阻配合AD623实现放大。同时该系统可以对多通道配置不同的增益,从而可以采集不同传感器输出的信号。实现了采集范围宽的采集要求。

2 系统设计方案

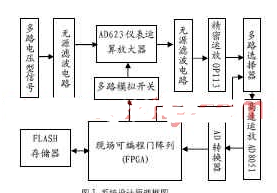

本设计采用现场可编程门阵列(FPGA)作为主控单元,实现整个系统的逻辑控制。整个系统的原理框图如图1所示。从整个流程来看,系统主要由以下几个模块组成:运算放大模块、AD转换模块、可编程逻辑器件控制模块。

整个系统的工作流程为:首先确定各通道输入信号范围,从而确定各通道的增益,对FPGA进行编程配置,使ADG704选中增益配置电阻,经AD623放大后通过精密运放OP113跟随输出,通过多路选择器切换将模拟信号输出至AD转换器,将转换完成的数据通过FPGA存储在FLASH。完成整个系统的数据采集。

3 典型电路设计

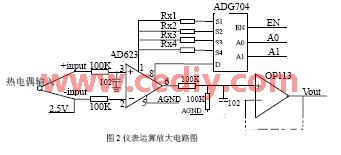

下图2为运算放大模块电路图。

该模块的核心为仪表运放AD623,AD623是一个集成单电源仪表放大器,它能在单电源(+3V~+12V)下提供满电源幅度的输出,其增益设置范围为1~1000。AD623通过提供极好的随增益增大而增大的交流共模抑制比(ACCMRR)而保持最小的误差,线路噪声及谐波将由于共模抑制比在高达200Hz时仍保持恒定而受到抑制。增益可通过1脚和8脚之间的电阻设置,其公式如下:

G为放大倍数。  为调节电阻。

为调节电阻。

图中输入信号前加一阶无源低通滤波器,滤除混叠在信号中的高频成分,信号截至频率可以通过

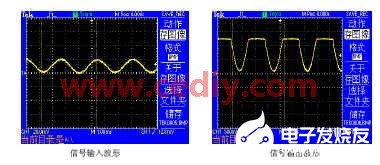

f=1/2ΠRC求得,同时在AD623输出端又加一级分压滤波器,它与前一级滤波器构成二阶无源低通滤波器。对滤波后的信号进行放大,对于AD623,如果信号不加共模信号直接放大,输出信号最大将会被限制在1.25V。如图输入信号为0~20mv正弦波,通过调节电阻使其增益设置为100,此时输出应为0~2V的正弦波,但实际波形如下:

如果在输入端加2.5V共模电压,电路图连接如图2,同样在输入端加0~20mv正弦波,增益设置为100,输出波形如下:

为了提高驱动能力,如图2中在AD623输出端加一级跟随器OP113作为驱动,因为AD623设计为驱动10K欧或以上的负载,如果负载小于10KΩ时,需要用一个精密运放作为缓冲提高驱动能力,接OP113作为跟随驱动器,当负载小到600Ω时,也可以在负载上得到0~4V的输出摆幅。

在图2中ADG704作为模拟开关,主要用来切换S1~S4中的某一通道与D导通,该选中通道与AD623配合实现增益控制。对于ADG704的控制,用可编程逻辑器件编程实现。控制使能和选择信号A1、A0、EN通过真值表1实现切换。

4 结束语

本文提出的由可编程逻辑器件控制系统的放大倍数,充分利用了仪表运算放大器AD623的增益可调功能及其优越性。每一路热电偶输入信号可以有多个不同的放大倍数,使得各种幅值不同的输入信号采集的实现更加方便、可靠、快捷。选用的16位AD转换器,以采集精度高、控制方便、转换速度快等优点,更大程度地优化了该系统。

本文作者创新点:通过对FPGA进行编程配置,可以对不同通道输入的伏值不同的电压信号分别设置增益,使每一个通道输出的信号正好在AD采集所需要的信号范围内。设计结构简单、体积小、适用性强、性能优良、可控性好、能够满足大部分试验和科研过程的需求,具有很广泛的适用性。

责任编辑:gt

-

现场可编程门阵列是什么2024-03-16 4202

-

FPGA现场可编程门阵列的综合指南2023-12-07 1714

-

简单认识现场可编程门阵列2023-12-01 2114

-

什么是FPGA?FPGA现场可编程门阵列的综合指南2023-09-14 2204

-

FPGA-现场可编程门阵列2021-07-30 1249

-

XA6SLX25-3CSG324Q现场可编程门阵列2021-04-26 1527

-

XC7K325T-2FFG900I现场可编程门阵列2021-04-13 1176

-

现场可编程门阵列有哪些应用?2019-08-06 4097

-

现场可编程逻辑门阵列器件 FPGA原理及应用设计2017-09-19 1053

-

现场可编程门阵列2015-03-13 2350

-

现场可编程门阵列的供电原理及应用2010-03-17 1894

-

现场可编程门阵列的结构与设计2009-07-07 1960

全部0条评论

快来发表一下你的评论吧 !