基于CY7C68013芯片和LVDS技术实现图像采集系统的设计

描述

目前在一些弹载设备中,由于采集的实时图像数据量很大,因此在其与地面测试台进行数据传输时需要很高的传输速率。传统的图像数据传输方法存在很大的局限性。比如,物理层接口无法满足数据的传输速度;由于传输通道的增多引起传输导线数量的增加导致系统功耗、噪声也随之增大等。低电压差分信号传输技术(LVDS)为解决这一问题提供了可能。

1 LVDS技术简介

LVDS技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可以是平衡电缆。LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。

图1为LVDS器件单工通信基本原理框图。它由一个驱动器、差分互连单元和一个接收器组成。驱动器和接收器主要完成信号电平和传输方式转换,它不依赖于特定的供电电压,很容易迁移到低压供电的系统中去,而性能不变。互连单元包含电缆、PCB上差分导线对以及匹配电阻。

2 系统总体方案设计

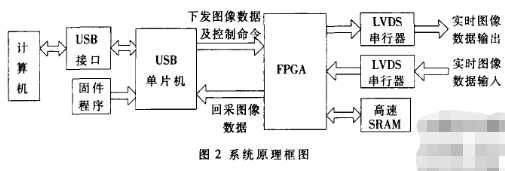

系统采用USB接口电路实现计算机与FPGA的数据传输,以LVDS串行器与解串器构建实时图像的发送与接收电路。系统的原理框图如图2所示。

系统的工作原理为:计算机将控制命令及实时图像数据经由USB接口发送给FPGA,FPGA将实时图像数据部分存储到高速SRAM,然后根据控制命令将SRAM中数据传送给LVDS串行器;另外,FPGA还需将回读的实时图像数据以20 MB/s的速度经由USB接口发送给计算机进行处理。

3 系统结构组成及其实现

3.1 USB接口实现

本系统所使用的USB单片机选用Cypress公司开发的EZ-USB FX2芯片CY7C68013。该芯片集成了51单片机内核、USB2.0收发器、串行接口引擎(SIE)、4 KBFIFO存储器以及通用可编程接口等模块,这些模块则保证了CY7C68013可与外围器件实现无缝的、高速的数据传输。用户在使用该单片机与外围设备进行数据传输时,只需直接利用GPIF接口来实现与外围设备之间的逻辑连接,就可以进行高速数据的传输。CY7C68013的GPIF接口有16位数据线,6个RDY信号和6个CTL信号。其中RDY信号为等待信号,GPIF可连续采样RDY信号。通常用来等待指定信号的某个状态出现,以确定GPIF下一步动作。CTL信号为控制输出信号。通常用作选通信号、非总线输出信号以及产生简单的脉冲信号。 CY7C68013在高速模式下,发送数据的码率可达到480 Mb/s,因此可将20 MB/s的实时图像数据实时地传送给计算机。

本系统的USB传输部分主要实现将计算机发出的控制命令及实时图像数据发送给FPGA,并将回读的实时图像数据发送给计算机。计算机发送的命令信号通过CY7C68013的PE端口传送给FPGA,实时图像数据通过CY7C68013的GPIF接口发送给FPGA或上传给计算机。由于USB与FPGA的传输速度不一致,所以还应在FPGA中设置两个软FIFO,分别用于图像数据的上传与下发。

3.2 LVDS数据发送与接收部分

本系统采用美国TI公司的10位总线型LVDS芯片SN65LV1023A和SN65LV1224A实现实时图像的高速数据传输和回采。两者发送和接收10 bit并行数据的速率在10 MHz~60 MHz之间。由于数据在并串转换时,SN65LV1023A会自动加上1位起始位和1位停止位,则串行数据发送的实际速率为120 Mb/s~792 Mb/s之间。LVDS串行器和解串器都需一个外部时钟。只有这两个外部时钟频率同步时,串行器和解串器才能正常通信。利用FPGA内部时序逻辑,完全能够解决工作时钟频率同步的问题。[page]

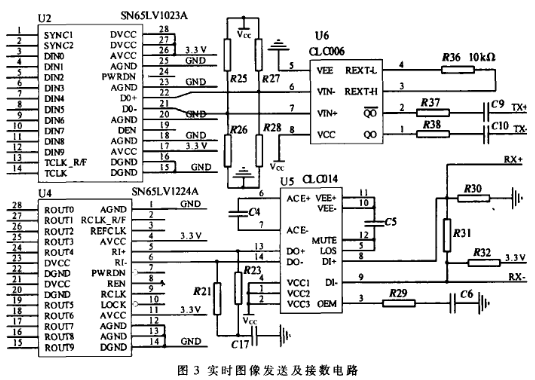

实时图像发送及接收电路如图3所示。FPGA根据计算机控制命令先从高速SRAM中读取1 B的数据,然后的将该字节外加两位的识别位共10位的并行实时图像数据输出到SN65LV1023A,再将转化后的高速串行差分信号经高速电缆驱动器CLC006驱动后远程传输。CLC006能在最高400 Mb/s数据速率下驱动75 Ω传输线,还具有可控的输出信号上升沿和下降沿时间,能使传输引入的抖动最小。通过调整R25/R27和R26/R28的阻值为驱动器提供正常输入信号。其值大小参考芯片资料接口连接部分选择,它随其输入电平类型及阻抗传输线而改变。驱动器的信号输出幅度随着Rext-H与Rext-L间电阻值的增大而增大。为了实现信号的最优化传输,将Rext-H与Rext-L之间电阻R36接为10 k?赘的可调电阻,根据实际情况调节R36阻值实现输出信号幅度范围的调整。

由于传输线对信号有损耗,而且容易产生信号失真、畸变和码元串扰等,本系统采用了自适应电缆均衡器CLC014对远程传输后接收到的数据进行均衡。CLC014具有同轴电缆和双绞线的自动均衡、载波检测与输出静音功能,适用数据速率范围为50 Mb/s~650 Mb/s,且具有极低的抖动性能。

LVDS接收器在内部虽然提供了针对输入悬空、输入短路以及输入不匹配等情况下的可靠性设计,但是当驱动器三态或LVDS接收器没有连接到驱动器上时,连接电缆会产生天线效应,此时LVDS接收器就有可能开关或振荡。为避免此种情况的发生,传输电缆采用双绞屏蔽电缆;另外在电路设计上外加上拉和下拉电阻来提高LVDS接收器的噪声容限。图3中的R31为100 Ω的匹配电阻,R32和R30分别为提高噪声容限的上拉和下拉电阻,阻值为1.5 kΩ。

FPGA主要通过控制LVDS串行器的TCLK、TCLK_R/F引脚以及LVDS解串器的RCLK、RCLK_R/F引脚实现数据的发送与接收。具体实现方法为:TCLK、RCLK引脚由FPGA分配同一时钟(时钟频率为20 MHz),在时钟的上升沿,FPGA先将从高速SRAM中读取的1 B的数据发送出去,另外在FPGA接收到1 B的数据后,先将其存入内部FIFO中,当FIFO中的数据达到512 B后通知USB单片机读取数据,然后发送到计算机。

4 实验结果

图4与图5分别为系统以20 MB/s的速度发送和接收的一帧512×512 B(每字节表示一个像素点)图像数据,分析结果表明发送与接收的图像数据完全一致,满足系统的设计要求。

采用LVDS技术与FPGA相结合的方法,实现了弹载图像采集设备与地面测试台之间高速数据传输,系统的传输速率可达到20 MB/s,并且提高了系统的可靠性和集成度。另外,整个系统的时序均由FPGA控制实现,具有很强的重构性。本设计已成功应用于某CCD图像采集设备的测试中,系统工作性能稳定。

责任编辑:gt

-

如何采用CY7C68013芯片设计图像采集系统2018-11-06 7429

-

基于CY7C68013的USB_Camera开发教程2016-12-17 1563

-

CY7C68013 与labview通信错误2016-05-16 4595

-

cy7c680132016-03-10 3226

-

采用CY7C68013芯片的系统固件程序设计2016-01-22 1172

-

基于USB2.0芯片CY7C68013的高速数据通信接口设计2011-09-21 1523

-

CY7C68013的固件程序开发方法2011-09-09 1899

-

基于CY7C68013的高速数据通信接口设计2011-09-08 992

-

基于CY7C68013的CCD图像传输系统2011-05-17 1285

-

CY7C68013器件中文手册2011-01-21 935

-

USB2.0控制器CY7C68013特点与应用2009-11-28 732

-

基于CY7C68013的USB数据采集系统2009-09-14 851

-

cy7c68013开发包及驱动2009-04-11 1968

全部0条评论

快来发表一下你的评论吧 !