极点跟随的LDO稳压器频率补偿方法的研究

电源设计应用

描述

LDO稳压器的频率补偿设计,不仅直接决定了频率稳定性,而且对LD0稳压器的性能参数,尤其是瞬态响应速度,有很大的影响。此外,随着当前半导体集成电路工艺的发展,越来越多的功能电路能够被集成于单一芯片中,而现有的LDO稳压器频率补偿技术,对芯片上频率补偿电容的需要,大大阻碍了LDO稳压器芯片集成度的提高和与其他功能电路的系统集成。

本文对LDO稳压器的频率稳定问题,和现有的频率补偿设计技术进行了理论分析。在此基础上,提出了一种新型的频率补偿方法,并给出了电路实现途径。通过一个采用TSMC0.18 μm混合信号半导体工艺,最大输出电流为100 mA的LDO稳压器设计,对该方法做出了进一步的说明。最后,结合LDO稳压器的HSpice仿真结果,对本文提出的频率补偿方法的效果进行了讨论。

便携电子设备无论是由蓄电池组,还是交流市电经过整流后(或交流适配器)供电,工作过程中,电源电压都存在变化。例如单体锂离子电池充足电时的电压为4.2 V,放电后的电压为2.3 V,变化范围很大。而各种整流器的输出电压不仅受市电电压变化的影响,还受负载变化的影响。因而近年来,低压差线性稳压器(LowDropout Linear Regulator)以其低成本,高电池利用率,洁净的输出电压等特点,被广泛应用于移动电话、掌上电脑等消费类电子产品,以及便携式医疗设备和测试仪器中。

2 LDO稳压器频率补偿

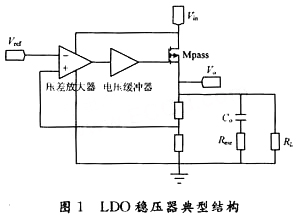

LDO稳压器的典型结构,如图1所示。图1中,Vref为具有良好温度特性的电压参考信号,Vin为不稳定的输入电压信号,Vo为输出电压信号。LDO稳压器利用由压差放大器、电压缓冲器、电压调整管Mpass和反馈网络构成的负反馈环路,维持Vo稳定。

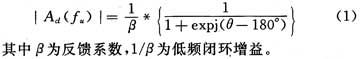

当环路对一定频率的信号的相移达到-180°时,负反馈成为了正反馈,如果环路增益T仍大于单位增益,环路将产生自激振荡,失去稳定Vo的作用,故需要频率补偿设计,来保证在相移达到-180°之前,T已衰减到单位增益以下。在单位环路增益频率fu处,环路相移与180°的和,被称为相位裕度θ。在θ与闭环增益Ac1间存在以下关系:

由式(1)可以看到,若相位裕度小于60°,则∣Ad∣大于1/β,即发生过冲。过冲会导致LDO稳压器的阶跃响应呈现欠阻尼振荡(振铃)。因而相位裕度不仅是考察频率稳定性的重要参数,而且对瞬态响应也有很大影响。

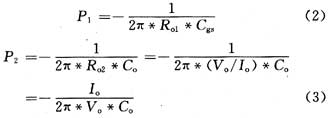

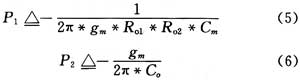

图1中存在两个低频极点,分别为位于电压缓冲器输出端的极点P1,和LDO稳压器输出端的极点P2。P1与P2的值由电压缓冲器的输出等效电阻Ro1,Mpass的栅、源极电容Cgs,LDO稳压器输出端的等效电阻Ro2和外接电容Co决定:

为保证LDO稳压器的频率稳定性和足够的相位裕度,P1与P2的间距(P1/P2)应足够大。但由式(3),P2随着LDO稳压器的输出电流的增大,逐渐向高频移动,使P1和P2的间距缩小,造成频率稳定性变差。

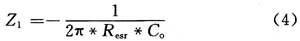

传统LDO稳压器的频率补偿方法,如图1所示,利用了输出端电容Co及其等效串联电阻Resr,产生一个左半平面(LHP)零点Z1:

若Resr的取值使Z1与P1足够接近,并相互抵消,则在LDO稳压器的通带内只有一个极点P2,环路相移不会超过-180°。但是,Resr会增加Vo在瞬态过程中的变化幅度,降低对Vin中噪声的抑制,且对Resr取值的要求,限制了Co可选择的类型,增大了使用难度和系统成本。此外,Resr的值还受到环境温度、电压和频率的影响,所以频率稳定性不能得到可靠的保障。

由于以上原因,当前的LDO稳压器,多采用内部频率补偿。一类内部频率补偿技术借鉴了传统LDO稳压器的零、极点抵消方法,并利用前馈技术,或芯片内部的RC网络和电压控制电流源,产生所需的零点。但是,要做到芯片内产生的零点与相应极点的完全匹配,是非常困难的。而未能相互抵消的零点和极点,会成为LDO稳压器通带内的零、极点对(doublet),造成Vo建立时间的增加。另一类广泛使用的内部频率补偿为米勒频率补偿。米勒补偿具有极点分离的特性,即通过跨接在Mpass栅极和漏极的米勒电容Cm,将P1推向低频,P2推向高频。米勒补偿后,P1与P2由式(2)、式(3)变为:

其中,gm为Mpass的跨导。

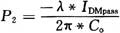

由式(5),欲使P1远小于P2,则Cm会很大,电路内部对其充放电的过程造成Vo的压摆时间tsr变长。因Co很大,由式(6),P2处于低频,限制了增益带宽GBW。米勒补偿对tsr和GBW的影响,直接增大了LDO稳压器的环路延时td(参看式(7))。虽然通过嵌套的米勒频率补偿方法或电容倍增电路,能够减小Cm,但未能根除Cm对LDO稳压器芯片的集成度的影响。

针对以上问题,下节将给出一种能够保证LDO稳压器的高速,且无需芯片上频率补偿电容的新型频率补偿方法。

3 极点跟随频率补偿

LDO稳压器空载时,由式(3),P2为0 Hz(实际上,此时 ,λ和IDMpass为Mpass的沟道调制系数和漏极电流),P1只需大于0 Hz,P1与P2的间距(P1/P2)就足以保证频率稳定性。随着输出电流的增大,P2向高频移动,如果P1能够跟随P2的变化,则P1与P2的间距得到维持。极点跟随的频率补偿,即是当输出电流变化时,通过使P1跟随P2的变化,获得频率稳定性的方法。

,λ和IDMpass为Mpass的沟道调制系数和漏极电流),P1只需大于0 Hz,P1与P2的间距(P1/P2)就足以保证频率稳定性。随着输出电流的增大,P2向高频移动,如果P1能够跟随P2的变化,则P1与P2的间距得到维持。极点跟随的频率补偿,即是当输出电流变化时,通过使P1跟随P2的变化,获得频率稳定性的方法。

一种使P1跟随P2变化的电路实现,可利用共集电极和共漏极电压缓冲器的输出电阻,分别与偏置电流和偏置电流的开方成反比的规律,根据输出电流来动态地调整电压缓冲器的偏置电流,使P1也受输出电流控制。

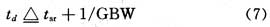

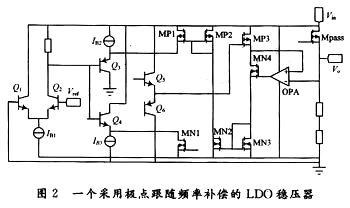

一个采用了极点跟随频率补偿的LDO稳压器,如图2所示。其中,完成频率补偿的动态偏置电压缓冲器,包括了由MOS晶体管MP3,MN4和运算放大器OPA组成的输出电流监测电路,由MN1~MN3和MP1~MP2组成的电流镜电路,以及由电流源IB2,IB3和双极晶体管Q3~Q6组成的电压缓冲器。

输出电流监测电路中的MP3与LDO稳压器的电压调整管Mpass的源、栅极驱动电压相等,且由于运放OPA输入端“虚短”特性,MP3的漏极(OPA正向输入端)电压等于Mpass的漏极(OPA负向输入端)电压,故有:

对照式(3)与式(13),可以看到,P1/P2独立于Io,故图2中的LDO稳压器获得了在整个负载变化范围内的频率稳定性。

4 仿真结果与讨论

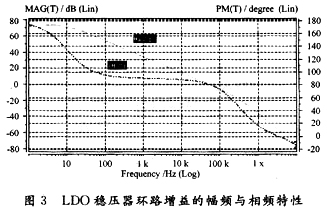

采用TSMC 0.18 μm混合信号Spice模型,和高精度仿真工具HSpice,对图2中的LDO稳压器进行了设计与仿真验证。在Co=1 μF,Io=100 mA的条件下,环路增益T的幅频与相频响应的仿真结果如图3所示,在单位环增益频率内,幅频特性与单极点系统相同,以-20 dB/dec的速度衰减,相位裕度大于80°。

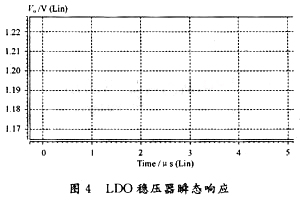

图4为输出电流Io在20 ns内由0跳变为100 mA时,LDO稳压器输出电压Vo的瞬态响应。由图4可以看到,Vo从空载到满载的转换时间约为0.5μs。如此良好的瞬态响应是由于极点跟随频率补偿具有以下优点:极点P1对P2的跟随,减小了P1的附加相移,增加了相位裕度,则由式(1),有利于减小过冲导致的输出电压振铃现象;无需引入零点,因而避免了零、极点对造成的输出电压稳定时间的增加;对带宽没有限制,且无需米勒频率补偿电容,则由式(7),有利于减小环路延时。此外,电压缓冲器中的甲乙类推拉结构和动态电流,对提高响应速度也有很大帮助。

最后需要说明的是,对输出电压Vo进行的直流扫描结果表明,Vo在整个输出电流范围内的变化较大,约为4 %。经分析,主要由以下因素造成:图2中的宽带压差放大器的非对称结构引入了较大的输入失调电压;双极器件的基极电流,以及NPN型器件与PNP型器件参数(放大倍数等)的差异引入的误差。通过改用对称结构的低失调压差放大器,并将双极器件替换为MOS器件,可提高LDO稳压器的精度。但是由于低失调压差放大器引入的低频极点,以及MOS器件的低跨导造成的P1的频率降低,会减小相位裕度,所以应避免在压差放大器中采用电流镜(引入镜极点)或共源共栅(增加节点电阻)等结构,并适当提高电压缓冲器中器件的尺寸和偏置电流。

本文提出的极点跟随的频率补偿方法,提供了LDO稳压器良好的频率稳定性和瞬态响应,且无需芯片上频率补偿电路,因而不仅适用于高负载变化响应速度的单芯片LDO稳压器,在集成电源管理和片上系统(SOC)方面,也有较好的应用前景。

-

如何选择最佳稳压器2024-01-08 2663

-

LDO稳压器的正确使用方法2023-12-20 1916

-

线性稳压器件补偿和波特图相关资料推荐2021-05-25 1215

-

LDO稳压器内部频率补偿电路及满足系统稳定性要求的应用设计2021-03-09 6698

-

LDO线性稳压器的系统稳定性问题及其频率补偿方法详细说明2020-04-03 1900

-

全集成型CMOS LDO线性稳压器设计2016-09-14 6250

-

基于高性能LDO线性稳压器的设计2011-04-14 2028

-

LDO线性稳压器关键技术分析2011-03-11 1583

-

LDO稳压器中动态频率补偿和限流保护的研究2010-10-18 883

-

LDO稳压器等效串联电阻的稳定范围2010-10-16 1140

-

LDO线性稳压器动态频率补偿电路设计2010-05-14 1559

-

一种LDo稳压器内部动态频率补偿电路的设计2010-04-28 1639

-

LDO线性稳压器的研究与设计2009-12-02 10094

-

[分享]如何选择低压差稳压器2009-01-07 3883

全部0条评论

快来发表一下你的评论吧 !