基于FPGA EPlS30芯片和AD变换器实现导航系统的设计

可编程逻辑

描述

1 引 言

INS/GPS组合导航系统在军事领域和民用方面的运动载体中得到了广泛应用。INS是组合导航系统中的核心部分,涉及多个陀螺仪、多个加速度计和温度传感器等众多传感器数据的采集与处理,同时对系统运算的实时性要求也很高。对于导航计算机系统的研究,许多学者做了大量有益的工作。传感器数据采集现有方案大多采用一片多路△-∑结构的AD芯片采集6路惯性器件信号,这就造成6路信号的数据采集不能同时进行,在高动态下导致组合导航系统导航精度的下降。本文以TI公司生产的AD变换器AD1274和Altera公司生产的FPGA EPlS30位主选芯片,阐述了组合导航系统的实现方法。

2 数据采集

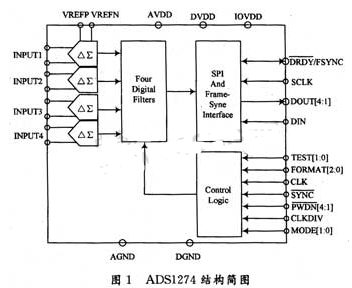

组合导航系统的传感器包括3个低成本微机械陀螺仪(AD‘ADXRS150)、3个微机械加速度计(AD’ADXL210)、压力传感器(Motorola‘MPX4115A)、二轴磁罗盘(Honeywel’HMC1022)、一个温度传感器(TI‘TMP275)和GPS。对于这些传感器需同时采样,方能满足组合导航系统的要求。本系统选用TI公司生产的高精度模数转换器ADS1274。ADS1274是一款高性能的24位△-∑结构的AD转换器,有4路同步采样输入通道,输出有串行和并行两种方式,如1所示。

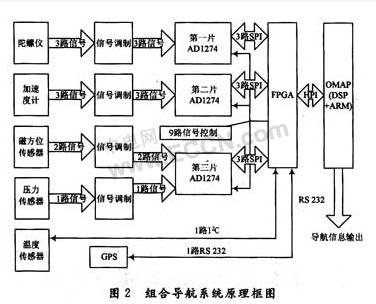

本系统中共采用3片AD1274,一片用于3个陀螺仪信号的数据采集;另一片用于3个加速度计的数据采集;第三片用于2个磁方位传感器、1个压力传感器的数据采集,温度传感器的输出信号为数字信号,不需要进行模数变换。每一片均剩余一路AD,用于今后深入研究的冗余系统。

为了克服由于传感器输出信号数据采集时间上的不同步引起的导航计算偏差,除采用具有4通道同步采用的AD1274外,数据采集系统的控制采用具有并行机制的FPGA,芯片选用Altera公司的Cyclone低成本FPGA EP1C6Q240。

3 组合导航系统的设计

组合导航系统的功能包括:

数据采集 采集各种传感器信号(陀螺仪、加速度计、磁罗盘、温度计、气压高程等);

预处理 采用数字滤波技术对采集到的传感器信号进行预处理;

导航计算 利用导航算法进行数据融合处理;

输出导航信息 将系统的位置、速度、姿态的功能信息输出到运动载体控制系统,进行导航指示和运动控制。

导航计算和导航信息输出采用TI的OMAP5912实现。组合导航系统原理如图2所示。

OMAP5910是TI公司生产的双核处理器,将TMS320C55XTMDSP内核与ARM9TDMI内核集成在单芯片上,实现了应用性能与低功耗的最佳组合。这种独特的架构不仅提供了DSP的低功耗、实施信号处理功能,同时还提供了ARM的命令和控制功能。充分发挥了DSP进行加、乘运算的优势,进行导航参数的实时运算,发挥ARM超强事务管理功能进行如导航数据的输出、显示、控制伺服机构等。

4 FPGA设计

4.1 FPGA逻辑设计

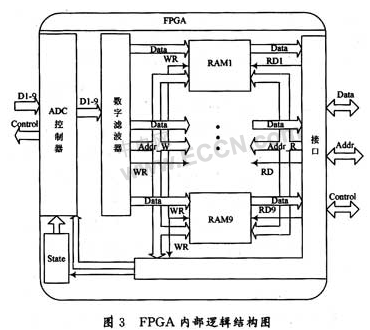

FPGA的主要工作在于:同步产生各ADC的工作时序;同步发送命令字;同步接收、数字滤波和存储各ADC的转换数据;提供与外部处理器的逻辑接口。FPGA内部的逻辑单元主要包括:状态机(State)、ADC控制器、数字滤波器、RAM块、接口单元等,对应的结构如图3所示。

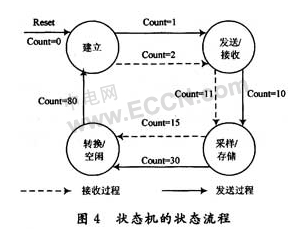

状态机State是FPGA内部的控制单元,它按照固定的节拍周而复始地运行,并指挥着ADC控制器完成各种操作。根据FPGA对ADC数据发送和接收的不同过程,状态机可分为不同的4个状态周期。对于发送过程,其4个状态周期依次为:建立周期、发送周期、采样周期、转换周期;对接收过程,其4个状态周期依次为:建立周期、接收周期、存储周期、空闲周期。由于发送和接收过程在时间上可以重叠,其状态流程图如图4所示,其中Count的值是根据采样频率确定的,对不同的系统可参照选择。

ADC控制器是FPGA内部的主要执行单元,它按照状态机的节拍和状态指示进行相应的工作。RAM是FPGA内部的数据存储单元,用于存储各ADC转换的数据。接口单元是FPGA内部的功能协调单元,为外部处理器OMAP对FPGA的访问提供桥梁,当OMAP向FPGA写入ADC初始化配置字时,接口单元将配置字送往ADC控制器,同时复位状态机;当OMAP读取FPGA内部RAM块的数据时,接口单元对外部处理器的访问地址进行译码,选中对应的RAM块,将访问的数据送到外部处理器的总线上。

对于低成本微机械陀螺仪和加速度计,由于微惯性仪表技术不很成熟,在性能和精度上仍存在不足,如数据输出中存在野值现象和较大漂移,严重影响了系统的正常工作和精度,因此在进行组合导航数据融合算法之前,有必要对微机械传感器(陀螺仪、加速度计、压力传感器等)输出的数据进行预处理。本系统采用文献介绍的方法利用FPGA设计FIR滤波器。考虑总体要求,数字滤波器设计指标:通频带0~20 Hz;通带衰减不大于-3 dB;过渡带宽5 Hz;阻带内最小衰减不小于-20 dB;采用频率100 Hz。

FPGA通过这些内部结构单元的协调工作,来完成对各ADC数据的同步采集,以及与外部处理器OMAP的无缝接口。

4.2 逻辑仿真

根据FPGA内部的逻辑单元结构和功能,在Altera公司提供的QuartusⅡ开发平台中,用VHDL语言对上述逻辑进行了设计,并进行了功能仿真。其设计结果已在该公司的EP1C6得到实现,且性能稳定。

5 结 语

本文提出了基于FPGA和高精度ADC的组合导航系统,该系统具有开发周期短、集成化程度高等特点。软件和硬件均采用编程实现,设计灵活,容易修改,在实际应用中收到良好的效果。通过跑车试验,基于FPGA和高精度ADC的组合导航系统的导航位置精度:水平位置6 m(无DGPS),5 min 300 m(无GPS信号);姿态精度:横滚和俯仰角度0.3°~0.5°(有GPS),0.7°~1.0°(无GPS);航向角度0.4°(有GPS),2°(无GPS)。实验证明该设计方案切实可行,达到了预期目的。

责任编辑:gt

-

嵌入式导航系统DIY分享2019-12-10 3621

-

怎么实现基于DSP的车载GPS/DR组合导航系统硬件设计?2021-05-12 1427

-

怎么实现基于Linux的嵌入式车载导航系统的设计?2021-05-18 2018

-

怎么实现嵌入式GPS导航系统的设计?2021-05-26 1519

-

怎么实现基于51单片机&GPS的导航系统设计?2021-09-30 2459

-

如何实现基于Linux的嵌入式车载导航系统的设计?2021-12-27 1134

-

基于Linux的嵌入式车载导航系统的设计2009-12-22 1086

-

矩阵变换器空间矢量调制策略的FPGA实现2010-01-13 398

-

基于FPGA的AC-AC谐振变换器实现2011-08-29 3345

-

基于FPGAs的智能机器人导航系统2015-11-30 539

-

在FPGA 2上使用距离变换的人工智能自主飞机导航系统2017-09-08 1017

-

基于FPGA的组合导航系统解析2017-11-22 1351

-

基于FPGA的电力电子变换器控制系统设计2018-01-29 1434

-

基于FPGA的惯性导航系统设计2018-03-04 3800

-

基于Android的地铁出口导航系统设计与实现2023-10-20 569

全部0条评论

快来发表一下你的评论吧 !