基于现场可编程门阵列技术设计时钟分配网络的应用方案

可编程逻辑

描述

1 引言

自产生到现在,现场可编程门阵列(FPGA)以其独特的优点被成功应用在工业控制、数据通信、计算机硬件等领域,也成功应用在保密通信和多种先进的武器系统中。我国在FPGA的开发方面起步较晚,开发具有自主知识产权的FPGA具有重要意义。各种应用条件要求FPGA能够快速进行大量数据传输与处理,同时,不断提高的工艺水平已将CMOS电路速度提高到了一个新的层次,这要求FPGA的时钟信号有更高的速度与精度。时钟分配网络决定了时钟的速度与精度,决定着数据的稳定与可靠。本文结合FPGA的特点,在优化时钟网络功耗与面积基础上研究FPGA内嵌时钟锁相电路,从整体上给出了一种FPGA时钟分配网络设计方案。

2 FPGA的时钟布线结构

高性能的FPGA可用于实现一个完整的系统,系统有不同组成部分,每一部分需要不同的时钟,这就需要多个时钟组成时钟网络。许多FPGA允许利用通用逻辑布线资源进行时钟布线,但其时钟偏差较大,一般设计中需单独设计时钟网络。另外,时钟网络的功耗占了FPGA的很大一部分,设计时要先考虑功耗、面积,严格设计以给FPGA中的每个模块提供低功耗、高速、偏差小的时钟信号。通常FPGA均将时钟信号分为全局和局部两种,把芯片分为四个象限区域,布线时将时钟信号分层次布到每个区域。局部时钟只分布在FPGA的一个区域,可连到区域中的每一个触发器。全局时钟分布于整个芯片,但不一定要连到每一个逻辑单元中的触发器。Altera 公司的Stratix Ⅱ系列提供了16个全局时钟信号,可连到FPGA的每一个触发器,同时在每个象限区域提供8个时钟信号。同样,Xilinx的Virtex Ⅱ Pro也提供了16个全局时钟,给每个象限区域提供8个局部时钟,但其全局时钟不直接驱动触发器,而只驱动到每个象限的局部时钟网。

根据现有的FPGA的时钟网络,可提出一个有效的时钟模型。 模型将时钟网络分为三级,第一级是从芯片外围的时钟源到时钟区域中心的可编程连接,包含全局和局部两个平行的时钟网络;第二级是从区域中心时钟信号到此区域中逻辑块间的可编程连接,每个区域都有这样的网络;第三级(图3)是从逻辑块时钟到其中逻辑单元的可编程连接。

图1示范性的将FPGA芯片分成了9个区域,时钟源置于芯片四周,芯片的每一边布有四分之一的时钟源,全局时钟从每一边的时钟源引到FPGA中心,再通过H树连到每个区域的中心。局部网络从与本区域最邻近时的芯片两边选择局部时钟源,将其连到区域中心。每个区域的逻辑块通过SRAM控制的多路选择器可以灵活的选择使用全局或是局部时钟(见图2)。此方式中,FPGA可支持多个置于芯片周围的时钟源,同时通过限制芯片中每一区域能同时使用的时钟数,有效减少了整个时钟分配网络的复杂性,而对性能影响较小。

利用这个模型可将时钟网络的组成单元如时钟源数,全局和局部时钟数,时钟区域数等参数化,然后研究参数变化对芯片面积及功耗的影响,由此可以得出一个功耗与面积优化的时钟网络结构[3]。

3 利用锁相环的时钟分配结构

通常在速度不高,芯片的复杂度不是很高的情况下,通过选择合适的时钟分配网络就可得到满足要求的FPGA时钟。随着复杂度与速度的提高,因温度、工艺参数或电源电压变化所引起的时钟偏差严重影响FPGA的工作。此时需在FPGA时钟网络结构中设计锁相环将时钟信号锁定在稳定的参考频率上,消除分配网络的时钟偏差,使芯片中的触发器能准确地同步工作。同时,利用锁相环的频率合成功能,FPGA芯片内部可工作在一个较高的频率上,而外部接口工作于较低频率,这样提高了芯片的数据处理能力又不增加板级接口的实现难度。

在FPGA中,时钟沿在各个寄存器的相对到达时间决定了芯片能否准确工作,而时钟沿到寄存器的绝对延时时间则对系统功能影响不大。设计时通常关心时钟分配路径的相对延时,保持时钟沿在同一时刻到达寄存器。这种特点使得锁相环在时钟分配网络中得以应用,锁相环使得时钟延时为一个周期的整数倍,保证了不同寄存器处的时钟能同步。

在时钟分配中利用锁相环的技术称为零延时缓冲(Zero-Delay Buffer)技术。其原理如图4所示[4]。图中将时钟缓冲树(clock tree)结构中的一个时钟信号回馈到锁相环与参考时钟进行相位比较,根据误差调节相位将负载时钟与参考时钟对齐,实现了时钟信号到负载的零延时。图中R1-R4为靠近缓冲树端的电阻用于匹配负载连线的特征阻抗,保证了信号完整性。设计时在工艺上保持负载连线与反馈连线长度一致可减小时钟偏差。

4 锁相环的实现

在FPGA中一般可用模拟锁相环(PLL)或数字延迟锁相环(DLL)来实现时钟信号的合成。PLL利用相位误差控制可产生时钟的压控振荡器(VCO),使其输出时钟信号与参考时钟信号的相位对齐。而DLL没有VCO,不产生时钟,它是通过可控的延时单元来调整延时时间,完成相位对齐。

模拟锁相环可用电荷泵锁相环(CPPLL)来实现,实质上它属于混合信号锁相环[5](Mixed Signal PLL)。其由鉴相器产生相位误差电压,利用电荷泵累积误差电压,滤波后控制压控振荡器产生与外部时钟同步的信号。其原理框图如图5所示。

图中分频器用来完成时钟信号频率合成,可以使时钟工作在N倍的参考频率上。文 [6]给出了此类锁相环的详细实现过程。

通常情况下PLL需要高阶滤波器,其稳定性设计较复杂,一般在特殊要求的场合使用。而DLL一般只需要一阶滤波,且系统的阶数就是滤波器的阶数,设计相对简单。另一方面, FPGA中晶体管的切换使得芯片内部存在很大的电源噪声,传统的PLL使用的压控震荡器(VCO)对噪声与抖动有积累作用,易受干扰; DLL不使用VCO,对噪声无累积作用,可抑制噪声,且在工艺、电压和温度(PVT)变化时工作较稳定[9]。因此,FPGA中更倾向于用纯数字构成的DLL调整时钟偏差,市场上Xilinx 的Spantan Ⅱ和Virtex系列均使用数字DLL[10]。

传统的DLL原理如图6所示。电路包含压控延迟线(VCDL),鉴相器,电荷泵,滤波 器。VCDL由参考时钟驱动,它只利用末级输出时钟与参考时钟进行相位比较,产生输出误差电压,再由电荷泵累加、滤波器滤波后产生VCDL的控制电压,由此调整延时,将输出时钟与参考时钟相位对齐。正确锁定时VCDL的总延时为参考时钟的一个周期。

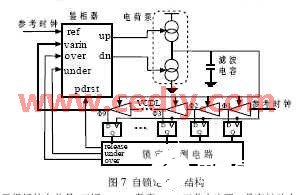

实际工程设计中,可将VCDL中每一级延时单元的输出信号均作为反馈信号,完成复杂的控制,增强DLL环路功能。图7是在传统结构了增加了锁定检测电路的DLL,图中的VCDL用了9级延时缓冲,每一级的输出在参考时钟上升沿被锁存,锁定检测电路根据锁存的信号产生相应于延时过长(过延时)、延时过短(欠延时)以及延时正常的信号,鉴相器根据锁定检测电路的这些信号释放控制或者控制电荷泵充放电。具体来说,图中锁定检测电路对VCDL末级的延时进行判断,如其大于1.5个参考时钟周期,则产生过延时(over)信号;小于0.75个参考时钟周期,则产生欠延时(under)信号;末级延时达到1.25个参考时钟周期时产生代表延时正常的release信号。鉴相器一旦检测到 over或者under信号,它立即将控制交给锁定检测电路,由over或under信号直接控制电荷泵的充放电。当release信号被检测到时,鉴相器复位over与under信号,比较参考时钟与VCDL末级输出的相位,根据相位误差控制电荷泵的充放电。利用此原理构成的DLL电路可以防止环路锁定到2倍以上的参考时钟周期,环路的捕捉范围更大,响应速度更快,同时产生的抖动更小[7]。另外,在此结构上增加一些逻辑电路便可进行频率合成,最大频率可达9倍的参考时钟频率[7]。

这种DLL已很好的在单晶-三铝-0.5um数字CMOS工艺中实现,具有抖动小,工作稳定,最高频率可达1Ghz.[8]

5 结论

在一个可优化功耗与面积的布线结构模型基础上,将数字延迟锁相环引入时钟分配网络,有效解决了网络的时钟偏差。同时抑制了噪声,使FPGA工作稳定,抖动小。

本文作者创新点:在时钟网络布线结构中引入自锁定数字延迟锁相环减小时钟偏差,给出了一个有效的时钟网络设计方案。

责任编辑:gt

-

现场可编程门阵列是什么2024-03-16 4176

-

FPGA现场可编程门阵列的综合指南2023-12-07 1692

-

FPGA-现场可编程门阵列2021-07-30 1248

-

XA6SLX25-3CSG324Q现场可编程门阵列2021-04-26 1525

-

XC7K325T-2FFG900I现场可编程门阵列2021-04-13 1172

-

现场可编程门阵列有哪些应用?2019-08-06 4096

-

现场可编程逻辑门阵列器件 FPGA原理及应用设计2017-09-19 1045

-

现场可编程门阵列2015-03-13 2344

-

现场可编程门阵列的供电原理及应用2010-03-17 1892

-

现场可编程门阵列的结构与设计2009-07-07 1949

全部0条评论

快来发表一下你的评论吧 !