基于Altera的FPGA器件完整设计流程以及开发工具分析

可编程逻辑

描述

近年来,随着微电子学的迅速发展以及SoC(System on Chip,片上系统)技术在设计领域引起的深刻变革,EDA(Electronic Design Automatic,电子设计自动化)工具在系统设计中的地位愈发重要。特别是20世纪90年代后,电子系统已经由电路板级发展为ASIC(Application Specific Integrated Circuit,专用集成电路)、FPGA(Field Programmable Gate Array,现场可编程门阵列)以及嵌入式系统等多种模式,其中FPGA设计正是当前数字系统设计领域中的重要方式之一。

本文以Altera公司的FPGA为目标器件,通过一个8-bit RISC CPU的设计实例,系统地介绍了FPGA的完整设计流程以及开发过程中用到的多种EDA工具,包括Modelsim、Synplify、Quartus II,并重点说明如何使用这些EDA工具进行协同设计。

1 FPGA的设计流程

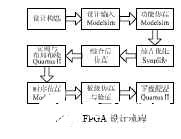

一般来说,完整的FPGA设计流程包括电路设计与输入、功能仿真、综合优化、综合后仿真、实现与布局布线、时序仿真、板级仿真与验证、调试与加载配置等主要步骤,如图1所示。

电路设计与输入是指通过某些规范的描述方式,将工程师的电路构思输入给EDA工具,常用的设计方法有HDL(Hardware Description Language,硬件描述语言)设计输入法与原理图设计输入法。目前进行大型工程设计时,最常用的设计方法是HDL设计输入法,它利于自顶向下设计以及模块的划分与复用,可移植性和通用性好,设计不因芯片的工艺与结构的不同而变化,更利于向ASIC移植。

电路设计完成后,要用专用的仿真工具对设计进行功能仿真(Functional Simulation),验证电路功能是否符合设计要求。功能仿真又称前仿真(Pre-Simulation)。通过仿真能及时发现设计中的错误,加快设计进度,提高设计的可靠性。

综合(Synthesis)优化是指将HDL语言、原理图等设计输入翻译成由基本门、RAM、触发器等基本逻辑单元组成的逻辑网表,并根据目标与要求(约束条件)优化所生成的逻辑网表,输出标准格式的网表文件,供FPGA厂商的布局布线器进行实现。

综合后仿真(Post Synthesis Simulation)的作用是检查综合出的结果与原设计是否一致。作综合后仿真时,要把综合生成的标准延时格式SDF(Standard Delay Format)文件反标注到综合仿真模型中去,可估计门延时带来的影响。综合后仿真虽然比功能仿真精确一些,但是只能估计门延时,不能估计线延时,仿真结果与布线后的实际情况还有一定差距,并不是十分准确。目前主流综合工具日益成熟,对于一般性设计,如果设计者确信自己表述明确,没有综合歧义发生,则可以省略综合后仿真步骤。

综合结果的本质是一些由基本门、触发器、RAM等基本逻辑单元组成的逻辑网表,它与芯片实际的配置情况还有较大差距,此时应该使用FPGA厂商提供的软件工具,将综合输出的逻辑网表适配到具体FPGA器件上,这个过程叫做实现(Implementation)。在实现过程中最主要的过程是布局布线(P&R),所谓布局(Place)是指将逻辑网表中的硬件原语或底层单元合理地适配到FPGA内部的固有硬件结构上,布局的优劣对设计的最终实现结果(包括速度和面积两个方面)影响很大;所谓布线(Route)是指根据布局的拓扑结构,利用FPGA内部的各种连线资源,合理正确地连接各个元件的过程。一般情况下,用户可以通过设置参数指定布局布线的优化准则。总体来说,优化目标主要有两个方面——面积和速度。一般根据设计的主要矛盾,选择面积或速度或平衡两者等优化目标,但是当两者冲突时,一般满足时序约束要求更重要一些,此时选择速度或时序优化目标效果更佳。

将布局布线的时延信息反标注到设计网表中,所进行的仿真就叫时序仿真(Timing Simulation)或布局布线后仿真,简称后仿真(Post-Simulation)。布局布线后生成的SDF文件包含的时延信息最全,不仅包含门延时,还包含实际布线延时,所以布局布线后仿真最准确,能较好地反映出芯片的实际工作情况。一般来说,布局布线后仿真步骤必须进行,通过布局布线后仿真能检查设计时序与FPGA的实际运行情况是否一致,确保设计的可靠性与稳定性。

在有些高速设计情况下,还需要使用第三方的板级验证工具进行仿真与验证,这些工具通过对设计的IBIS、HSPICE等模型的仿真,能较好地分析高速设计的信号完整性、电磁干扰等电路特性等。FPGA设计开发流程的最后步骤就是在线调试或将生成的配置文件写入芯片中进行测试。

2 EDA工具介绍

图1不仅显示了FPGA的设计流程,还给出了8-bit RISC CPU设计实例中用到的EDA工具与FPGA设计流程中每一步的对应关系。

2.1 仿真工具Modelsim

目前仿真工具种类繁多,但在业界最流行、影响力最大的仿真工具还是Mentor Graphics公司的Modelsim,其主要特点是仿真速度快、仿真精度高,且图形化界面友好,具有结构、信号、波形、进程、数据流等窗口。Modelsim不仅支持VHDL和Verilog HDL的仿真,还支持VHDL和Verilog HDL混合编程的联合仿真。PC版Modelsim的仿真速度也很快,甚至和工作站版不相上下。

2.2 综合工具Synplify

Synplicity公司的Synplify作为新兴的综合工具在综合策略和优化手段上有较大幅度的提高,特别是其先进的时序驱动和行为级提取综合技术B.E.S.T(Behavior Extraction Synthesis Technology)算法引擎,使其综合结果面积小、速度快,在业界口碑很好,如果结合Synplicity公司的Amplify物理约束功能,对很多设计能大幅度地减少资源,优化面积达到30%以上。

2.3 集成开发环境Quartus II

Quartus II是Altera公司的第四代可编程逻辑器件集成开发环境,提供从设计输入到器件编程的全部功能。Quartus II可以产生并识别EDIF网表文件、VHDL网表文件和Verilog HDL网表文件,为其它EDA工具提供了方便的接口。

3 8-bit RISC CPU设计实例

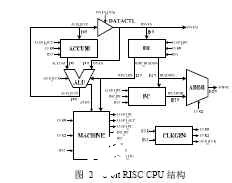

CPU是一个复杂的数字逻辑电路,但其基本部件的逻辑并不复杂,可将其分为8个模块,各模块的名称及功能列于表1中,它们之间的连接关系如图2所示。

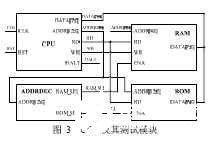

为了对所设计的CPU进行仿真测试,还需要建立一些必要的外围虚拟器件模型,包括装载测试数据的RAM、存储测试程序的ROM和用于选通RAM或ROM的地址译码器ADDRDEC。在仿真测试中,用这些虚拟器件来代替真实的器件对所设计的CPU进行验证,检查各条指令的执行是否正确、与外围电路的数据交换是否正常,这与用真实器件进行调试的情况非常接近。这些虚拟器件模型都可以用Verilog HDL描述,由于不需要被综合成具体的电路,所以只要保证这些虚拟器件模型的功能和接口信号正确即可。它们之间的连接关系如图3所示。

在测试台程序(Testbench)中利用模块调用的方法把CPU及其外围测试模块按图3连接起来。在Testbench中运行3个不同的汇编程序,对CPU进行完整的逻辑测试与验证。在Modelsim中,首先对所有的设计输入文件进行编译,编译通过后,对Testbench模块进行仿真。下面截取了一段功能仿真的结果:

run -all

# ROM Loaded Successfully

# RAM Loaded Successfully

# Running CPUtest1

# TIME PC INSTR ADDR DATA

# 1200.0ns 0000 JMP 003c zz

# 2000.0ns 003c JMP 0006 zz

# 2800.0ns 0006 LDA 1800 00

# 3600.0ns 0008 SKZ 0000 zz

# A HALT Instruction was Processed

# Break at cpu_test.v line 29

功能仿真通过后,要根据目标器件(Altera FLEX10K EPF10K10 TC144-4)对设计进行综合。为了便于及时发现综合中出现的问题,综合工作应分阶段进行,首先对构成CPU的各个子模块进行综合以检查其可综合性,然后再对整体的CPU模块进行综合优化。综合工具选择Synplify。

布局布线工具选择Quartus II,对Synplify综合器输出的edf文件进行全编译。全编译是指从分析、综合、适配(布局布线)、编程到时序分析的全过程。实际上,设计在Synplify中已经综合好了,但分析与综合对于Quartus II来说是必须的,主要是用来生成数据库文件。由于Quartus II中还内嵌了综合工具,所以也可以使用Quartus II来完成从综合到布局布线的全过程(即全编译)。全编译完成后,Quartus II会自动生成布局布线后的网表文件和标准延时格式SDF文件。

要完成时序仿真,首先要将功能仿真时Modelsim工程中的RTL级设计文件替换为Quartus II布局布线后生成的网表文件,并编译通过。在Modelsim中,加入事先编译好的Altera仿真库文件和延时反标SDF文件,对Testbench模块进行仿真。截取的一段时序仿真结果如下:

run -all

# ROM Loaded Successfully

# RAM Loaded Successfully

# Running CPUtest1

# TIME PC INSTR ADDR DATA

# 1239.0ns 0000 JMP 003c zz

# 2039.0ns 003c JMP 0006 zz

# 2839.0ns 0006 LDA 1800 00

# 3639.0ns 0008 SKZ 0000 zz

# A HALT Instruction was Processed

# Break at cpu_test.v line 29

与功能仿真的结果相比,时序仿真的结果虽然有39ns的延迟,但系统的逻辑功能却未发生变化,这说明综合和布局布线带来的延迟并未导致系统功能的改变。

本设计选用的下载芯片为Altera公司FLEX 10K系列的EPF10K10TC144-4,它具有144个I/O引脚,其中可分配的有96个,内部具有576个逻辑宏单元。下载工具选择Quartus II,首先选择器件、分配管脚,然后执行全编译。全编译后会生成一些数据文件,其中扩展名为hex的是十六进制输出文件,它包含了布局布线后的器件、逻辑单元和管脚分配等编程信息。通过下载线将计算机的COM口与实验板的COM口连接起来,使用烧录工具将hex文件下载到EPF10K10TC144-4中。

4 结论

在实际的FPGA开发中,选用Modelsim + Synplify + Quartus II的EDA工具组合能很好地规划设计流程,充分利用各EDA工具的优点,提高开发效率。

本文作者创新点在于将FPGA开发过程中的多种EDA工具有机地结合在一起,并通过一个CPU的设计实例证明了利用多种EDA工具进行FPGA协同设计的可实现性。

责任编辑:gt

-

先进FPGA开发工具中的时序分析2022-06-28 1935

-

【下载】《FPGA设计指南:器件、工具和流程》2017-09-01 46186

-

勇敢的芯伴你玩转Altera FPGA连载8:FPGA开发流程2017-10-12 3397

-

华为FPGA设计流程指南2017-12-08 5226

-

FPGA开发工具有哪些?2018-09-27 15402

-

FPGA开发的完整的流程及开发过程中使用到的开发工具有哪些?2021-04-29 1876

-

Verilog HDL语言编程基础与FPGA常用开发工具2021-12-22 2042

-

Altera FPGA的选型及开发2012-08-15 1556

-

Altera Cyclone V FPGA和SoC FPGA虚拟目标开发工具荣膺EDN中国2012最佳产品奖2012-11-29 1718

-

Altera与风河公司建立战略合作关系 为Altera SoC平台定制操作系统和开发工具2014-02-10 3249

-

Xilinx-FPGA高级开发工具2016-09-01 1035

-

Altera功能安全锁步解决方案采用了FPGA、SoC,认证工具流程2018-08-31 1953

-

GRX IV FPGA开发工具包用户指南资料免费下载2018-11-22 1336

-

FPGA的开发流程以及它的适用场景2019-11-20 2421

-

Altera推出一系列FPGA软、硬件和开发工具2024-10-12 1737

全部0条评论

快来发表一下你的评论吧 !