ADC芯片对 LTCC 基板工作温度影响

处理器/DSP

描述

由于系统小型化要求,数字处理分机由原来的机箱缩小为一个表贴器件。通过选用裸芯片采用 SIP 封装的形式,把集成电路 ADC 芯片、ASIC、存储芯片和各类无源元件如电容、电感等集成到一个多层基板上。以现有混合集成技术为基础,主要研究器件装配工艺选择,对于关键器件,采用电磁仿真软件模拟装配方式对性能的影响。通过有限元仿真,分析芯片的散热需求;并详细探讨了基板材料对封装器件散热的影响。

引言

随着电子装备一体化需求,对分系统、模块的体积、质量提出了更高的要求,轻质化、小型化、系统化是未来的整机发展趋势。在微波技术领域中,以 MMIC、RFIC、LTCC、MEMS 等技术为主体,辅之以部分芯片离散元件,采用高密度的 MCM 技术,面向芯片内系统(SOC)和封装内系统(SIP),将微机电、数字电路、中视频 IC、射频和微波电路集成在很小的电路单元内,形成一个微系统,以实现微波前端变频和数字处理功能。

从形态上来看,微系统产品分两个层次。一是芯片集成微系统,指以系统架构和算法为核心,以先进微电子、光电子、微机械为基础,融合集成的集传感、处理、通信、执行、微型电源供电等功能一体的、具有某种系统功能的、芯片级规格的微小型系统,芯片集成微系统是微系统的高级阶段如图 1 所示;二是功能集成微系统,指以系统架构和算法为核心,以微电子、光学(或光电子)、MEMS/NEMS 等技术为基础,从系统工程的角度出发,通过跨学科多专业融合集成设计,采用 SoC/SiP 以及系统级封装集成制造,实现某种系统功能的微型或小型产品。功能集成微系统(如图 2 所示)能较灵活应用各种不同芯片资源和封装互连优势,优化系统性能,避免重复封装,可以缩短开发周期、降低成本并提高了集成度,是当今及今后较长时间的产品形态 。

图 1 芯片集成微系统

图 2 功能集成微系统

现以小型化数字接收机为例,产品由原来一个机箱大小的数字化接收机,通过小型化设计,整体缩小为一个具有同等功能的 SiP 封装表贴器件,长宽大小不超过 50 mm。设计上采用可寻的商业化芯片,自行设计专用芯片,把电路 ADC、ASIC 和无源元件如电容、电感集成到一个封装体内,实现数字信号处理功能。在有限的空间内,采用原有的混合集成器件加电缆集成的方式,体积上不满足要求。须采用多层基板加裸芯片集成的方式,本文重点对芯片集成和散热两方面考虑,研究芯片装配工艺。通过仿真软件 HESS、ANSYS 进行电、热性能仿真,根据仿真结果,确定芯片的装配方式,并选择适宜的基板材料,实现小型化数字处理器的装配工艺设计。

1 数字处理器封装工艺流程设计

根据数字处理器设计方案,以多层电路为布线基板,承担芯片物理载体和信号传输的功能。所有控制和信号在基板层内完成,芯片等元器件器件通过表贴、倒装和贴装集成在基板上。基于设计图纸,装配工艺流程设计如下:SMT 贴装→回流焊→芯片安装(粘接后引线键合 / 倒装贴片)→等离子清洗→丝焊→封盖→植球→回流焊→表面打标→测试→包装。该工艺流程中,芯片与基板间的装配,有倒装和贴装两种方案可选,其他工序由于无备选工艺方案,工艺流程可以确定下来。因此,该数字处理器工艺流程设计关键在于选择合适的芯片装配工艺方式。

目前,芯片有两种装配方式,倒装和贴装。两种工艺比较,倒装焊的芯片价格昂贵,采购困难,不适合小批量生产模式,该工艺的使用范围较窄。但是,倒装焊工艺相比贴装后焊线连接,在性能、布线和散热上具备如下优势:

(1)倒装焊技术无引线键合焊盘中心距极限的问题;

(2)在芯片的电源 / 地线分布设计上可以给电子设计师提供更多的便利;

(3)通过缩短互联长度,减小 RC 延迟,为高频率、大功率器件提供更完善的信号;

(4)封装面积小;

(5)热性能优良,芯片背面可安装散热器。

鉴于倒装在性能和散热两方面的优势,而 ASIC 芯片功耗为 40 W,有较高的散热性要求,倒装芯片焊接可利用芯片背面与散热板接触散热,ASIC 产生的热可在短时间内通过散热板导出封装外,可降低芯片节温,确保芯片长期稳定工作。另一方面,ASIC 与 ADC 信号传输接口有几百个,采用倒装芯片可以减小封装尺寸,缩短传输路径,减少信号延迟时间,提高芯片性能。因此,考虑性能和散热因素,ASIC 芯片最佳方案是采用倒装贴片的装配方式。

对于 ADC 芯片,功耗约 1 W,对散热需求不明显。性能方面,通过 HESS 仿真,分别计算 ADC 倒装和贴装两种装配方式,对高速信号的完整性影响大小。是贴装后焊接不同跨距互连金丝对性能的影响。通过插损和回损大小,判定芯片合适的装配方式。

ADC 芯片倒装焊接

ADC 芯片基板金丝互连

ADC 芯片与基板不同跨距金丝互连

仿真结果在 0~2 GHz 频段内,倒装贴片插损小,可以忽略不计,ADC 倒装焊电性能达到最佳。芯片贴装后,金丝键合的插损随着引线跨距增加而增大,当跨距达到 1.4 mm 时,插损为 -0.2 dB。在 0~2 GHz 频段内,倒装贴片回损小于 -50 dB,贴装芯片随着金丝互连跨距加大,回损增加,1.4 mm 金丝互连在 2 GHz 回损约为 -15 dB。该器件插损要求大于 -0.2 dB,回损小于 -15 dB。因此,小于 1.4 mm 跨距金丝键合,丝焊仍满足性能要求。在 2 GHz 频段内,ADC 芯片倒装贴片和引线键合均可满足要求,鉴于 ADC 芯片散热要求低,金丝互连对性能影响小,采用贴装工艺,可节约成本,提高产品可装配性,因此该芯片采用贴装后金丝互连的方式装配。

插损

回损

2 基板材料选择

基板是数字处理器的重要组成部分,在封装中实现搭载器件和电气连通的作用。由于该器件需要在母板上再次集成,基板在满足器件本身功能的前提下,还需与系统母板安装相匹配。本次基板的选择需满足芯片倒装工艺,又要兼顾 BGA 封装后与母板二次焊接。常用封装基板有有机系(树脂系)、无机系(陶瓷系、金属系)和复合机系三种,前两种材料在性能上各有优缺点,而复合机系综合了两者的优点,已经成为基板的发展方向,但是目前没有大规模应用。本次选用有机、无机基板作为封装材料为封装基板研究对象。

2.1 BT 封装

封装基板有机系材料,也统称的 BT 树脂。

BT 封装的优点:

(1)与 PCB 的热匹配性好,两种材料的 CTE 比较接近,因而热匹配性好;

(2)在回流焊过程中可利用焊球的自对准作用,即熔融焊球的表面张力来达到焊球与焊盘的对准;

(3)成本低;

(4)电性能良好。

BT 材料封装的缺点:对湿气敏感,不适用于有气密性要求和可靠性要求高的器件封装。

2.2 陶瓷封装

无机基板以陶瓷 LTCC 使用较广,多用于具有气密性高要求的封装中。

陶瓷封装的优点:

(1)气密性好,抗湿气性能高,因而封装组件的长期可靠性高;

(2)与 BT 封装器件相比,电绝缘特性更好;

(3)与 BT 封装器件相比,封装密度更高。

陶瓷封装的缺点:

(1)由于陶瓷基板和 PCB 的热膨胀系数(CTE)相差较大(陶瓷基板约为 7×10 -6 /℃,PCB 约为 17×10 -6 /℃),因此热匹配性差,焊点疲劳失效;

(2)与 BT 封装器件相比,封装成本高;

(3)在封装体边缘的焊球对准难度增加。

2.3 BT 和 LTCC 基板对芯片工作温度影响

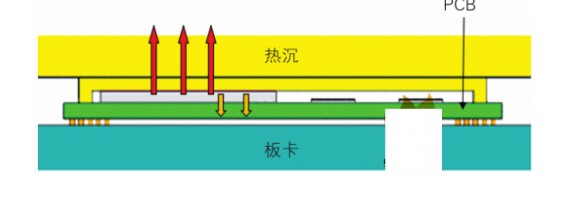

数字处理器 40 W 以上的功耗,仅通过基板焊带不能将大量的热及时传导出去,大功耗器件 ASIC 芯片需金属外盖接触,外盖表面贴着热沉,结构设计如图 8 所示,热沉上表面由 25 ℃的水冷系统进行冷却,对流换热系数为 578 W/(m 2 ·K)。金属盖板用密封焊料焊接在基板上,用以保护芯片、引线及焊盘。ASIC 芯片倒装后,芯片底面通过散热胶直接与金属盖接触,可以将大部分的热通过传导的 方式带出。其他表面为自然对流冷却,对流换热系数为 10 W/(m 2 ·K),环境温度为 85 ℃,ASIC 芯片的功率为 40 W,AD 芯片的功率为 1 W,闪存芯片的功率为 0.5 W。通过 ANSYS 软件仿真,计算使用两种不同基板时,对应芯片的工作温度。图 9 是 BT 基板和 LTCC 基板封装仿真热分布,ASIC 芯片(芯片 1)的温度范围为 105~118 ℃,ADC 芯片(芯片 2)的温度范围为 102~112 ℃ ,闪存芯片的温度范围为 100~105 ℃,芯片的最高温度位于 BT 封装的 ASIC1 底部中心位置,温度约为 118 ℃,其次为 LTCC 封装的 ASIC1 底部中心位置,温度约为 115 ℃。对比 BT 和 LTCC 基板封装,对芯片温度分布影响较小。

数字处理器热传导示意图

对比 LTCC 和 BT 封装,芯片工作温度的变化较小。其主要原因是 ASIC 大功率芯片上表面紧贴热沉,其产生的绝大部分热量往上耗散,形成了热耗散通路,大功耗芯片的热少量向基板方向传导。其它芯片如 ADC、存储芯片散热小,仅少量热会传给基板,本次基板散热性能的优劣对芯片散热的影响较小。因此,该数字处理器 SiP 封装基板材料两种均可选用,鉴于 BT 在 BGA 焊接方面的优势,在与母板焊接时,BT 基板的热膨胀系数更匹配,本次选用 BT 材料作为封装基板。

3 结论

本文以现有混合集成技术为基础,主要研究在系统小型化过程中,关键芯片的封装工艺,并采用电磁仿真软件模拟倒装和贴装两种装配方式对性能的影响。且通过有限元仿真软件,分析芯片的散热需求,并探讨 BT 和 LTCC 作为基板材料对该结构数字处理器散热的影响。为后期小型化工艺设计指明了研究方向,是一次有效的 SIP 封装的工艺探索。目前,在国内 SiP 技术尚属于初级阶段,随着 SiP 技术逐步成熟,必将成为电子技术新热点和技术应 用的主要方向之一。而 SiP 封装工艺作为 SiP 封装技术的重要组成部分,值得花费力量从事相关技术研究。

责任编辑:pj

-

工作温度范围2019-04-16 3073

-

LTCC电子器件的模块化2019-07-09 2779

-

芯片的工作温度是指芯片的发热温度嘛,还是指环境温度呢?2019-08-09 14984

-

怎样去计算电源芯片的工作温度呢2021-12-27 1678

-

怎样使用温度传感器和ADC去测量芯片的工作温度呢2022-01-25 1931

-

LTCC多层基板2010-07-26 995

-

倒车雷达的工作温度2010-01-04 1786

-

LTCC基板密集孔区域研究2018-04-13 1413

-

基于stm32f429,利用内置温度传感器和ADC外设,测量芯片工作温度2021-11-30 1086

-

电源芯片工作温度的计算2022-01-05 1101

-

LTCC基板关键工艺问题解决方案2022-12-16 2624

-

芯片的温度之结温和工作温度的区别分析2023-05-14 38463

-

IC长时间工作温度多少合适?2023-11-29 3890

-

如何降低变换器的工作温度2024-08-14 1533

-

锌银电池工作温度_锌银电池结构2024-10-03 2503

全部0条评论

快来发表一下你的评论吧 !