逐次逼近式AD转换器AD7492的性能特点和应用电路分析

模拟技术

描述

1 概述

AD7492是AD公司推出的12位高速、低功耗、逐次逼近式AD转换器。它可在2.7V~5.25V的电压下工作,其数据通过率高达1MSPS。它内含一个低噪声、宽频带的跟踪/保持放大器,可以处理高达10MHz的宽频信号。

AD7492 很容易与微处理器或DSP接口。输入信号从CONVST的下降沿开始被采样,转换也从此点启动。忙信号线在转换起始时为高电平,810ns后跳变为低电平以表示转换结束。没有与此过程相关的管线延时。转换结果是借助标准CS和RD信号从一个高速并行接口存取的。

AD7492采用先进的技术来获得高数据通过率下的低功耗。在5V电压下,速度为1MSPS时,平均电流仅为1.72mA;它还可对可变电压/数据通过率进行管理。在5V供电电压和500kSPS数据通过率下的消耗电流为1.24mA。

AD7492具有全部休眠和部分休眠两种模式,采用休眠模式可以在低数据通过率时实现低功力量。在5V电压时,若速度为100kSPS,则平均电流为230μA。AD7492的模拟输入范围为0~REF IN。另外,该器件内部还可提供2.5V参考电压,同时,该参考也对外部有效。器件的转换速度由内部时钟决定。AD7492的主要特性如下:

●额定电压VDD为2.7V~5.25V;

●高数据通过率:数据通过率为1MSPS;

●功耗低:在5V电压下,数据通过率为1MSPS时,功耗一般为8.6mW;

●输入频带宽;100kHz输入时,信噪比为70dB;

●具有片内+2.5V参考电压;

●具有片内时钟振荡器;

●具有可变电压/数据通过率管理功能,转换时间由内部时钟决定。有部分和全部两种休眠模式,采用休眠模式可在低数据通过率时使效能比达到最大;

●带有高速并行接口;

●具有柔性数字接口。通过设定VDRIVE引脚可控制I/O引脚上的电压;

●休眠模式的电流一般为50nA;

●无管线延时。是一个标准的逐次逼近式AD转换器,可在采样瞬间精确控制,采样瞬间借助于CONVST的输入和间隔停止转换来控制;

●外围元器件较少,可优化电路板空间;

●采用24引脚SOIC或TSSOP封装形式。

2 引脚功能

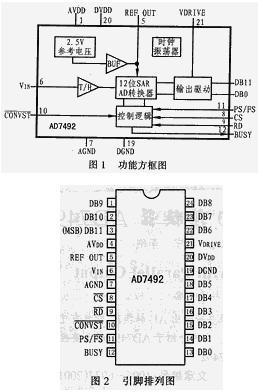

图1所示为AD7492的功能框图。图2为其引脚排列。各引脚的功能如下:

CS:片选引脚。在CS和RD下降沿之后,系统把转换结果放在数据总线上。由于CS和RD连接在输入端的同一个与门上,因此信号是可以互换的。

RD:读信号输入端。通常连接到逻辑输入端,以读取转换结果。若数据总线总是处于工作状态,则在忙信号线变为低电平之前将新的转换结果送出去,在这种情况下CS和RD可通过硬件方式连至低电平。

CONVST:启动转换输入信号端。跟踪/保持输入放大器在CONVST的下降沿处从跟踪状态转换为保持状态,同时启动转换过程。转换建立时间可短至15ns。如果 CONVST在转换持续期间处于低电平,且在转换结束时仍保持低电平,器件将自动进入休眠状态。休眠状态的类型由PS/FS引脚决定。若器件处于休眠状态,CONVST的下一个上升沿将唤醒它。唤醒时间一般为1μs。

PS/FS:休眠模式选择端。器件进入休眠状态时,此引脚决定休眠的类型。在部分休眠模式下,内部参考电路和振荡电路不断电,耗电大约200μV。在全部休眠模式下,所有模拟电路均断电,此时器件的功耗可以忽略不计。

BUSY:忙信号输出端。此引脚的逻辑输出表明器件所处的状态。在CONVST下降沿之后,忙信号变为高电平并在转换期间保持高电平。一旦转换结束,转换结果存入输出寄存器,忙线复位为低电平。在忙信号下降沿之前,跟踪/保持放大器转为跟踪状态,忙信号变为低电平以开始跟踪。在忙信号变低时,若CONVST输入仍为低电平,则器件在忙信号上降沿自动进行入休眠状态。

REF OUR:2.5V±1%参考电压输出。

AVDD:模拟电源端。

DVDD:数字电源端,2.7~5.25V。用于给AD7492器件内除输出驱动电路和输入电路外的所有数字电路提供电源。

AGND:模拟地。

DGND:数字地。

AGND和DGND理论上应处于同一电位,即使在有瞬变电流时,其差值最大也不可超过0.3V。

VIN:模拟输入端。单端模拟输入路线。输入范围为0V~REF IN。此引脚为直流高阻抗。

VDRIVE:输出驱动电路和数字输入电路的供电电源为2.7V~5.25V。此电源电压决定数据输出引脚的高电平电压和数字输入的阈值电压。当数字输入和输出引脚阈值电压为3V时,VDRIVE允许AVDD和DVDD在5V电压下工作(使ADC的动态性能最优)。

DB0~DB11:数字线0~11位。器件的并联数字输出。这是由CS和RD控制的三态输出。它们的输出高电平电压是由VDRIVE引脚决定的。

3 应用接口电路

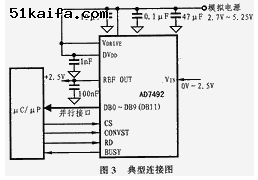

图3 为AD7492的一个典型连接图。一旦CONVST变为低电平,忙信号就变为高电平,在转换结束时,忙信号的下降沿用于激发一个中断服务。由CS和RD线控制并读取12字节。内部2.5V参考电压使AD7492成为0~2.5V的模拟输入、单极性AD转换器。REF OUT引脚需并联一个不小于100nF的电容器,以使基准电压保持稳定。因为第一闪转换可能会有误差,建议剔除第一次转换结果。这样也可以保证各部分处于正确的转换状态。上电时,不能变动,否则CONVST的上升沿可能会叫不醒器件。

图3 中,将VDRIVE引脚与DVDD相连是为了确定逻辑输出的电平值为0或DVDD。加在VDRIVE的电压可确定输入和输出逻辑信号的电压值。如果 DVDD连接5V电压而VDRIVE连接3V电压,则对应逻辑0和1的电压为0V和3V。这些特性使得AD7492能以3V的阈值电压使A/D在5V下运行。

责任编辑:gt

-

高性能低功耗12位并行ADC——AD7492的深度解析2026-04-02 162

-

逼近型模数转换器特点和应用2024-07-22 1896

-

逐次逼近型A/D转换器的工作原理和特点2024-05-21 4873

-

逐次逼近型A/D转换器的基本原理2023-10-01 3669

-

高性能全集成逐次逼近寄存器型模数转换器2022-10-31 695

-

EVAD7492 AD7492 评估板2021-05-29 782

-

基于Nios驱动的AD7492的BeMicro FPGA方案2021-05-16 1436

-

高速率的逐次逼近模数转换器ADS8412是如何设计的?2021-04-14 2234

-

A/D转换器的特点2019-05-27 2640

-

请问AD7492噪声怎么解决2019-01-24 2449

-

逐次逼近AD转换器电路图2009-03-21 1740

-

AD7492中文资料 (12位并行输出AD转换器)2008-08-06 3088

-

逐次逼近式A/D转换原理2006-01-01 4435

全部0条评论

快来发表一下你的评论吧 !