基于DSP器件实现高速铁路新型轨道信号模拟系统的设计

处理器/DSP

描述

铁路信号的主要任务是保证行画安全,提高运输效率。随着铁路运输向重载、高速、高密度方向发展,对直接指挥和控制列车运行机的铁路信号提出了更高的要求。各国铁路,特别是发达国家铁路积极引进和采用新技术,加大研发力度,推动高速铁路信号的发展。

我国目前运用的轨道信号主要是交流计数信号(解调是境大于4s,且抗干扰性能很弱)、移频信号(频点设置不合理,不满足正交条件,占用频带宽,且抗干扰性能很弱,大部分频率解调难度大,解调时间长,存在倍频信号的隐患)、UM71信号、ZPW2000A信号(频点不满足正交条件,16.9HZ以下的调制频率的调制系数大,对上下边频的漂移敏感,存在倍频的隐患)、数字编码信号(设备复杂昂贵,解调时间2.5s-3.0s)。但这些轨道信号存在的缺点,导致其完全不能适应当前国内高速铁路的需要,因此急需研制新型国产轨道信号系统。新型轨道信号必须适应列车提高运行速度和运行密度的需要,适应重载运输的需要,适应电气化铁路发展的需要。同时还不能脱离现在的基础,要尽量利用现有的轨道电路信道,即在现有轨道电路的基础上设计新型轨道信号。为此本文讨论了自主开发的适应于高速铁路的改进型数字编码信号和正交化FSK信号,并研究了一套能够模拟以上两种高速铁路信号发送和解调过程的硬件平台。

1.系统分析

通过对原有的铁路轨道信号进行国产化改进,提出了适合中国高速铁路和改进数字编码和正交化FSK信号,并开发了以TMS320C6722浮点DSP为数据处理核心的高速铁路信号的发送和接收模拟系统。该系统为通用型系统,不但可以实现改进型数字编码和正交化FSK信号的发送和解调,而且预留了更多的扩展接口,可以应用于研究创新实验。

本系统按其主要功能分为信号发送和信号解调两部分,系统的整体结构如图1所示。

1.1信号发送单元

信号发送单元主要实现信号的产生和发送,同时还可在信号中混入噪声,进行实际轨道信号的模拟。信号发送由上位机控制,上位机选择发送信号的幅度、载频、调制频率等参数,并选择是否添加噪声,然后通过USB传输到硬件系统控制DDS发码单元发送相关制式铁路信号。在发送过程中,上位机界面可以实时显示信号的发送参数和相应波形。

1.2信号解调单元

信号解调单元负责接收信号,对其进行时域和频域分析。通过对载频信息的检测完成对各种制式的确定,然后按照不同制式的解调算法进行解调。信号解调过程首先由A/D采集DDS发送的轨道信号,然后采集数据送人DSP处理器,DSP判断信号制式进行相应解调,解调后的数据通过双口RAM送人ARM协处理器,ARM控制液晶显示信号制式、载频、调制频率等,并通过USB传输解调信息到上位机实时显示。

2.系统硬件分析

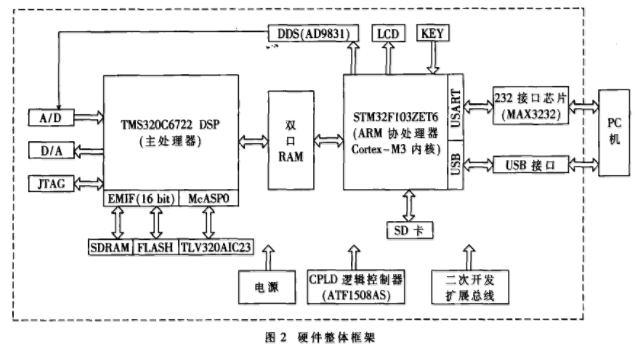

系统的硬件整体框架图如图2所示。

2.1双CPU单元

采用TI公司的浮点DSP处理器TMS320C6722作为整个系统的核心,应用其出色的运算能力和数据处理速度快、精度高等优点,完成系统的数据处理任务。控制单元采用CORTEX-M3为内核的ARM芯片STM32F103ZET6作为核心,其强大的控制能力,满足了整个系统的控制要求;其丰富的外设配置,为系统的扩展和升级提供了很大的空间。

2.2主要外围电路单元

DDS发送单元以AD9831为核心,配合相应算法及程序发送正交化FSK信号和数字编码信号。由于AD9831频率寄存器切换选择线(FSELECT)需由定时器的输出脉冲控制,以实现多频之间切换,而DSP芯片定时器未设置定时器的外部引脚,故DDS的控制由协处理器STM32F103ZET完成。

信号采集单元以MAX1322为核心,通过并行数据线与TMS320C6722相连,AD_E0C#连接C6722的外部中断引脚,读写及片选由CPLD逻辑译码产生。

2.3通信单元

系统中DSP和ARM之间采用双口RAM(IDT70V24)通信。该芯片配有两套完全独立的数据线、地址线、读/写控制线,允许主从控制器对双端口存储器的同一单元进行同时存取。两套完全独立的中断逻辑用来实现两个CPU之间的握手控制信号;两套独立的“忙”逻辑,保证两个CPU同时对同一单元读/写操作的正确性;读/写时序与普通单端口存储器完全一样,存取速度完全适合高速、实时的通信系统。

PC和ARM之间采用USB或RS-232串口通信。

2.4 CPLD模块

采用ATMEL公司的CPLD芯片ATF1508AD完成对整个系统的时序控制和硬件接口逻辑。它可以把DSP芯片进一步解放出来集中完成数据处理工作,提高DSP芯片的使用效率;它还实现复位控制、输出时钟的功能。

3.轨道信号的改进方案

如果以目前的轨道电路为基础对现有铁路轨道信号进行改进,将大大降低改造成本,而且改造容易,可以迅速普及。以下提出的方案基于目前的轨道电路。

3.1正交化高速高可靠轨道信号

FSK信号是用数字调制信号的正负来控制载波的频率,即频移键控信号。目前国内使用的UM71轨道信号,虽然有占用频带窄、不容易受到干扰、解调相对容易、反应时间快等优点,但是其调制频率的设置仍不满足正交条件,16.9 Hz以下调制频率的调制系数偏大,对上下边频的漂移敏感,也存在倍频信号的隐患,UM71频谱集中在中心载频附近,当调制频率较低时,调制系数偏大,尤其是10.3 Hz时,其能量分布除了在中心载频处有最大值外,它的次高谱线、次次高谱线处的能量也较大,不利于解调的可靠性。针对这些缺点,对其进行正交化改造。

根据最佳接收系统的条件,如果移频键控信号FSK的两个频率IL和`满足相互正交,则该信号系统的接收检测可以达到最佳,进而保证系统的可靠接收,提高系统的稳定性。通过推导可证明FSK信号的正交条件为两频率之差是其调制频率的整数倍。由FSK信号的频谱可知,其谱结构是以载频为中心、以调制频率为间隔的离散谱。因此调制频率越小,谱线越集中,信号频带越窄。正交化轨道信号采用调制系数0.5,不仅可以得到较窄的带宽,还有很好的功率谱结构,方便可靠解调。改造方案大体如下:

(1)采用原ZPW2000A信道,载频设置上行2 000 Hz、2 600 Hz,下行1 700 Hz、2 300 Hz。这样可以利用原轨道电路。

(2)调制频率设置满足正交性,且正交系数为1,调制系数0.5。

(3)不同的调制频率对应不同的频偏,形成自适应频偏体系。

(4)特征谱一次边频分量的相对幅度为l/3。

(5)避开了50 Hz的谐波干扰。频带控制在正负40 Hz以内。

(6)调制频率的选择避免倍频的可能。

(7)解调速度提高到0.4 s~0.6 s。

所以将调制频率设计为从1* Hz~31.6 Hz,间隔为0.8 Hz递增,避开了倍频的可能,从而可以增加到20个调制信号。

3.2新型数字编码信号

TVM430数字编码信号有27个信息位,信息量远高于国内原有轨道信号。但是其最大缺陷在于信号解调周期长,信号可靠确定时间长,大大超过国产移频信号和UM71信号。此外该轨道信号系统运行成本昂贵,性价比低,且应用中信息位存在冗余,理论上若信息位降低,解调周期必定会减少。针对以上问题,对TVM430信号进行国产化技术改造,在保证信息量的同时降低信息位,使之成为一种具有较高信息传送能力、解调周期短、适合中国国情的数字轨道信号系统。

经过对铁路现场的调研和分析,提出了改进方案。改进的TVM430数字编码信号被命名为新型数字编码信号。新型数字编码信号在满足我国铁路的实际情况的前提下,相比于原信号减少了低于4.08 Hz的低频信息,从而提高了信号的抗干扰能力和解调速度。新型数字编码信号去掉了路网码,信息位共20 bit,其中坡度码3bit、闭塞分区长度码4 bit、速度码5 bit、循环冗余校验码6 bit、奇偶监督码1 bit、占用码1 bit。1 bit奇偶监督码专门用于速度码的检测。为了提高解调速度,在不同的信息码之间添加0码,即不同信息码连接处的频率间隔为1.28 Hz。载频沿用TVM430信号的1 700 Hz、2 000 Hz、2 300 Hz、2 600 Hz四个载频。

4.系统主要软件设计

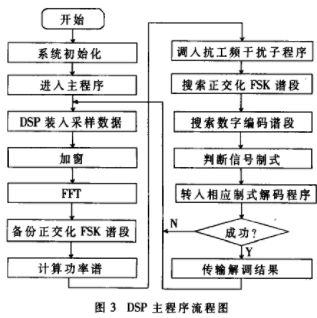

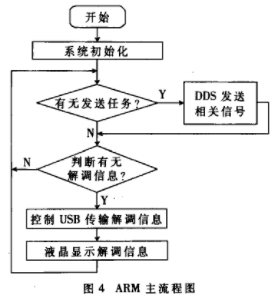

本系统软件设计主要包括:系统的整体控制、正交化FSK信号的发送和解调、数字编码信号的发送和解调。铁路轨道信号发送和解调过程主流程图如图3、图4所示。

4.1正交化FSK信号发送与解调

4.1.1信号的发送

上位机控制界面选择要发送信号的各项参数,包括制式、载频、调制频率、频偏等,通过USB传输信号信息发送到ARM,ARM根据信号信息设置定时器参数,发送DDS频率参数,完成FSK信号的发送。

4.1.2信号的解调

正交化FSK信号的解调过程中,采用了频域解调方法。频谱识别法能准确直观地找到特征功率谱,从而得出载频和调制频率。在正交化FSK信号中,调制频率和频偏存在倍数关系,可通过载频和调频计算出上下边频,即上下边频=载频+调频/2。

4.2新型数字编码信号发送与解调

4.2. 1信号的发送

新型数字编码信号码字共19 bit,该信号是由多个低频信号叠加形成的多音频调制信号,信号频谱中有很多的交叉调制项,通过DDS发送时,采用调相的方式实现。首先根据数字编码信号的特点建立相位表,然后初始化ARM的定时器,设置ARM定时器的中断频率为16 384 Hz。当每次中断发生时查表将相位表中的一个值写人AD9831的相位偏移寄存器,重复发送相位表的值即可完成信号的发送。

4.2.2信号的解调

解调方法采用脉冲解调原理。根据数字编码信号的特点,其频谱以载频为对称轴,载频两侧有两条占用码形成的对称的谱线,这三条谱线在频谱中幅值较大。根据这一特征,对采样信号求功率谱,找出其中的五条幅值较大的谱线按频率排序,然后按照相应规则判断载频是否存在。如果存在则继续解调,否则重新采样。原信号通过高通滤波器后量化处理,在幅值正过零处形成脉冲序列,低通滤波后得到调制信号。对调制信号加Hammlng窗截断后进行FFT变换,就得到了调制信号的频谱结构。新型数字编码信号的调制频率的间隔为0.64 Hz。为了能准确地识别出不同的调制频率,采用了ZFFT技术得到0.031 25 Hz的频谱观察分辨率。得到的低频信息还需进行CRC校验以检测解码的正确性。CRC校验的优先权高于奇偶校验,若CRC校验不通过,再对速度码进行奇偶校验,如果速度码正确,则对信息码循环纠错,直到通过CRC校验,解码结束。

4.3 USB通信设i十

本系统的USB通信部分实现ARM和上位机之间的通信。系统采用全速USB2.0标准进行批量数据传输。STM32F103ZET自带USB2,0全速设备外设固件接口,即USB固件库。可以用此库进行USB宏单元简化开发。通过USB的高、低优先权中断处理函数USB_HPI()与USB_LPI(),响应相关的批量传输中断。

4.4上位机软件设计

由于所发送信号参数复杂,如果用硬件实现信号的发送控制,必将造成面板设计复杂,而且显示的信息量也不多,因此采用PC机作为主控制端,在PC上用Borland C++Builder 6开发相关发送、接收界面。

基于TMS320C6722 DSP浮点处理器的轨道信号模拟系统,能够模拟高速铁路信号的发送和解调过程c该系统在实现轨道信号的实时发送过程中,能够随时添加单频干扰或双频干扰。本系统经过测试,性能稳定,解调结果正确,各项指标符合铁道部要求,达到了预期的要求。该系统可为国内高速铁路信号系统提供可行的解决方案,也可为教学和实验提供演示,具有很好的应用前景。

责任编辑:gt

-

浅析加速度传感器在高速铁路中的应用2014-07-15 2089

-

【TL6748 DSP申请】高速铁路机车调配运营平台2015-09-10 1389

-

传感器在高速铁路中的应用与研究2018-11-01 2447

-

高速铁路无线网络的覆盖解决方式2019-07-12 2629

-

高速铁路综调系统中消息传递的研究2009-07-01 767

-

大唐移动TD-SCDMA高速铁路解决方案2009-12-19 891

-

传感器在高速铁路的测速和定位技术中的应用2010-10-14 5213

-

高速铁路实现机车信号主体化方案2011-03-21 762

-

高速铁路分步建设WCDMA网络方案介绍2018-11-07 3152

-

射频识别芯片助力高速铁路设计2019-08-10 918

-

高速铁路电力系统基本知识2021-09-23 1242

-

RRH 6200M:低噪音、高速铁路到铁路站点的数据表 ADI2023-10-08 85

-

构建高速铁路安全在线监测预警系统解决方案2024-09-10 878

-

高速铁路安全预警系统的功能优势2024-09-24 951

-

高速铁路预警系统:守护安全,预防自然灾害的坚实盾牌2024-10-18 829

全部0条评论

快来发表一下你的评论吧 !