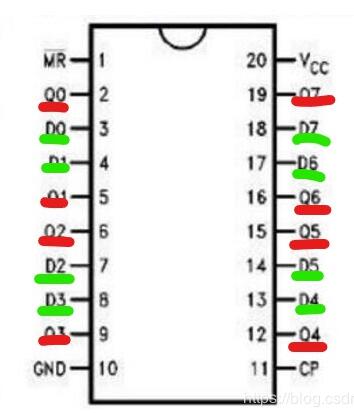

74LS273引脚图和工作原理

芯片引脚图

730人已加入

描述

74LS273是8位数据/地址锁存器,它是一种带清除功能的8D触发器,D0~D7为数据输入端,Q0~Q7为数据输出端,正脉冲触发,低电平清除,常用作数据锁存器,地址锁存器。

(1)1脚是复位/MR,低电平有效,当1脚是低电平时,输出脚2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部输出0,即全部复位。

(2)当1脚为高电平时,11(CP)脚是锁存控制端,并且是上升沿触发锁存。。当11脚有一个上升沿,立即锁存输入脚3、4、7、8、13、14、17、18的电平状态,并且立即呈现在在输出脚2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)上。

(3)74ls273其它管脚功能:1D~8D为数据输入端,1Q~8Q为数据输出端,正脉冲触发,低电平清除,常用作8位地址锁存器。

74LS273的工作原理

1脚是复位端,11脚是时钟(脉冲)输入端;当1脚为L电平时,无论有无脉冲,数据端(D端)是H或L电平,输出端(Q端)都为L电平;仅当1脚为高电平(H)时,“D”端的数据在脉冲的上升期间被传送到“Q”端。

第一脚WR:主清除端,低电平触发,即当为低电平时,芯片被清除,输出全为0(低电平);

CP(CLK):触发端,上升沿触发,即当CP从低到高电平时,D0~D7的数据通过芯片;为0时将数据锁存,D0~D7的数据不变。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

74ls160引脚图及功能真值表介绍2022-05-25 179116

-

74LS273触发器是如何工作的2021-11-01 4875

-

74LS273是什么2021-07-29 2905

-

74ls165中文资料汇总(74ls165引脚图及功能_工作原理及应用电路)2018-05-08 79317

-

74ls273应用电路图大全(七款74ls273串行显示/共阳LED数码显示/端口扩展电路)2018-04-28 25215

-

74ls273中文资料汇总(74ls273引脚图及功能_工作原理及应用电路)2018-04-26 190632

-

74ls07引脚图及功能_74ls07工作原理2018-04-04 85640

-

74ls164内部结构及其应用(74ls164引脚图及功能_工作原理)2018-01-27 113449

-

74LS273与74LS373的区别2017-11-07 20751

-

地址锁存器--74LS2732009-03-14 5548

-

74ls273 proteus仿真(含dsn仿真文件)2008-10-06 2189

-

74ls373引脚图2008-03-16 11509

-

74ls04引脚图 引脚功能2007-11-29 76600

全部0条评论

快来发表一下你的评论吧 !