基于复杂可编程逻辑器件实现雷达采集系统的设计

可编程逻辑

描述

1 引言

雷达高度表在飞机和导弹等的惯性导航和地形匹配导航中有着广泛的应用。雷达高度表是雷达向地面发射无线电电波,根据其反射回波的滞后时间来测量距离,用来取得距离地面的相对高度的一种装置。另外通过对雷达回波的分析处理可以了解地形情况。由于机载弹载雷达的外场试验组织实施难度大,试验费用昂贵,而且随着对雷达技战术指标要求的提高,对雷达测试设备提出了更高的要求。例如要求系统的数字化小型化,要求系统具有独立性和灵活性等,而且为了不丢失数据,测试设备应当能够连续长时间的纪录雷达的状态和信号。

CPLD(复杂可编程逻辑器件)具有可编程性和实现方案容易改动的特点,可以极大的降低系统开发成本和缩短开发周期,而且易于实现系统的集成化小型化。Altera公司的CPLD器件具有布线能力强,延迟可预测等优点,适合于完成各类算法和组合逻辑。其MAX系列器件性价比高,传播延迟小,逻辑资源丰富,电路设计简单等特点使其特别适合用作逻辑控制电路控制。硬盘作为存储介质具有很高的容量价格比,且易于扩充,数据利于转存和后期数字处理。普通IDE硬盘受限于总线速率,其持续数据传输速率在15MBps左右。目前15000转的小型计算机系统接口SCSI(Small Computer System Interface)硬盘,总线数据传输速率为80-320MBps,持续数据传输速率大于40MBps,性能远远高于IDE硬盘。鉴于此,雷达高度表数据采集存储系统设计采用可编程逻辑器件和总线技术,利用高速SCSI硬盘作存储介质,并且脱离微机平台,实现了雷达信号的灵活采集和连续存储。

2 系统结构

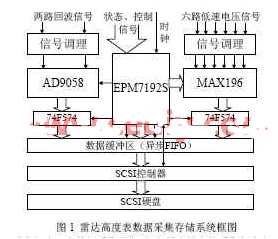

整个系统结构如图1所示。系统需要记录两路雷达脉冲回波信号,六路雷达状态信号(为缓变电压信号,输入幅度不同),以及雷达系统同步脉冲和雷达信号波门之间的时间间隔。要求采集脉冲回波信号时采集起点可选为信号波门前沿或同步脉冲后延迟一定时间,且延迟时间手动可调(调节范围5~200us),采样频率可调。要求存储数据具有固定的帧结构,利于事后分析处理。

两个同步脉冲之间为一个数据采集周期:根据用户设定的采集起点和采样频率采集一定点数的回波信号,计算目标距离,采集六路中速电压,将上述数据按照一定的格式打包,加上帧标志后组成一帧数据,送入数据缓冲区,等待SCSI控制卡将数据写入SCSI硬盘。

3 系统的设计和实现

3.1数据采集电路

数据采集电路分高速和低速两个部分。两路雷达回波信号采用高速数据采集电路,模数转换器采用美国AD公司生产的AD9058双路模数转换器(ADC)。AD9058在片内集成了两个独立的高性能并行8位ADC,其单路最高转换速率可达50MSps,模拟带宽达175MHz;每个ADC有单独时钟及参考电压输入;AD9058本身带有高稳定的2V电压参考源,可大大简化电路设计;其数字地和模拟地分开,有利于设计优秀的接地方案以消除干扰。

由于低速电压有六路需要采集而且输入幅度不同,但是要求的采样率较低,只需每个采集周期采样一次即可,所以低速数据采集电路采用了MAXIM公司的MAX196。MAX196为6路12位可编程ADC,每路模拟输入幅度程序可控,最高输入时钟2MHz,满足系统要求。

为产生高精度、高稳定度、低噪声、低抖动的系统时钟,时钟分系统采用高精度低相噪的温补、时钟分路器、分频器以及ET转换(PECL电平到TTL电平的转换)和TE转换(TTL电平到PECL电平的转换)来设计完成。高精度晶振作为时钟源,输出的纯净时钟信号送到高精度单端转差分时钟芯片,输出PECL差分信号经分频和变换后用作高速采集电路的采样时钟,时间延时的计数时钟。PECL信号和器件在良好匹配的情况下其信号速度、对外辐射、器件延迟以及输出信号抖动有着TTL和CMOS器件所无法比拟的优势,是设计高速数据采集系统时钟电路的理想选择[3]。

3.2逻辑控制电路

逻辑控制需要使用外部提供的同步和波门信号,这两个信号的优劣直接关系到系统逻辑的正确性和时间延时计数的准确性。对同步、波门信号调理的关键是将十几伏的模拟脉冲衰减到5伏以下,并保证衰减器与输入阻抗的匹配,避免信号反射。信号衰减后,送入高速比较器,获得TTL脉冲信号。由于采用高速比较器,调理后信号的上升和下降时间要比调理前模拟脉冲信号小得多,小于4ns。信号上升和下降沿的改善提高了CPLD的对信号脉宽、脉冲间隔的测量精度,为AD转换和时间延时计数提供了一个准确的时间起点。

在本系统中,ADC采集结果缓存采用多体存储结构,将存储器芯片分为多个体,各体之间并行工作,从而满足系统对数据存储速度的要求。另外,SCSI硬盘的直接读写主要有SCSI硬盘适配器通过DMA方式法完成。由于SCSI硬盘在寻找扇区的过程中有2~9ms的间隔,在这段时间内不能对SCSI硬盘进行读写。为了保证数据的连续计录和回放,必须有足够深度的数据缓存,因此在设计中采用两级缓存方式。在系统中,由AD转换电路送出的两路高速数据流,被存入到两个缓冲锁存器中,接着又被并行写入到两个高速异步FIFO中,这样FIFO的平均写周期为AD转换电路数据更新周期的1/2,从而可使用相对低速的芯片来满足系统要求。另外多路模拟信号采集后,不同速率的数据流要按一定顺序,一定格式打包成帧,进行SCSI硬盘存储,同时保持数据流的连贯。所有高速、低速的数据流要通过一个SCSI控制器进入SCSI硬盘或硬盘阵列大量数据存入硬盘,为了便于软件处理,数据应当有一定格式,组成帧结构。因此采用时序和控制逻辑电路协调多路模拟信号采集,进行总线隔离控制、FIFO读写控制等。

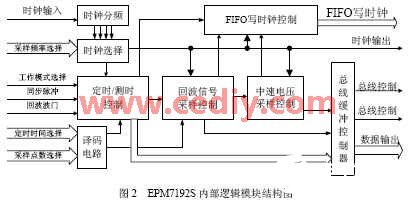

由于本系统控制逻辑的复杂性和使用的输入输出管脚较多,因此选择了Altera公司MAX7000系列中容量较大的EPM7192SQC160[4]。设计采用模块化设计,每一个子控制模块生成子模块后组成整个完整的系统。这种设计方法极大地提高了设计效率,并且有利于阅读和修改。控制核心EPM7192S内部逻辑模块结构划分如图2所示。

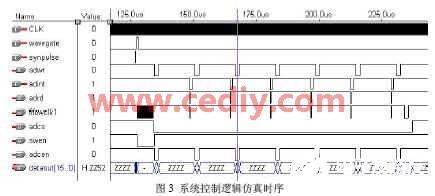

其中定时/测时控制模块完成采集起点控制和时间间隔记录;回波信号采样控制模块完成按照用户设定的采集起始点、采样频率和采样点数采集回波信号;中速电压采样控制模块完成每个采集周期内对MAX196写入6次控制字和读取数据转换的数据;FIFO写时钟控制模块提供数据存入缓冲区(异步FIFO)所需的写入时钟;总线缓冲控制器完成CPLD,高速A/D,低速A/D,FIFO间的数据交换。设计时采用同步电路设计,使用一个时钟作为全局时钟,最后实现的系统控制逻辑时序波形如图4所示。图中仅列出了完成一帧数据采集存储所需的几路关键信号:fifowclk1为异步FIFO的写信号,swen为高速A/D数据锁存器的输出使能信号,adcen是中速A/D控制字的输出使能信号。

3.3软件设计

事后分析软件主要负责将存放在SCSI硬盘中的测量数据通过SCSI转接卡,利用动态链接库转存到微机内存,显示并分析测量数据。事后分析软件首先寻找到存储数据的SCSI硬盘,依次读取所有存储数据文件属性,包括文件大小、存储时间、在SCSI硬盘中的初始扇区和终止扇区以及文件句柄等,并将采集数据文件名列出,供用户选择。用户选出要显示分析的文件,事后分析程序从中读取一定数量的测量数据到缓冲区,并连续寻找两个数据帧头,将两个帧头之间的数据经过一定处理后显示出两路雷达回波波形、同步信号和波门信号之间的时间间隔、6路中速电压值以及采集时设置的参数。

4 系统测试与应用

系统性能测试主要分两部分。首先是对多路模拟信号数据采集的测试,包括转换有效位数、谐波失真等。其次是测试SCSI硬盘数据存储的正确性和持续存储速度。

模数转换性能测试是对系统的静态和动态性能的测试,主要包括信噪比、总谐波失真、信噪失真比和有效位数的测试。实际的ADC存在噪声和失真,从而影响了ADC的实际分辨率,降低了ADC的位数,ADC实际可达到的位数称为有效位数[3]。采用FFT相关频谱分析方法对本系统进行了测试。选择DOFED &SCHWARZ DIGITALUHR CLOCK 铯原子时钟输出5MHz纯正正弦信号作为模拟输入,采样时钟来自系统板上晶体,对分辨率八位的ADC,采样的点数选择为1024点,采样频率是40MHz,频谱分辨率为0.125MHz。故此时满足相关采样的条件,采样为相关采样,根据采集数据和相关公式计算,最后测试结果表明ADC有效位为7.16bit,谐波失真约为44.92dB。

对高速数据流直接SCSI硬盘存储性能测试使用的是Seagate公司生产的ST336752LW型硬盘。测试时,在连续、高速存储过程中,监测异步FIFO的空满标志。若FIFO出现空标志有效的状态,表明SCSI硬盘持续存储速度高于数据流的速度;若FIFO出现满标志有效的状态,则表明数据流的速度高于SCSI硬盘持续存储速度,即表明系统不具备该速度的持续存储能力。测试表明,在单个SCSI硬盘、数据流速度在30MBps的情况下,没有出现FIFO满标志有效的状态,系统具备最高36MBps持续存储能力。另外,对确知数据流的存储数据进行了对比测试,通过近2G字节数据的比对,没有发现错误的数据,表明该系统的高速持续存储具有很高的可靠性。

本系统先后应用于多种雷达系统测试分析和外场试验,有效地记录和分析了雷达系统的动态特性、目标回波特性及干扰特性。特别是在机载雷达外场试验和雷达抗干扰试验中,获得大量以往难以连续记录的雷达中频回波信号。并且大大提高试验测试效率,节省大量的实验时间和费用,具有很高的经济效益。本系统采用模块化设计,采用CPLD器件和总线技术,缩短了开发周期,提高了系统集成度和稳定性。系统采样点数、采样频率、采样起始时刻可以灵活设置,可以脱离微机环境独立使用,能够广泛地应用于各种雷达测试、雷达目标和环境特性分析、雷达外场试验和验收鉴定。

责任编辑:gt

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4568

-

可编程逻辑器件测试2023-06-06 1301

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 2248

-

可编程逻辑器件(书皮)2022-07-10 784

-

PLD可编程逻辑器件2021-07-22 2319

-

求一种基于复杂可编程逻辑器件的硬件校正实现方案2021-04-28 1889

-

采用复杂可编程逻辑器件实现多路信号采集系统的设计2020-03-03 2090

-

可编程逻辑器件2014-04-15 3675

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1162

-

可编程逻辑器件基础及应用实验指导书2010-03-24 784

-

基于复杂可编程逻辑器件(CPLD)的120MHZ高速AD采集2010-01-17 849

-

什么是PLD(可编程逻辑器件)2009-06-20 30042

-

基于单片机的复杂可编程逻辑器件快速配置方法2009-03-28 1157

-

可编程逻辑器件设计2006-03-25 1179

全部0条评论

快来发表一下你的评论吧 !