可编程逻辑器件在高速DDR SDRAM中的应用优势

可编程逻辑

描述

I.引言

DDR SDRAM的原理及特点:DDR SDRAM不需要提高时钟频率就能加倍提高SDRAM的速度,因为它允许在时钟脉冲的上升沿和下降沿读写数据。至于地址和控制信号,还是跟传统的SDRAM一样,在时钟的上升沿进行传输。

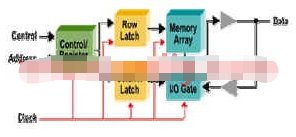

DDR (Double Data Rate SDRAM),能够以相同频率SDRAM的两倍来传输数据,每个时钟周期传输两次数据,它在时钟信号的上升沿和下降沿传输数据。存储单元工作在相同的时钟频率下,但是内部总线加宽,从内部阵列到缓存之间的总线宽度是外部总线(buffer)到控制器)的两倍,使得缓存到控制器的数据传输率达到内部存储单元工作频率的两倍。存储单元内部使用一个很宽但较慢的总线,但当数据传输到控制器时使用了一个较窄但是快速的总线。I/0口的控制电路对存储器的总体控制和时序具有极大的影响。

在DDR的读取过程中,需要考虑的有两个主要类型的延迟。第一类的是连续的DRAM读操作之间的延迟。DDR不可能在进行完一个读取操作之后就立刻进行第两个读取操作,因为读取操作包括电容器的充电和放电另外还包括把信号传送出去的时间,所以在两个读取操作中间至少留出足够的时间进行这些方面的操作。第二种延迟类型是叫做内部读取延迟(inside-the-read)。这种延迟同同两次读取操作之间的延迟非常的相似,但是不是由停止 /RAS和/CAS激活而产生的,而是由于要激活 /RAS和/CAS而产生的。比如,行存取时间(tRAC)--它就是在你激活RAS和数据最终出现在数据总线之间的时间。同样的列存取时间(tCAC)就是激活 /CAS引脚和数据最终出现在数据总线上之间的时间。

DDR SDRAM 控制器是一个可配置的,用户可以根据设计需要,灵活修改数据宽度、脉冲传输速率和 CAS 等待时间的设置。另外,DDR 控制器还支持组块管理,这是通过维护一个所有组块均被激活以及每一组块行激活的功能来实现的。DDR SDRAM 控制器通过这些信息决定是否需要一个激活命令或预充电命令。这有效缩短了 DDR SDRAM 接受读写命令的等待时间。

II.控制器总体框图:

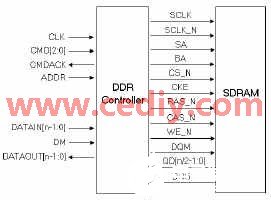

图2中DATAIN、DATAOUT分别是输入、输出数据信号,CMD信号为用户对DDR SDRAM进行的操作,可以支持NOP、WRITEA 、READA、REFRESH、PRECHARGE、LOAD_MODE命令。CS_N为片选信号,RAS_N、CAS_N分别为SDRAM的行选通、列选通信号。

图2:DDR控制器的总体框图

III.DDR 控制器主要模块

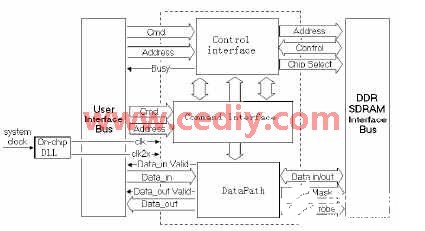

DDR控制器主要是由Control interface 模块、Data path模块以及Command interface模块组成,另外还包括FPGA上的DLL模块,如图3所示。

Control interface模块主要是对来自用户的command进行保存、译码,可支持NOP、WRITEA 、READA、REFRESH、PRECHARGE、LOAD_MODE命令。Control interface模块将Command信号和地址ADDR信号同时送到Command interface模块中,同时产生地址选通信号CA_N。

Command interface模块接收来自Control interface模块的译码的命令,对DDR SDARM产生相应的操作,即上面的6种命令。Command interface模块里还包含一个简单的仲裁器,用于对Command和refresh要求的仲裁。refresh要求总是优先于任何一个Command。有16 bits 的 refresh counter寄存器用于自动refresh。

Data path模块提供DDR和user interface之间的数据通路,通过对path width配置,可支持16、32、64的数据宽度。 burst length可以配置成是2、4、8。 Data path模块的数据宽度是DDR SDRAM的两倍,在时钟的上下沿都对DDR SDRAM进行操作。同时Data path模块产生DQS信号,即在写操作的时候Data path模块对写入DDR SDRAM的数据按照要求进行选通。如图中Data Strobe所示。

图3:DDR 控制器内部控制模块

此外,DDR SDRAM 控制器还利用了FPGA内部的DLL模块,给系统提供了2个时钟CLK 和CLK2X,并且可以改善时钟性能,减少时钟抖动,改善了系统的性能。

IV读写波形

图4:读数据波形图 图5:写数据波形

图4、图5是用采用Mentor modelsim 得到的仿真波形,是典型的读写波形,时钟频率为100MHz。

V系统实现及结论

DDR SDRAM 控制器在 Xilinx公司的XC2V1000 FPGA上实现,综合后使用了798个逻辑单元,在数据宽度为64,系统时钟为100Mhz的工作环境下,最高可达到1.6Gbytes/s的速率。使用的DDR SDRAM是Toshiba的TC59WM803BFT。

本文给出了基于FPGA的DDR SDRAM控制器的设计。DDR SDRAM 控制器是一个可配置的,用户可以根据设计需要,灵活修改数据宽度和 CAS 等待时间的设置。可广泛用于高速的DDR SDRAM中,提高系统的性能。

责任编辑:gt

-

可编程逻辑器件2014-04-15 3693

-

可编程逻辑器件是如何发展的?2021-04-29 1885

-

PLD可编程逻辑器件2021-07-22 2335

-

可编程逻辑器件设计2006-03-25 1191

-

可编程逻辑器件基础及应用实验指导书2010-03-24 798

-

什么是PLD(可编程逻辑器件)2009-06-20 30094

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1178

-

可编程逻辑器件(书皮)2022-07-10 809

-

可编程逻辑器件原理、开发与应用2017-09-19 938

-

可编程逻辑器件PLD课件下载2021-08-13 1513

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 2278

-

可编程逻辑器件的结构2023-03-24 2186

-

可编程逻辑器件测试2023-06-06 1331

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4615

-

可编程逻辑器件的特征及优势科普2024-02-26 2199

全部0条评论

快来发表一下你的评论吧 !