MAXIMD/A转换器MAX547的工作原理、性能特点和应用分析

模拟技术

描述

1.引言

MAX547是MAXIM公司生产的8通道、13位输入、电压输出的D/A转换器。其转换是通过倒置的“R-2R”梯形网络实现的。片内精确输出放大器可提供电压输出。在不需要外部元器件的前提下,MAX547的电压摆幅达-4.5V~+4.5V为双极性电压输出。MAX547内含带有13位并行数据总线的双缓冲接口逻辑电路。所有逻辑输入均与微机和TTL/CMOS电平兼容。另外,它的输出建立时间短,输出电压与输入数字量的线性好。MAX547可用于工业过程的自动控制、设备的自动检测、数字补偿/增益调整的随机函数发生器等。

2.MAX547的特点及引脚功能

MAX547具有如下特点:

·不需调整,满13位有效;

·片内有8通道的D/A转换器;

·具有缓冲输出;

·出厂时线性已校准;

·输出与输入一一对应;

·单极性或双极性输出的电压摆幅达±4.5V;

·输出建立时间短(5μs±1/2LSB);

·具有双缓冲输入锁存器;

·数字输入非同步装载,一次装载一对DAC锁存器;

·具有非同步的清除输入信号,可将DAC锁存器内容同时复位到模拟地电平;

·与微处理机和TTL/CMOS电平兼容。

MAX547有PLCC和塑料FP两种封装形式,塑料扁平封装的MAX547管脚排列如图1所示,管脚功能

3.工作原理

3.1D/A转换的实现

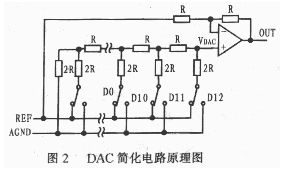

MAX547的D/A转换是通过倒置的“R-2R”梯形网络实现的,这些网络可将13位数字输入量转换为相应的模拟输出电压。输出电压的大小与输入的基准电压大小成正比。MAX547芯片中每两个通道DAC共用一个基准电压输入端(REF)和一个模拟地输入端(AGND)。每个REF输入信号决定其所控制通道的满量程输出电压。每个AGND输入信号决定其所控制通道的偏置电压。图2所示是MAX547通过倒置的“R-2R”梯形网络实现D/A转化的简化电路原理图。

图2中,DAC梯形网络的输出由增益为2的运算放大器缓冲。所有缓冲放大器的反相结点连接各自的基准电压输入端REF。这样双极性电压输出范围可以-REF~+REF(4095/4096)。

3.2MAX547工作时序

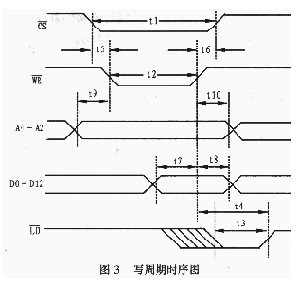

驱动MAX547的异步输入LD信号可将数据从输入锁存器传送到DAC锁存器。DAC锁存器的数据用来设置输出电压。所有输入端的控制逻辑均通过电平触发实现。数据可以锁存也可以直接传送给DAC锁存器。由CS和WR信号共同控制输入锁存器。LD信号用于控制数据从输入锁存器传送到DAC锁存器。当CS和WR信号同时为逻辑低电平时,输入锁存器打开;当LD信号为逻辑低电平时,DAC锁存器打开,在CS和WR为低电平期间,地址线A0,A1,A2必须有效,如图3所示。否则,数据会被写进错误的DAC。当CS和WR两信号中有一个为逻辑高电平时,数据将锁存在输入锁存器,在LD信号翻传至逻辑高电平的瞬间,MAX547再把数据锁存至DAC锁存器。若CS和WR信号为逻辑低电平,LD信号出被置为逻辑低电平,要实现数据正确传送,LD信号必须在CS和WR信号失效后持续t3或更长时间的逻辑低电平,如图3所示。驱异步CLR信号至逻辑低电平可使所有DAC的输出端复位到模似地电平,而与此时CS、WR、LD端输入信号的状态无关。在CLR信号翻转至逻辑高电平的瞬间,数据1000H都被锁存至所有的输入锁存器和DAC锁存器中。

4.与MCS8051单片机的接口电路

MAX547与8051单片机的接口电路如图4所示。由于MAX547有13位输入位,而8051单片机只有8根数据线,所以单片机需分两次发送要转换的某一数据,因此,电路中选用了74LS377作为数据锁存器。它的相关指令如下:

假设选择0通道(A2A1A0=000B),转换数暂存R1(高5位)和R0(低8位)中,则程序如下:

MOV DPTR,#8000H

MOV A,R0

MOVX A,@DPTR ;选中锁存器74LS377,并锁存低8位。

CLR P1.0;DAC A的锁存器透明。

MOV DPTR,#0000H

MOV A,R1

MOVX A,@DPTR ;选中MAX547及0通道,转换数送入DACA的输入锁存器

NOP

SETB P1.0 ;转换数送入DAC A锁存器,同时输出结果。

如果要获得±2.5V的满量程输出电压摆幅,可以选用MAX873作基准,它可以同时驱动全部4个基准输入端。若想获得一个±4.096V的输出电压摆幅(1LSB=1mV),可以选用MAX676,它在+5V电源下足以驱动2个基准输入端。

用一个运算放大器可以缓冲基准输入以获取较高精度并可以使用具有极低驱动能力的基准输入端。图4中运算放大器的负结点直接接MAX547的基准终点,并直接从基准输入端用低电流导线检测电压,以消除电路板引线阻抗的影响。而把反馈电阻加到各个基准缓冲放大器是为了能通过单个基准产生不同的基准电压。每一个基准输入端用一个0.1μF/50V的钽电容接地,可以降低系统噪声对转换精度的影响。

AGND端接REF/2能获得正单极性输出。调节R2,则AGND可被偏置到电源电压范围内的任何电压,但要确保所用运算放大器有足够的吸收电流能力以吸收模拟地端的电流。双极性输出时,用一个带有未断开模拟地的多层印制板电路作模拟地可获得最优的工作表现。在正常工作情况下,当所有AGND管脚电势相等时,把4个AGND管脚连接到同一点并同时作为数字系统的接地点,可最大限度地消除地线噪声对转换精度的影响。

另外一种接地设计方法是数字式偏置AG-ND。即把一个DAC的输出连接到一个或多个AGND的输入端。用这种方法时,不要把一个DAC的输出与它自己的AGDN输入端相连。

另外,在开启电源时应保证进入任何基准电压输入脚的电流不超过10mA。图4中在VSS和GND间连接了一个肖特基管,以确保VSS电位不超过地电位300mV以上。在VSS与GND,VDD与GND之间接1μF的独石旁路电容可滤除电源和地之间的高频干扰。在电源稳定之前,为避免电源干扰信号影响转换精度,其逻辑输入端不能有电流输入。数字线可能驱动超过10mA的电流,因此应在逻辑管脚设置限流电阻(如470Ω)。

责任编辑:gt

-

MAX547:八通道13位电压输出DAC的高性能解决方案2026-04-17 101

-

A/D转换器的工作原理和关键参数2024-08-30 6260

-

LLC谐振转换器的工作原理和工作区域2024-07-16 7540

-

逐次逼近型A/D转换器的工作原理和特点2024-05-21 4873

-

升压转换器的工作原理、优点和应用2024-02-01 5246

-

八位串行A/D转换器ADC0832具有什么特点?工作原理是什么?2021-09-29 7107

-

A/D转换器AD6644的工作原理、性能特点及应用2021-05-27 6675

-

升压转换器MAX8815A相关资料分享2021-03-26 1064

-

MAX1200的特点功能和工作原理2019-04-15 1828

-

模数转换器的工作原理与分类特点详解2017-06-06 5661

-

DA转换器工作原理2012-08-20 3379

-

八路13位数模转换器MAX547的原理及应用2011-06-03 1792

-

TC534的性能特点及工作原理2010-12-06 3006

-

D/A转换器工作原理2009-01-14 9324

全部0条评论

快来发表一下你的评论吧 !