EUV光刻机全球出货量达57台

描述

EUV光刻机全球出货量达57台

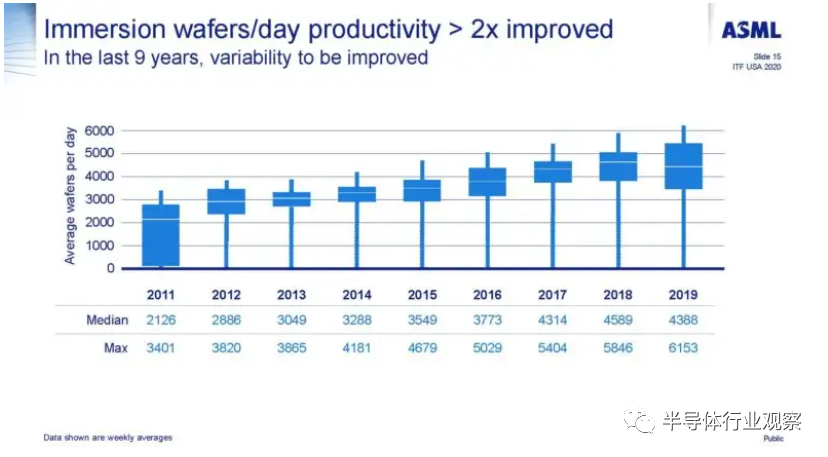

IMEC是推动半导体技术前进的主要组织之一,日前,他们举办了一场线上论坛,谈及了对芯片现状和未来的看法。在演讲中,ASML总裁则对光刻的发展进行了演讲。从他的PPT中可以看到,浸入式光刻在过去九年中增长了两倍。

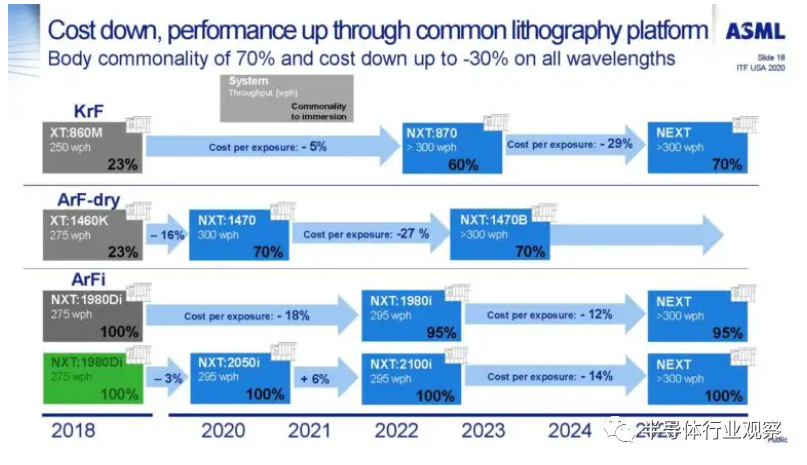

而ASML计划提高所有曝光工具每小时的晶圆数量。

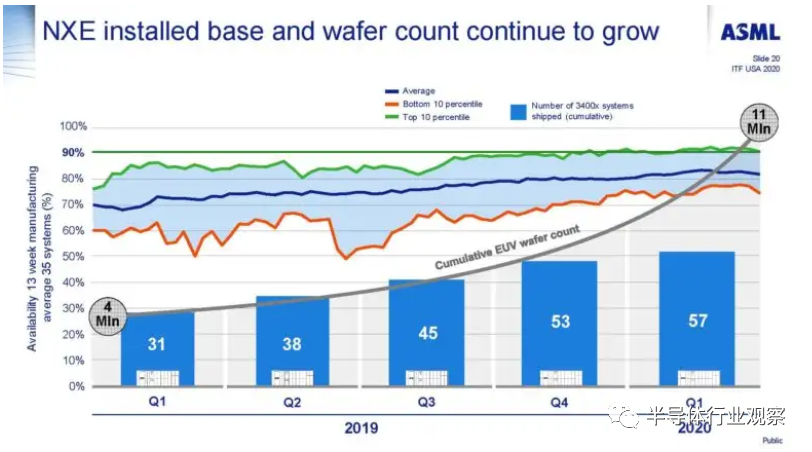

与此同时, 他指出,EUV继续为ASML的客户提高产量,迄今为止,他们的客户已经使用EUV光刻机曝光了超过1100万个EUV晶圆,并交付了57个3400x EUV系统(3400平台是EUV生产平台)。

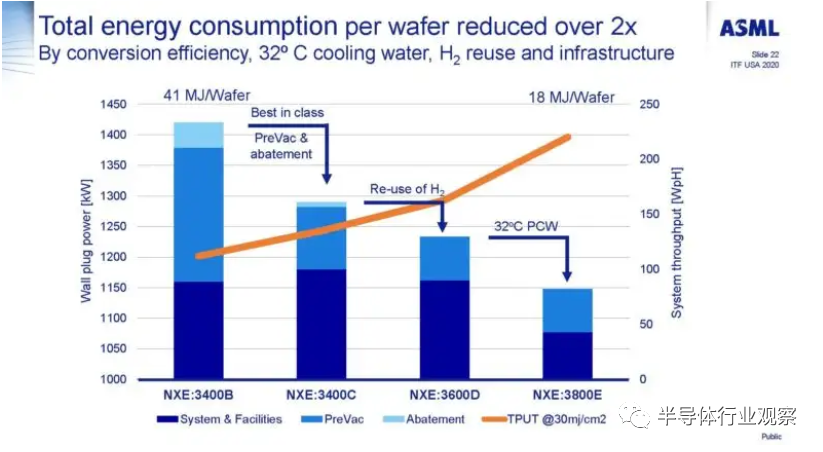

ASML计划继续提高EUV吞吐量,同时减少每个晶圆的总能量。尤其是2倍的能源节省,这吸引了大家的高度关注。他们还期望通过NXE3800系统达到每小时30mj / cm2的剂量通量,已达到最高每小时225个晶圆的生产能力!

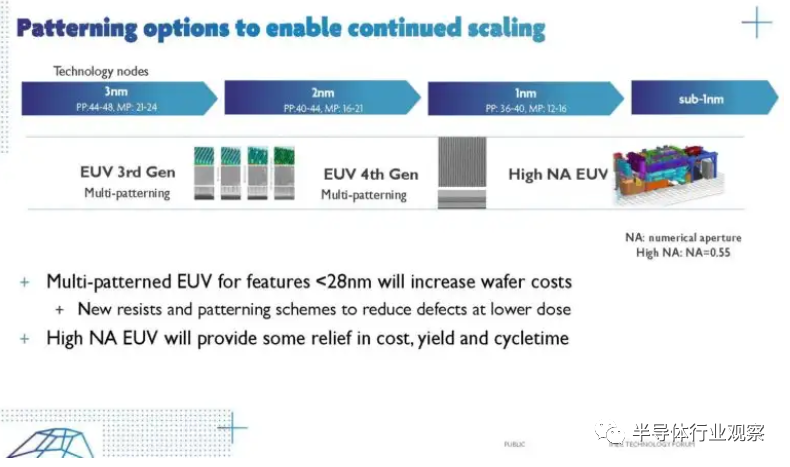

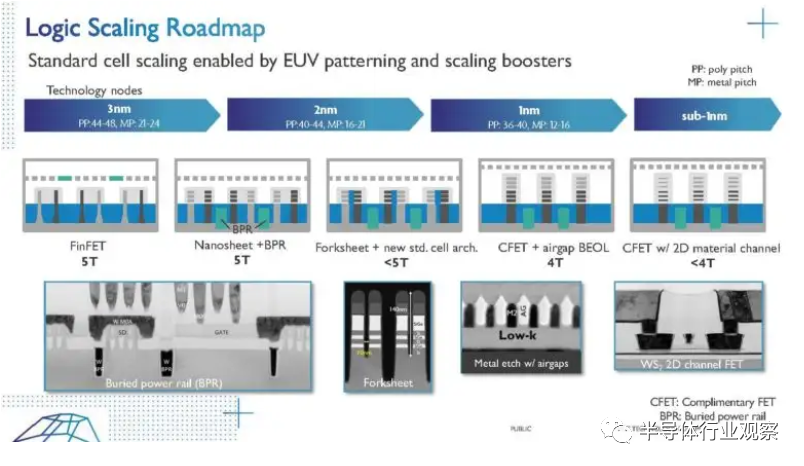

在演讲中,IMEC高管也分享了他们对行业的看法。 据IMEC公司CEO Luc Van Den Hove表示,过去几年来,即使尺寸缩放速度变慢,但Design Technology Co Optimization(DTCO)也可以实现连续缩放。借助DTCO,工艺优化已实现了标准逻辑单元轨道高度的减小。标准单元的高度是M2P( metal 2 pitch)乘以轨道(track)数,而6 track cell 的高度代表了当前的最新技术水平。 在他的演讲中,Luc概述了一个路线图,其中包括6条轨道的FinFET,让路给具有埋入式电源轨(buried power rails)的5轨道纳米片,然后增加了用于实现4.5条轨道纳米片的叉板(forksheets ),4条轨道CFET以及最终具有2D通道的CFET。 他还强调了对功率,性能,面积和成本(PPAC)的需求。多年来,基于功率,性能和面积(PPA)来表征前沿逻辑过程。例如,在最近的电话会议上,台积电(TSMC)讨论了他们的3nm工艺,即在相同功率下提供大约70%的逻辑密度,在相同性能下提高10-15%的速度,在相同性能下降低25-30%的功率。人们越来越认识到,成本是新流程定义的必要要素。 Imec CMOS技术高级副总裁Sri Samavedan介绍了Imec先进的半导体技术发展的最新情况。他表示,随着逻辑缩放继续达到3纳米及以下,EUV将不得不过渡到多图案化,直到可获得高NA EUV。

他还提出了与Luc Van Den Hove的演讲中类似的逻辑缩放路线图,但有更多细节,例如,要进入5轨道单元,需要将电源导轨作为埋藏式电源导轨(BPR)移入基板。

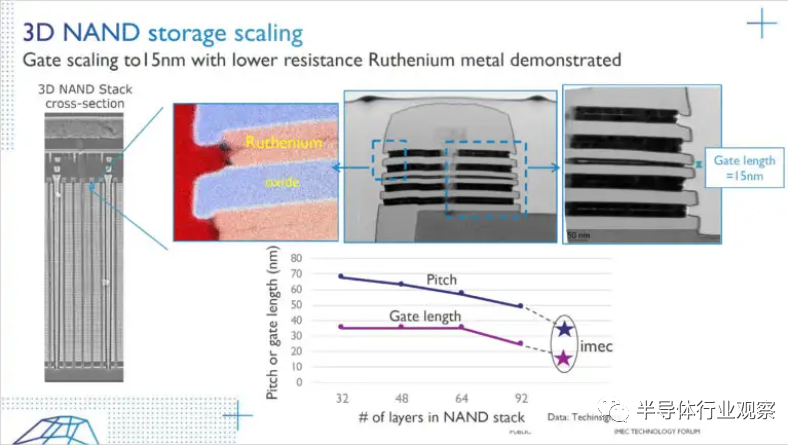

在3D NAND中,关键挑战之一是如何继续有效地添加更多层。随着堆栈变得越来越高,图案化变得越来越难。Imec一直在寻找钌(Ru)替代水平字线板的钨(W)。Imec相信,Ru可以帮助将线材的厚度从目前的大约30nm减小到大约15nm。就个人而言,我认为Ru太昂贵了,无法在3D NAND中实现,但是替代材料的概念很重要。

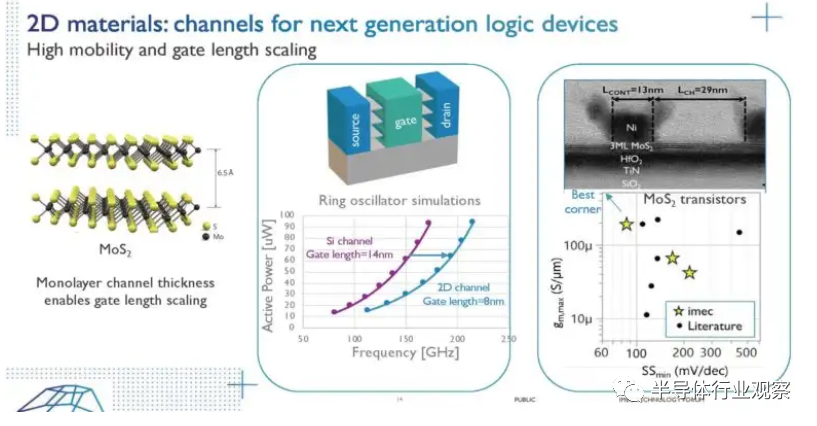

他还谈到了逻辑的2D材料,并提供了有关MoS2的一些数据,这些数据可以实现更细的通道和更短的通道长度。

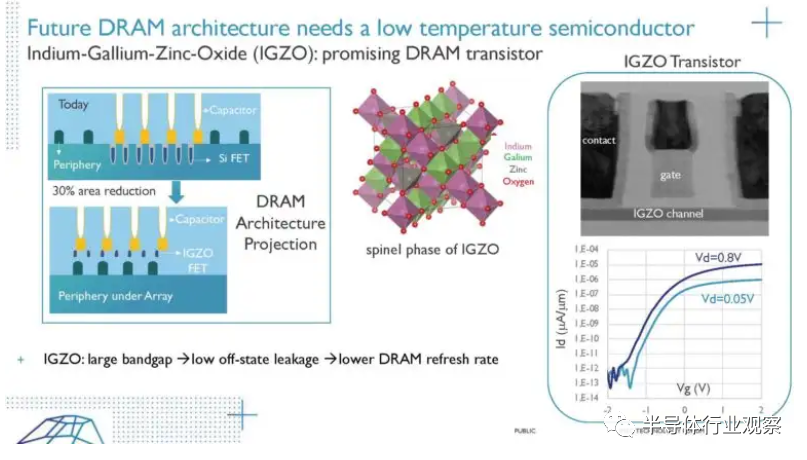

最后,我发现用于DRAM的低温沉积铟镓锌氧化物(IGZO)的选择很有趣。在逻辑,NAND和DRAM这三个主要的半导体产品领域中,DRAM面临着最未知/最困难的扩展挑战。低温沉积的低漏电晶体管可以使访问晶体管和电容器堆叠在外围逻辑上,从而增加DRAM密度。

国务院审议通过,集成电路正式成为一级学科!

今天上午的国务院学位委员会会议已投票通过集成电路专业将作为一级学科,并将从电子科学与技术一级学科中独立出来。集成电路专业拟设于新设的交叉学科门类下,待国务院批准后,将与交叉学科门类一起公布! 设立与集成电路有关的一级学科已经经过多年的讨论,但由于一直存在各种争议而无法成形。随着学科的不断发展变化,原有的一级学科划分在事实上确实已经限制了我国集成电路人才的培养,进而影响到了我国集成电路产业的良性发展。在中美贸易摩擦的背景下,这一问题被极具放大。 早在去年10月8日,工信部公布了一份答复政协《关于加快支持工业半导体芯片技术研发及产业化自主发展的提案》的函,函中工信部尤其指出了要“推进设立集成电路一级学科,进一步做实做强示范性微电子学院。”

此次集成电路作为一级学科通过,可以说对整个集成电路来说,都是一大利好消息!针对这一好消息,半导体行业观察记者随即联系到了电子科技大学电子科学与工程学院副教授黄乐天:黄老师就集成电路成为一级学科对于人才培养的影响这一问题发表了自己的见解:“其实’学科’是我国高等教育建设的基本“抓手”。一个很实际的例子就是“双一流”建设。“双一流”就是指的“一流大学”和“一流学科”。而一流大学必然以一流学科为依托。因此在评比时大家是按照学科质量来进行评比,拨款时是按照学科建设来进行。如果没有独立的学科,就没有直接的考评体系,也不会对应直接的建设经费。在以前的模式中,集成电路是被分散到各个学科中的。因此建设经费实际上是经过了“二次分配”甚至是“三次分配”,很多时候是拿不到建设经费的,尤其是对于一些集成电路方向实力偏弱的学校。对应的师资队伍建设、教师职称晋升等层面也会受到较大的限制甚至是打压。” “而如果集成电路成为一级学科,等于将集成电路学科单列进入了考核和拨款计划中,其发展空间相比于之前大了很多。这首先有利于形成一支较为全面、稳定的专业教师队伍,有利于国家对于集成电路人才培养和研究的资金“专款专用”,也会在研究生招生名额等问题上有所改进。这对于我国后续的人才培养,尤其是研究生以上学历的高层次人才培养有非常重大的促进作用。”黄老师补充说。

-

euv光刻机是哪个国家的2022-07-10 9009

-

euv光刻机可以干什么 光刻工艺原理2022-07-06 8530

-

EUV光刻机何以造出5nm芯片2021-12-07 12325

-

EUV光刻机何以造出5nm芯片?2021-12-01 14191

-

魂迁光刻,梦绕芯片,中芯国际终获ASML大型光刻机 精选资料分享2021-07-29 70632

-

ASML今年将出货交付40台EUV光刻机2021-01-21 2107

-

EUV光刻机还能卖给中国吗?2020-10-19 11146

-

光刻机工艺的原理及设备2020-07-07 17525

-

ASML研发新一代EUV光刻机 分辨率能提升70%左右2020-03-17 3607

-

台积电将包揽ASML这批EUV光刻机中的18台2019-04-30 8822

-

ASML将于明年出货30台EUV光刻机2018-10-19 4030

全部0条评论

快来发表一下你的评论吧 !