基于LTC400器件在数字校正环路实现20位DAC的设计

模拟技术

描述

(文章来源:电子产品世界,作者:Jim Williams , J.Brubaker , P.Copley )

引言

近来,高精度、仪表等级的数模转换技术取得了明显的进步。10年以前,12位数模转换器(DAC)就被认为是优质器件。如今,16位DAC已经面市,而且在系统设计中的应用也越来越普遍。这些16位DAC是真正的精密型器件,其线性误差小于1LSB,温度漂移低于1ppm/℃。但是,有些DAC应用还需要更高的性能。自动测试设备、仪器、校准仪表、激光修整器、医疗电子产品以及其它应用常常需要16位以上的DAC准确度。人们已经生产出了电路组件形式的18位DAC,不过它们价格昂贵,并且需要进行经常性的校准。准确度达20位甚至23位以上(0.1ppm/℃!)的DAC由手动开关式开尔文-华莱(Kelvin-Varley)分压器来提供。这些器件虽然具有令人惊叹的准确度,但缺点是体积庞大、速度缓慢且价格极为昂贵。其应用领域一般局限于标准实验室。一项有益的开发将是一款易于构造且无需频繁校准的实用型20位(1ppm) DAC。

20位DAC架构

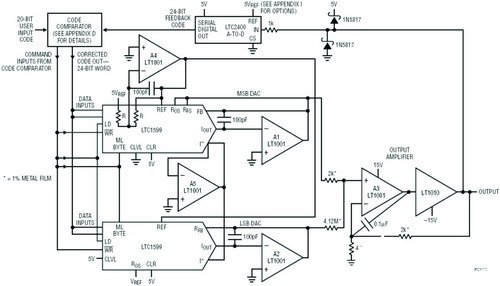

图1描绘了一款20位(1ppm)DAC的架构。该电路基于一款刻度和零点漂移低于0.02ppm/℃的真正1ppm模数转换器的面市。这款型号为LTC400的器件在数字校正环路被用作一个反馈组件,以实现20位DAC。

图1: 基于环路的20位DAC概念图。数字比较允许模数转换对DAC误差进行校正。LTC2400 模数转换器的低不确定性特征有望实现1ppm的输出准确度

实际上,“从属”20位DAC的输出由“主控”LTC2400 模数转换器来监视,后者将数字信息馈送至一个代码比较器。该代码比较器负责区分用户输入字和LTC2400的输出,并向从属DAC提供一个校正代码。环路以这种方式把从属DAC的漂移和非线性连续校正至一个由模数转换器和VREF所决定的准确度。对DAC的唯一要求是其应具备单调性。环路中的其它组件均无需稳定。

该环路具有诸多合乎要求的属性。如前文所述,准确度限值是由模数转换器及其基准来设定的。其它组件均无需稳定。此外,环路特性还对低阶位变址和抖动进行了平均处理,从而消除了环路所固有的小信号不稳定性。最后,可采用传统的远端采样或通过把模数转换器置于负载侧来实现数字化采样。该模数转换器采用SO-8封装,且外部组件极少,因而使得这种数字化开尔文(Kelvin)检测电路成为一种实用型方案。

电路细节

图2为该1ppm DAC的详细原理图。从属DAC由两个DAC组成。代码比较器输出的较高16位被馈送至一个16位DAC(“MSB DAC”),而较低的位则被一个单独的DAC (“LSB DAC”)所转换。虽然向两个DAC提供了总共32位,但有8位是重叠的,因而可在所有的条件下保证环路捕获特性。组合式DAC的合成24位分辨率提供了低于第20位的4位变址范围,从而确保了一个1ppm精度等级的稳定LSB。A1和A2把DAC的输出电流变换为电压,并在A3上相加。对A3的放大系数进行了适当的设置,以使校正环路能够始终捕获并校正零标度和全标度误差的任何组合。A3的输出(即电路输出)被馈送至LTC2400模数转换器。LT?010提供缓冲处理以驱动负载和电缆。由代码比较器来区分该模数转换器的数字输出和输入字,并产生一个校正代码。该校正代码被加至MSB和LSB DAC,从而对反馈环路进行补偿。环路的完整性由模数转换器和电压基准误差来决定。采用5V供电电源的模数转换器上的电阻器和二极管可保护其免遭意外A3输出(上电、瞬变、掉电等)的损坏。A4是一个基准负输出转换器,而A5则负责向两个DAC提供一个干净的接地电位。

图2 1ppm DAC的细节

线性度考虑

模数线性度决定了DAC的总体线性度。模数转换器具有约 ±2ppm的非线性度。在容许该误差的应用中,可将其忽略不计。如果需要1ppm的线性度,则可通过利用软件方法对残余的线性度误差进行校正来实现。

DC性能特征

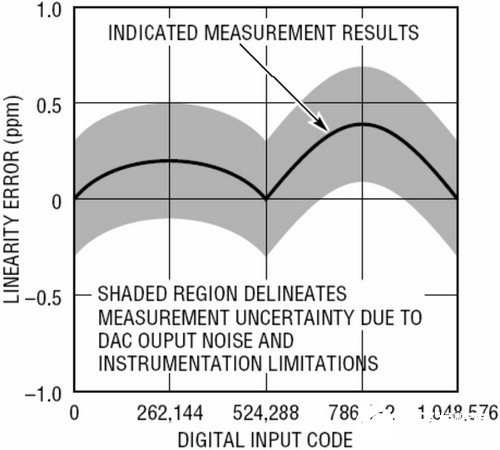

图3 线性度曲线显示了在所有代码条件下误差均不超过1ppm

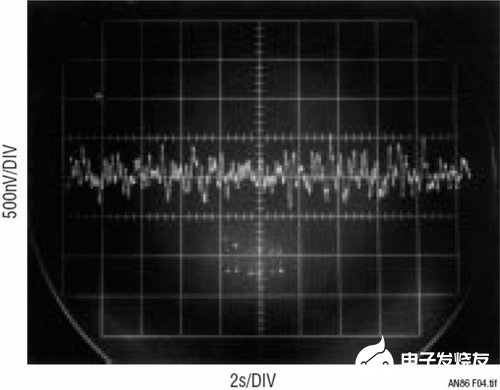

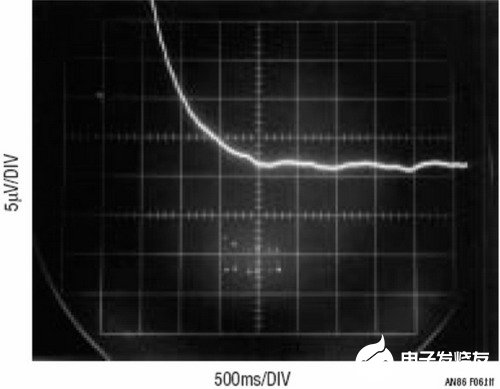

图3描绘了线性度与输出代码的关系曲线。数据显示:在所有的代码条件下线性度误差均不超过1ppm。由图4可见,在0.1Hz至10Hz通带中测得的输出噪声约为0.2LSB。设备的局限性 (它设定了一个约0.2mV 的噪声层) 对该测量结果产生了轻微的负面影响。

图4 输出噪声低于1uV

动态性能

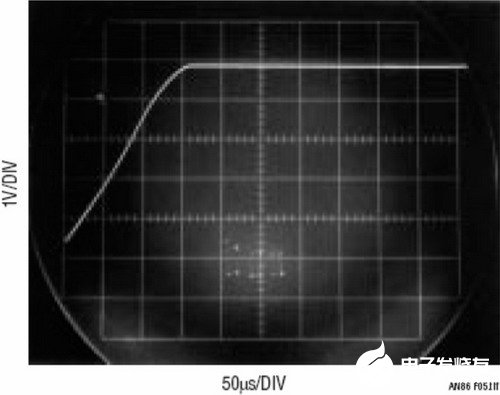

模数的转换速率与环路的采样数据特性和低速放大器组合起来,规定了一个较低的DAC响应。图5的转换响应需要大约150ms的时间。

图5 DAC输出全标度转换特性

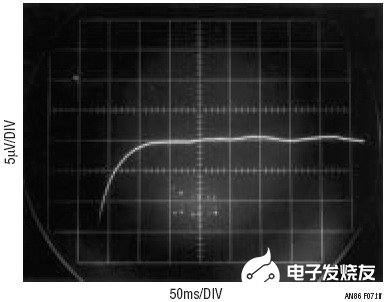

如图6所示,至1ppm(±5mV)以内的全标度DAC稳定时间约需1400ms。一个500mV的较小阶跃(图7)仅需100ms的时间便可稳定至1ppm以内。

图6 在一个全标度阶跃后的高分辨率稳定情况,稳定时间是1400ms至1ppm以内

图7 对于一个500uV的转换,小阶跃仅需100ms的时间便可稳定至1ppm以内

结语

表1给出了1ppm DAC规格的概要。这些规格应被视作指导准则,因为不同的选项和显着的偏差将对性能产生影响。请参阅相应的附录,以了解设计的详细说明书和折衷方案。

责任编辑:gt

-

Linear推出4通道电压输出16位和12位DAC系列2010-05-06 2091

-

新型16位DAC系列功能更加丰富2018-08-24 2947

-

数字电源和模拟控制环路实现高精度电源管理2018-09-26 1980

-

基于LTC2378-20 的SAC ADC 的数字增益压缩设计2018-10-31 3040

-

AD421:环路供电型4 mA-20 mA DAC 数据手册2021-03-19 1160

-

LTC1664:Micropower Quad 10位DAC数据Sheet2021-05-08 750

-

LTC1665/LTC1660:微功耗8位和10位DAC数据表2021-05-09 879

-

UG-250:16位、串行输入、环路供电4 mA至20 mA DAC评估板2021-05-11 913

-

LTC1588/LTC1589/LTC1592:12位/14位/16位软范围DAC,带可编程输出范围数据表2021-05-23 832

-

LTC2609/LTC2619/LTC2629:带I²C接口的四路16位/14位/12位轨对轨DAC产品手册2021-05-26 1074

-

DAC11001B 高级、20位、单调DAC技术手册2025-10-31 793

-

DAC11001A 20位单调DAC技术手册2025-11-04 659

-

DAC161P997 16 位 4-20mA 环路输出 ΣΔ DAC 技术文档总结2025-11-18 1046

-

解析LTC7543/LTC8143:高性能12位串行乘法DAC2026-04-13 123

-

LTC1655/LTC1655L:小封装大能量的16位DAC2026-04-16 119

全部0条评论

快来发表一下你的评论吧 !