基于Spartan3主流低端FPGA器件实现PWM发生器的设计

可编程逻辑

描述

1.引言

脉宽调制技术( Pulse Width Modulation, PWM)起源很早,随着科学技术的发展,广泛应用在电力、电子、微型计算机、自动控制等多个学科领域。自 80年代初以来,出现了多种 PWM实现方法,归纳起来有自然采样法、规则采样法或谐波消去法等等,其中自然采样法最能真实地反映 PWM的控制思想,效果最好。对于传统的控制器而言,自然采样法算法是一个超越方程,需用计算机迭代求解,运算时间较长。如果事先算好存入存储器,则不仅浪费了存储空间,而且设计不灵活,精度低。近几年推出的 DSP处理器虽然在芯片内部整合 PWM发生器模块,但是这些模块已经在硅片上实现了,不能够随意调整系统参数,缺乏灵活性,不能够适应复杂的系统设计。

本课题在 FPGA上实现了高精度的PWM发生器,在 Xilinx公司的 Spartan3(-4速度级别 )主流低端 FPGA器件上可以约束到高达 200MHz工作频率,并支持 14位以上的可调数据位宽。设计全参数化配置,作为可重用模块能够嵌入到更大的 FPGA应用系统中,具有较高的工程应用价值 。

2.高精度 PWM发生器的设计与实现

a) RTL级逻辑设计

本设计采用的是自然采样法产生 PWM波形。首先对实际的模拟电压值进行离散化,然后将离散化后的调制数据与载波数据进行实时比较,比较结果输送给死区信号发生器模块,该模块将死区保护时间附加到比较结果中,并输出 PWM波形。其中死区信号发生器的死区时间是可调的,以适应不同场合下的死区时间要求。

本设计主要有三个主要模块组成,分别是载波发生器、时序等于比较器和死区保护发生器。设模块位宽为 W,现分别介绍设计要点如下。

1、载波发生器:设计采用了锯齿波作为 PWM载波。从电路的角度来讲设计锯齿波发生器会比设计三角波发生器使用更少的组合逻辑资源,从而有利于时序约束到较高的频率。为减少宽位宽的计数器的进位链长度,采用 Prescaled结构的计数器,将其拆分为 2位计数器和(W-2)位计数器,

减少了组合逻辑延迟。在优化阶段通过设定 MultiCycle约束,还可以进一步提高器件工作速度。

2、时序等于比较器:该比较器不同于普通的纯组合逻辑等于比较器。通过例化 FPGA的底层子元件,在该等于比较器内部插入了一级 D触发器,大大减少了由于数据位宽增加而增加组合逻辑延迟。由于存在一级寄存器,比较结果需要延迟一个时钟周期才能够输出。对于 PWM调制这种应用场合,高精度情况下可以接受比较结果的一个时钟周期延迟,因此使用该比较器造成的比较误差非常小。

3、死区保护发生器:根据给定的死区长度数据,将输入的 PX信号输出为 PH和 PL信号,并在 PH和 PL数据的变沿时刻插入死区保护(同时置为高电平)。具体方式是通过上升计数器和下降计数器来实现的:上桥臂控制信号 PH在 PX信号为 1并且上升计数器计数完成后才置 1,此时上桥臂开通;下桥臂控制信号 PL在 PX信号为 0并且下降计数器计数完成后才置 1,此时下桥臂开通。这个机制能够保证上下桥臂不会同时导通。

为了保证时序收敛,根据实际情况,考虑到死区保护发生器模块的任务是插入保护时间,因此工作速度可以较低,故工作频率设计为 100MHz;其余两个模块的工作频率设计为 200MHz。如图 2-1所示,跨越异步时钟域的信号线只有 PX。由于这两个时钟域同相且具有二分频关系,只需要对比较器输出信号进行二倍脉冲展宽即可。

由于死区时间在不同的应用场合下也是不同的,且一般都在 1us以上。因此根据设计的技术指标,设计了一个 6位寄存器保存死区宽度数据,并在设计内部对输入数据进行重新移位,以适应死区时间的区间可调特性。据设计测算,模块工作频率在 100MHz下,死区时间可以在 2.5us到 5us区间内实现 64档调整。

b)结构优化实现

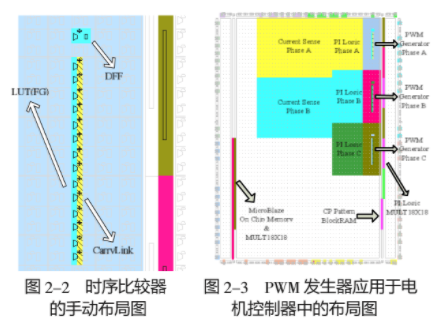

经过 RTL级设计之后,进行软件默认的综合和布局布线并不能够收敛到 200MHz。根据静态时序分析报告,发现关键路径仍存在于比较器的组合逻辑上。根据路径分析,虽然比较器进行了优化设计后减小了组合逻辑本身的延迟,但是软件自动布局布线之后的网线延迟很大,没有达到预期的优化效果。因此对该部分逻辑采用 Floorplanner工具进行手动布局,如图 2-2所示。

图 2-2中 DFF为 D触发器,实现了中间结果的一个时钟周期寄存; LUT为查找表,在此处用法为 FG(Function Generator,功能发生器 ),比较器的内含逻辑即保存在查找表中; Carrylink为进位链,布局到 FPGA中的直接进位链上,这样进位延迟最小。通过手动布局约束,可以让软件在自动布局布线过程中预先分配好这些关键逻辑的布局资源,减小关键路径上的连线延迟。

图 2-3是本 PWM发生器应用在一个三相步进电动驱动器中的布局实例。该实例例化了三个本 PWM发生器以驱动三相桥臂,参见图 2-2右上部分。通过该实例,充分说明了只要手动布局关键资源,模块可以以同样的优化结构复用到更大的 FPGA应用当中去。

经过 Floorplanner布局之后,时序收敛。静态时序分析表明该模块的最大周期时间为 4.642ns(折算过来的频率达到 215MHz),其中 3.409ns为逻辑延迟 , 1.233ns为布线延迟,逻辑延迟占到了总延迟的 73.4%,达到这个优化效果是非常令人满意的。

进行布局布线后仿真时发现设计有些情况下会出现模块 reset失败的现象。经过分析,发现是异步重置的 recovery time和 removal time无法满足某些 200MHz工作的 D触发器的要求。这是因为本模块都是采用的异步 reset,而异步 reset网络在 FPGA内部是唯一的,具有非常大的全局扇出,对于大型设计很容易造成数纳秒级别的传输延迟。而 200MHz的 D触发器工作周期才只有 5纳秒,很容易造成时序错误。根据这一情况,对进行本模块的异步 reset信号进行了本地同步化,将异步 reset信号同步到三个完全相同的 D触发器内部,再分派给三个子模块,有效的减低了扇出系数。修改后的设计就没有再出现过 reset失败的现象了。

3.设计的仿真与验证本设计采用 ModelSim软件进行仿真验证。通过功能仿真验证设计的正确性,通过布局布线后仿真验证实际工作的正确性和稳定性。

图 3-1是 PWM发生器的功能仿真波形。图中的 ph和 pl两根信号线就是 PWM发生器的输出信号。该仿真采用了 14位数据宽度,其 PWM输出的载波频率为 200MHz / 214 = 12.2KHz。死区保护时间在 2.5us~5us时间内可调。在给定 pwm寄存器和 deadprotect寄存器的输入后,该发生器能够正确地产生指定的 PWM波形输出。使用仿真波形图中的游标进行测算,所有波形数据符合设计预期。功能仿真通过。

3-2是 PWM发生器的布局布线后仿真波形图。根据同样的方法,测算在不同输入波形的宽度,并计算验证,所有波形数据符合设计预期。布局布线后仿真通过。

本设计最终占用 FPGA资源如表 3-1所示。可见本设计经过优化后,综合后工作速度高,资源占用非常小。参数化的设计,可重用性也非常好。

4.结束语

本文提出了一种在 FPGA器件上实现高精度 PWM发生器的设计方法 [4]。首先根据 PWM调制原理选择了其中效果最好的采用自然采样法调制 PWM信号。根据自然采样法的思想,将设计分拆为三个子模块,每个子模块都相对功能简单,并且易于设计和优化。考虑到以后工程应用的移植性,设计采用了参数化方式,主要的数据位宽和参数都可以直接在常数声明文件中进行配置。在每一个子模块的设计工程中,都分为了 RTL功能设计和结构优化两部分——RTL功能设计实现模块功能,结构优化是在功能不变的前提下,通过等效结构变换减小设计的组合逻辑延迟,避免高扇出网络,提高设计稳定性。在结构优化中,还解决了 200MHz以上高速设计中异步 reset信号存在的潜在不稳定性问题。完成了设计和优化工序后,对设计进行了功能仿真和布局布线后仿真,经过人工计算比对, PWM发生器的输出完全符合预期,保证了之前的设计工作的正确性。最后给出了 FPGA资源占用表格,供重用该模块评估时使用。

本文作者创新点:在比较器部分的设计当中,创造性地设计了内部带有一级 D触发器的等于比较器,并给出了最佳的 Floorplanner布局图,解决了高位宽下过长的进位链带来的大延迟的问题,在控制精度和器件工作频率之间找到了一个兼顾二者的契合点。采用了这种类型的比较器之后,本 PWM发生器可以在 200MHz的工作频率下支持非常高的数据位宽,提供非常精确的 PWM调制波形。

责任编辑:gt

-

如何在FPGA中实现随机数发生器2024-08-06 1971

-

如何使用FPGA实现静止补偿的PWM脉冲发生器设计2020-01-07 1276

-

请问我的Spartan3 / AN上的FPGA上有这个IP核功能吗?2019-07-19 1422

-

Isthis Flash与Xilinx Spartan3 FPGA兼容吗?2019-06-03 1029

-

测量spartan3静态功耗2019-05-20 1504

-

Spartan3 FPGA的编程和非编程没有任何输出2019-01-10 1696

-

如何获得 Spartan-3A FPGA 器件的节能模式2018-05-22 3580

-

基于fpga实现信号发生器2018-04-20 1602

-

基于FPGA和PWM的多路信号发生器设计2017-11-18 7677

-

SPARTAN3 AN系列电路设计及使用注意事项2017-01-11 1535

-

基于FPGA的多功能图像目标发生器的设计与实现2016-08-30 789

-

实现基于spartan3与CAN总线连接后的的汽车时速的模拟仿真2016-06-07 975

-

FPGA实现智能函数发生器设计2011-07-25 937

-

QDR SRAM与Spartan3 FPGA的接口设计2011-06-01 6345

全部0条评论

快来发表一下你的评论吧 !