基于新放大器结构在流水线模数转换器中的应用研究

模拟技术

描述

(文章来源:电子学报,作者:黄显洋 , 李树荣 , 姚素英 )

本文提出了一种新颖的放大器结构。它由两部分组成:前面为跨导放大器,后面则是由电阻反馈形成的跨阻放大器,两种放大器的组合构成了具有高输入阻抗、低输出阻抗的电压放大器。与普通放大器不同的是,在我们设计的工作条件下,它输出端的极点几乎不受负载电容的影响。用该放大器作为预放大级,驱动一单级主放大器所构成的两级运放在负载电容为4pf的情况下实现了超过1GHz的增益带宽积,瞬态分析的结果表明它可以在10ns内达到0。01%的精度(闭环增益为8),而功耗仅有25mW,远低于同性能其他结构的放大器,非常适合作为高速高精度流水线模数转换器中的首级余量放大器使用。

流水线ADC以其高速高精度低功耗的优点得到广泛应用。近些年来,流水线ADC发展的趋势是通过减少每级的位数,降低对电路中主要功耗元件余量放大器增益带宽积(GBW)的要求,从而降低整个系统的功耗。但因为每级多位的结构能够显著提高ADC的线性,并且可以减少总的级数以及放低对后面各级精度的要求,所以在高精度的场合有利于性能的提高和功耗的优化。由于上述原因,很多高精度的ADC采用第一级多位的结构,这样就要求首级余量放大器有较大的闭环增益,对它的增益带宽积提出了很高的要求,设计高增益带宽积低功耗的运算放大器成为实现这种高速高精度流水线ADC性能的关键。

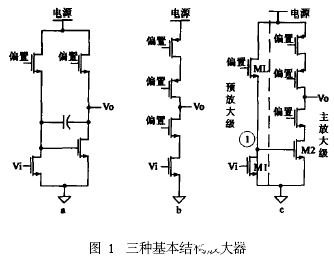

流水线模数转换器中常用的运算放大器有:Miller补偿的两级结构图1(a),单级结构图1(b)以及带有预放大级的两级结构图1(c)。Miller补偿的两极结构优点是直流增益高,但是该放大器主极点在内部,而输出端还存在一个位置较低的非主极点,这大大限制了它的速度,而要将非主极点推到较高的频率需要增加很大的功耗。单级放大器主极点在输出端,内部没有位置较底的极点,并且通过采用共源共栅结构或者增益自举(gain-boost)技术同样可以达到很高的直流增益,因此非常适合应用在高速场合。但是当放大器需要工作在较低的反馈系数下即实现大的闭环增益时,单级放大器所需的功耗迅速增加,这是因为:单级放大器的增益带宽积为gm/C1(gm为放大器输入管跨导,C1为输出端有效负载电容),其环路增益带宽约为fgm/C1(f为反馈系数),当负载电容一定时,为达到规定的速度(速度决定于环路增益带宽),反馈系数的减小要求放大器跨导增大;在管子尺寸一定的情况下,跨导与电流的平方根成正比,即反馈系数减小一半,放大器功耗增加为原来的四倍。

Miller补偿的两级结构也存在类似的问题。带有预放大级的两级放大器(跨导自举放大器)是在单级放大器的基础上加入一高速预放大电路(如图1c所示),该预放大电路通常只需达到几倍的直流增益,但必须有很大的带宽,即不引入较低频率的极点,以保证两级运放的稳定性。该结构放大器的增益带宽积为Agm/C1(A为预放大电路的直流增益),预放大级的加入使整个放大器的增益带宽积提高为原来的A倍,而这仅仅以预放大电路本身较小的功耗为代价,因此在需要很高增益带宽积的放大器时,带有预放大级的两极结构是较理想的选择。

在设计预放大电路时,特别是在高速电路中,主要难点是增加它的带宽,使预放大电路所有的极点都远离整个放大器闭环工作的3dB带宽,这样才能保证放大器闭环工作的稳定性。通常的预放大电路如图1(c)所示,它在其输出端引入值为1/(gMLCeff)的极点(gML为管ML的跨导,Ceff为预放大电路输出端(节点①)的等效负载电容,主要是管M2的栅电容)。

电路设计中,为了获得大的跨导,管M2尺寸一般较大,带来的问题是较大的寄生栅电容,从而导致节点①处的极点频率较低,影响整个电路的速度或稳定性,而要将该极点推倒足够高的频率,需要较大的功耗。本文下面要介绍的是我们设计的一种结构新颖的放大器,用它作为预放大级可以解决普通预放大电路由于负载电容较大带来的稳定性问题,并且不需要增加太多的功耗。该放大器驱动一单级放大器所构成的两极运放在有效负载电容为4pf的情况下实现了超过1GHz的增益带宽积,其功耗与同性能的其他结构放大器相比大大降低。

放大器结构及工作原理

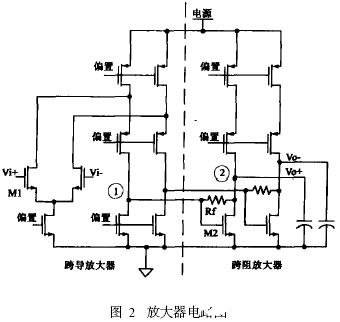

我们所设计的放大器如图2所示,它由两部分构成,虚线左侧为折叠共源共栅的跨导放大器,右侧则是由电阻反馈所形成的跨阻放大器。跨导放大器的特点是高输入阻抗和高输出阻抗,而跨阻放大器则是低输入阻抗和低输出阻抗,它们的结合构成了具有低输出阻抗的电压放大器。下面对该电路进行具体解释。

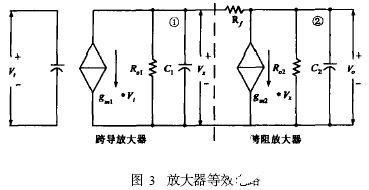

为简化分析,忽略非关键节点极点的影响,将放大器简化为图3所示的等效电路:Ro1、Ro2、C1、C2分别为节点①、②处的等效电阻和有效负载电容;Rf为反馈电阻,它分别连接于共源放大器的输入和输出端,形成电压并联负反馈,降低该级的输入输出电阻;gm1、gm2则分别为管M1、M2的跨导。由于Ro1、Ro2均为很大的电阻(远大于1/gm1或1/gm2),其影响可以忽略不计。需要特别指出的是,该电路的设计必须满足C1≤C2(实际电路中一般都很容易满足该条件),下面的讨论都是在这个前提条件下进行的。

根据基尔霍夫电流定律列方程:

gm1Vi+VxsC1+(Vx-V0)/Rf=0(1)

gm2Vx+V0sC2+(V0-Vx)/Rf=0(2)

解方程组得:

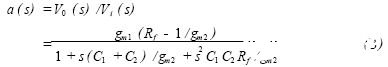

由传输函数看出,该放大器可以等效为一二阶系统,其直流增益为:

A=gm1(Rf-1/gm2)(4)

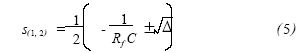

它的极点就是方程1+s(C1+C2)/gm2+s2C1C2Rf/gm2=0的根,值为:

其中,

因为C2≥C1

所以,C≈C1,C1+C2≈C2(7)

当Δ≥0即C1+C2≥gm2RfC时,方程有两实根,即放大器有两个实极点

由式(8)、(9)看出,随着C2的增加极点s1的绝对值显著减小,即极点频率随C2的增大而降低,这不利于放大器的稳定。

当C1+C2

公式(10)表明,共厄极点的实部取决于C1,几乎不受C2值的影响。合理的电路设计可以保证C1是一个很小的值,从而使整个电路的极点位于很高的频率。

由上面的分析可以得到以下结论:当C1≤C2,并且C1+C2模拟结果

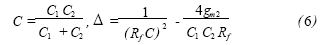

利用我们所提出的预放大电路,设计了图4所示的运算放大器。它是两级结构,前级为预放大电路,后级为套桶式放大器。

若需要更高的直流增益或者较大的输出电压摆幅,图中所示单级放大器可以采用增益自举放大器。

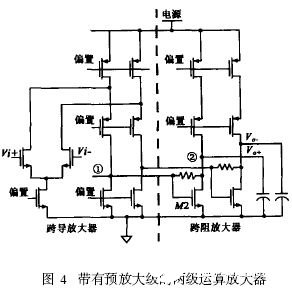

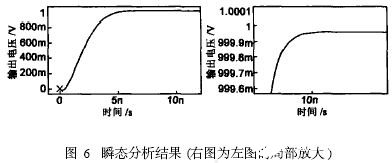

该两极运算放大器用于实现8倍的闭环增益,用0.35μmCMOS工艺模型在Spice中进行模拟,模拟的电路示意图见图5。当输入为0.125V的阶跃信号时,Hspice瞬态分析的结果如图6所示:

由模拟结果得到运算放大器的各种参数值如表1所示:

若去掉预放大级而仅仅采用后面的单级放大器,即使将输入管的尺寸加倍,也需要高达80mW的功耗。并且增大输入管的尺寸会使放大器的输入端寄生电容增加,而应用于流水线ADC中时,该电容会影响ADC的各项性能。

与单级放大器相比,图4所示电路还有一个突出的优点:输入共模范围大。当然单级电路也可以采用折叠共源共栅结构来增加输入共模范围,但采用这种结构会使功耗大大增加。

对于预放大级,从Hspice的输出文件中提取各项参数代入(4),(10)中进行计算,计算结果与模拟结果对比如表2:

可以看到,理论计算值与实际模拟结果十分接近,证明了前面所做推导的正确性。

总结

本文介绍了一种适用于高速高精度流水线ADC的运算放大器,它是带有预放大级的两级结构。其中,用做预放大级的放大器是由我们特殊设计的,它在负载电容较大的情况下仍能达到很高的带宽,我们对它的传输函数进行了理论推导,模拟结果证实了推导结论的正确性。用0.35μmCMOS工艺所设计的该类型运算放大器在负载电容为4pf的情况下,实现了超过1GHz的增益带宽积,功耗仅为25mW,远低于同性能其他结构的放大器。

责任编辑:gt

-

ADS5421流水线式模数转换器(ADC)数据表2024-07-30 460

-

ADS5237流水线式模数转换器(ADC)数据表2024-07-29 551

-

ADS828流水线式CMOS模数转换器数据表2024-07-23 528

-

ADS5422流水线式模数转换器(ADC)数据表2024-07-16 599

-

如何设计一种适用于流水线ADC的运算放大器?2021-04-22 1589

-

模数转换器如何知道流水线ADC及其使用方法?2021-03-11 1499

-

MAX1200中文资料,pdf (流水线结构的模数转换器)2009-10-02 630

-

流水线型模数转换器MAX1200及其与DSP的接口2009-04-28 795

-

一种流水线结构AD转换器的速度分析方法2008-12-03 889

全部0条评论

快来发表一下你的评论吧 !