基于数字可编程可变增益放大器实现数字分析仪前端模块的设计

测量仪表

描述

(文章来源:,作者:隋绍勇,孙义卓,任仲平)

引言

示波器和频率计是电子测量的常用仪表,其前端电路的设计对于仪表整体的性能指标起着十分关键的作用。本文主要介绍一款基于AD8260的数字分析仪前端模块的设计方法。AD8260是AD公司生产的一款大电流驱动器及低噪声数字可编程可变增益放大器(DGA)。该器件增益调节范围为-6~+24 dB,可调增益的-3dB带宽为230 MHz,可采取单电源3.3 V、5 V或+/-5 V双电源供电。主要用于数字控制自动增益系统、收发信号处理等领域。本设计主要使用其数字控制自动增益功能。

1 设计原理

该数字分析仪包含示波器和频率计两大功能。频率计功能分为高频段和低频段两部分,其中20 MHz以下频率信号由采样后的示波器来测量;高于20 MHz的频率信号则由频率计通过等精度算法实现。为提高测量精度,本设计采用高稳定度的恒温晶振来为系统提供时钟源,通过FP-GA内置锁相环为各模块提供各时钟信号。而对于100 MHz带宽示波器功能的实现,若由单芯片的超高速采样来实现,则要对采样后的高速信号进行存储,这种方法不易实现,且对电路的工艺要求也很高。为了避免这种情况.本设计参考了TEKtronix公司的100 MHz示波器的设计,因而采用了3片ADC来实现对输人信号的分时采样,并在分别存储后由DSP处理。

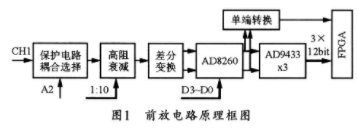

本文主要介绍数字分析仪前端模块的设计。由于示波器的输入信号幅度范围一般为+/-5Vpp,而AD9433 (AD采样芯片)的输入信号幅度要求不大于2Vpp,因此,在采集电路的前端加入信号衰减和信号增益两级幅度调整电路,可保证测量的正确性,提高测量的精确度。与NI的数字分析仪不同,本数字分析仪的频率计功能不是由超高速采样后通过数字信号分析来实现,而是根据等精度频率测量的原理来实现的,这样可以大大降低仪表的造价。同时,考虑到仪表的便携性及工程人员的应用习惯,本仪器只提供了单通道输入,没有设计外部触发通道,因而简化了仪表的体积,同时降低了设计的难度。数字分析仪前端模块的原理框图如图1所示。

本系统的输入信号经过压保护电路及交直流耦合选择后,将进入高阻衰减网络,并通过外部控制信号实现对输入信号的1:1、1:10的高阻衰减,衰减后的信号经差分变换后进入AD8260进行程控增益,程控增益后的信号一路直接进入AD9433进行高速采样(此处要求增益后的信号幅度尽量达到AD9433的满量程输入,以提高AD采样的精度),并将采样后的数据送入FPGA进行相应处理,从而实现示波器功能;而程控增益后的另一路信号则通过单端变换进入FPGA进行相应的处理,进而实现高频频率计数功能。

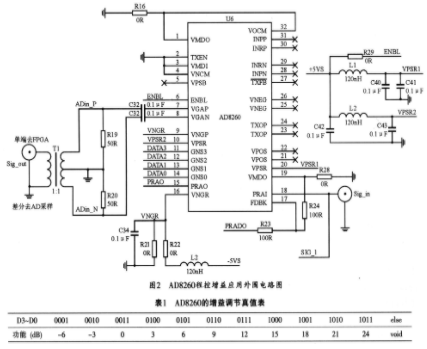

图2所示是AD8260的外围电路,其中AD8260芯片采用±5 V双电源供电,也可以通过跳线实现+3.3V单电源供电。即将-5VS接地,R21焊接,R22断路,+5VS接+3.3 V。

2 设计电路

数字分析仪前放电路中的耦合选择及衰减控制电路如图3所示,其中输入信号由CH1通道进入,经D1、D2过压限幅后,通过GPI01控制K2继电器的通和断,以分别选择示波器的直流、交流耦合模式。然后进入1x、1 0x的高阻衰减(由GPI-02控制K1继电器实现),其中C1、C2、C3、R3、R5组成了10x高阻衰减网络。衰减后的信号直接可送往AD8260进行数字程控增益放大。1x或10x衰减后的信号由AD8260的17、18脚输入,经AD8260内部前端放大器6 dB的固定增益放大、-30 dB程控衰减以及末级放大器18 dB固定增益放大后,将由7和8脚输出。所以,模块总的增益范围为-6~+24 dB。AD8260内部的数字程控增益功能框图如图4所示,表1所列是AD8260的增益调节真值表。

当信号由AD8260的7脚和8脚输出后,一路以差分形式直接送往3片AD9433进行时分高速AD采样,以实现100 MHz示波器及20 MHz以下的频率计功能;另一路通过R19、R20组成的电阻匹配网络及T1变压器转换为单端信号送往FPGA直接进行高频信号的频率计数。本设计的FPGA采用ALTERA公司的EP2C20。并通过FPGA内置锁相环对输入的高精度时钟信号进行倍频,其内核时钟为600 MHz,频率计数准确度达10-7的功能。在PCB制版中,因为是高频电路的设计,因此,为了防止各模块电源对电路的干扰,每个模块的电源都要用电感和电容进行隔离和滤波。另外。还要注意数字电路和模拟电路的隔离。

3 结束语

经在实际系统中的调试证明,本文所介绍的方案能有效地实现100 MHz以下信号的程控放大,且成本较低,具有一定的实际意义。

责任编辑:gt

隋绍勇,孙义卓,任仲平-

LMP7312数字可编程可变增益放大器/衰减器数据表2024-06-17 603

-

AN-1578:使用AD5292数字电位器和AD8221输入放大器的低成本、高电压、可编程增益输入放大器2021-05-26 1091

-

AN-137:一种数字可编程增益和衰减放大器的设计2021-05-25 1049

-

LTC6912:带串行数字接口的双可编程增益放大器产品手册2021-04-30 1313

-

数字可编程增益放大器设计方案2019-07-17 2885

-

可编程增益放大器在模数接口的应用2019-05-21 2540

-

低功耗数字可编程增益放大器参考设计2017-05-09 943

-

带可编程增益跨阻放大器和数字同步检波功能的双通道色度计2017-03-05 1121

-

德州仪器可编程差分放大器 绝非一般的可变增益放大器2012-09-26 20325

-

具有负时间常数的数字可编程增益放大器设计2012-08-20 1486

-

AD8555型数字可编程放大器的原理及应用2009-10-30 1927

-

放大倍数在1~15之间可变的可编程增益放大器电路图2009-07-16 2530

-

可编程增益放大器实用电路2008-12-17 1662

全部0条评论

快来发表一下你的评论吧 !