利用连续带通SD ADC组件实现二次变频超外差式接收机的应用设计

模拟技术

描述

便携式无线接收机的主要挑战是在降低功耗的同时,使其动态范围最大化。带有一对时间连续,低通模数转换器(ADC)的直接变频接收机的功耗很低,但是它也容易造成诸如正交性不很好、DC偏移和低频失真等问题,从而限制了产品的动态范围。另一方面,一个二次变频超外差接收机就没有这些限制,但通常由于其复杂性增加,以及需要对较高的中频(IF)信号进行数字化,它的耗电量相对增大。本文介绍了一种频率范围在10“300MHz,带宽 333KHz,动态范围为90dB的混频器和时间连续带通SD ADC组件。电路的耗电量为50mW,这说明低功耗高性能的二次变频超外差式接收机是可以实现的。

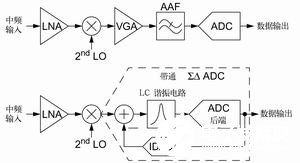

图1 两个超外差式接收机的后端

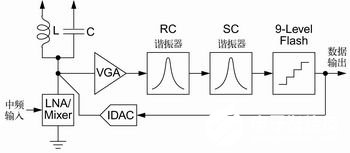

图2 ADC的方框简图

图3 ADC的电路图

图1对将一个中频信号进行数字化的两种方法进行对比。第一种方法需要几种大功率的模块,即,可变增益放大器(VGA),抗混叠滤波器(AAF)和ADC,而第二种方法将此模块用一个带LC谐振电路的带通SD ADC所替代。借助时间连续环路滤波器,带通SD ADC对固有混叠进行保护,省去了AAF。由于ADC的输入噪声较低,且它的电流型输入能提供较强的信号,所以它的动态范围较宽,因此,也省去了VGA。通过将这两个高耗电模块纳入到ADC中,第二种简单的拓扑结构具有节电优势。

图2是较详细的ADC结构。鉴于上述讨论,低噪放(LNA)加混频器的跨导视为gm=10mA/V。低噪放加混频器的输出电流2mApp直接作为ADC的输入,而没有经过不必要的I-V或V-I转换。8个元件的电流型DAC(IDAC)的电流减去反馈数字输出电流,生成一个驱动LC谐振电路的误差电流。LC谐振电路由两个外部5.6mH的电感和一个电容组成。通过一个9位片上电容阵列将电容值微调到所需值的1%以内。LC谐振电路在相关频带内的有效阻抗为Z=6KW,此阻抗将造成12VPP的电压摆动,如果不是来自于IDAC的反馈,IDAC的反馈只能导致以下的电压摆动。前端电路较大的有效增益为gmZ=60,当低噪放有输入信号时,会使ADC后端的噪声由减少到只有。由于此噪声比低噪放/混频器的输入噪声低8dB,因此,ADC的后端对IC噪声特性的影响不大。由于LC谐振电路不产生噪声,加之无失真和不耗电,因此,LC谐振电路是带通SD ADC中理想的第一谐振器。

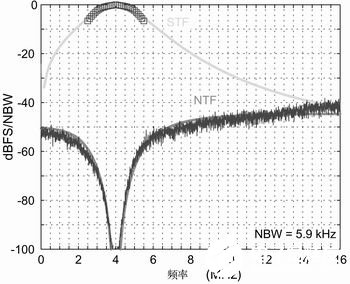

图4 时SFT和NTF图

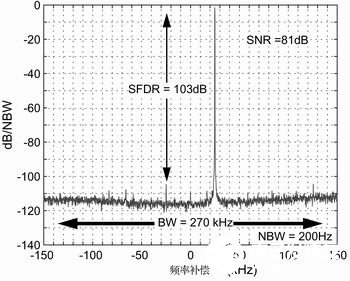

图5 fIF=”103“.25MHz,fLO=100MHz,fCLK=26MHz,OSR=48 时的带内频谱

图6 fIF=273MHz,fLO=269MHz,fCLK=32MHz时SNR与输入功率的关系

VGA通常用于当信号较弱时,通过增益来降低ADC的输入噪声。但是,图2中的VGA是ADC的一个内部元件,它的主要目的是当信号较弱时降低功率消耗。为了平衡大信号的电流,IDAC元件的总电流必须为2mA,但是当信号较弱时,元件的电流可以降低(本方案中降低了1/4),以节省功耗。全面地改变IADC可以相应地改变ADC,使AGC功能得以实现。全面地降低IDAC可以减小ADC后端的信号摆动,并且利用图中的可变增益元件使电路得到最有效的补偿。为了保持调制器的动态范围,VGA的增益会随IDAC的全面波动而反向变动。VGA作为一个其gm值可变的模块,通过改变非退化双极结型晶体管(BJT)差分对中的拖尾电流来控制。

ADC的第二个谐振器也使用了一个LC谐振电路。图3中的VGA和有源RC谐振器消耗2mA的电流,并且不需外部元件就能满足第二级动态范围的要求。可编程电容阵列可以实现RC谐振器的调谐。

为使谐振器的Q值较高、漂移量较低,ADC的第三级使用一个开关电容谐振器。有源RC谐振器功耗较低,但是其Q值较低,漂移量较大,必须使用第四级谐振器。通过调整SC谐振器的Q值和漂移量,使其耗电为1mA。由于开关电容这一级工作在离散时间,此调制器的混叠保护性能不如时间连续系统的好,尽管如此,混叠衰减仍大于80dB。

如图4所示,调制器的通带设计为fCLK/8,较好地协调了期望噪声密度和测量噪声密度。同时,图4描述了一个信号传递函数(STF)。所测量的STF很平坦,在大约500KHz的范围内,每100KHz下降0.1dB。

图5中过采样率OSR=48,时钟频率fCLK=26MHz时,输出频谱的信噪比(SNR)为81dB,非杂散的动态范围为103dB。图6表示fCLK=32MHz时,OSR=48的动态范围为90dB;OSR=960的动态范围为105dB。

责任编辑:gt

-

舒尔SLX4无线话筒接收机原理图:二次变频超外差部分2024-09-29 2884

-

超外差接收机工作的原理是什么 超外差接收机的优点2024-04-08 10090

-

超外差式调幅收音机的安装报告2023-10-25 812

-

请问超外差接收机的工作原理是什么?2021-06-22 4401

-

七管超外差式收音机原理2021-05-25 2378

-

请问低功耗高性能的二次变频超外差式接收机能实现吗?2021-04-20 1470

-

高性能低功耗无线寻呼射频接收机方案2019-07-24 1515

-

高性能低功耗FSK无线寻呼射频接收机方案2019-07-23 2677

-

超外差式收音机原理分析2012-04-11 3861

-

电池超外差式收音机装修技术2011-02-26 1165

-

基于MAX7033的ASK超外差式接收电路设计2010-12-06 1238

-

AM超外差接收机的仿真2009-12-04 1624

-

超外差式收音机2008-01-10 1924

-

超外差式收音机的统调2006-04-16 6410

全部0条评论

快来发表一下你的评论吧 !