Δ-Σ转换器信噪比是如何计算的

模拟技术

2518人已加入

描述

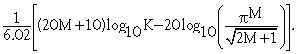

Δ-Σ转换器的性能远超一般简单的模数转换器。它有过采样结构、调节器和数字滤波器。过采样结构在较宽的频率范围内扩展噪声功率。调节器形成低频噪声或将其推到更高频率。数字滤波器可以平滑噪声信号并将其从高频信号中消除。完美的逐次逼近记录寄存器和传递途径信噪比为6.02N+1.76(参考文献1),其中N为转换器位数。Δ-Σ转换器的信噪比是6.02(N+NINC)+1.76,其中,N是调节器位数,NINC是增加的分辨率是:

在这个公式中,M是调节器阶数,K是转换过程中的过采样速率。

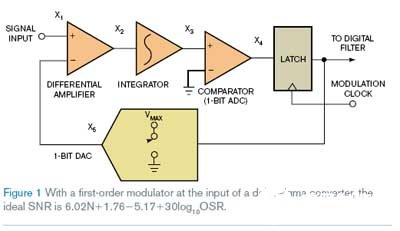

理想的带一阶调节器的Δ-Σ转换器信噪比是6.02N+1.76–5.17 +30log10OSR,其中OSR为过采样速率,N为调制器位数而不是转换器的位数(如图1)。

这些理想公式假定ADC和DAC的噪声和偏移误差为线性的,通常一阶设备是理想的,数字滤波器也会有一个理想的砖墙型反应。事实上,Δ-Σ转换器并不想我们希望的那么理想。

由这些理想的理论,最好的方法仍是依靠转换器性能的基准数据。这些数据给你转换器性能的现实看法。在这个基础上,通过获取上百次直流输入信号的采样,来测量转换器的均方根噪声。在这种情形中,描述任意ADC信噪比的公式是20log10(VRMS-FS/VRMS-NOISE)。

责任编辑:gt

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

升压转换器功率级的基本计算2024-09-10 502

-

计算精密数模转换器应用中的误差预算2023-03-08 2385

-

如何使用电感数字转换器计算工具2022-11-02 539

-

10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响#ADC #SNREE_Voky 2022-08-16

-

145. 逐次比较型AD转换器#AD转换器电路设计快学 2022-07-29

-

反激式转换器的计算公式2022-05-23 7191

-

超低抖动时钟发生器和分配器最大限度地提高数据转换器的信噪比2021-05-18 951

-

Δ-Σ转换器信噪比如何不同?2021-04-08 1217

-

请问信噪比是怎么计算出来的2018-09-13 6135

-

浅谈转换器的噪声2018-08-08 3067

-

高信噪比和失真的双16位/24位高精度Δ-Σ模数转换器2018-06-07 6084

-

转换器的信噪比如何不同2009-12-01 567

全部0条评论

快来发表一下你的评论吧 !