如何选择实时示波器进行抖动测试和分析,有哪些关键因素

测量仪表

描述

随着计算机和通信系统总线速度的显著提高,特别是各种不同的采用内嵌时钟技术的高速串行总线日益普及,定时抖动已经成为影响其性能的基本因素。本文针对当前各种不同的抖动测试工具和方法重点介绍了如何选择实时示波器进行抖动测试和分析,并且探讨了示波器中影响抖动测试结果的几个关键因素。最后针对高精度抖动测试提供了参考方法和测试实例。

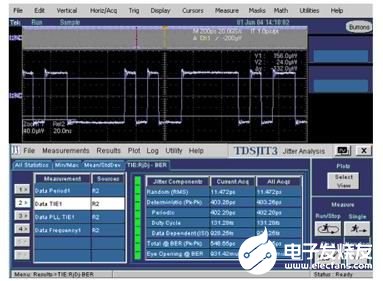

图1:TDSJIT3进行高速数据的抖动测试和分解。

越来越多的高速计算机和通信系统开始采用高速串行总线在芯片间,背板间和系统设备间传送高速数据。在串行数据传输过程中,任何微小的高速时钟和数据抖动都会对整个系统产生巨大的影响,在这种情况下,抖动已经成为设计高速数字系统成败的关键。最典型的应用是传统的33M PCI并行总线正在被采用高速串行技术的PCI-Express取代,它的最新标准支持的数据率已经到5Gb/s,一个UI的宽度才200ps,任何微小的抖动都会导致数据传输错误。从当前各种高速串行总线和数据链路的定时余量规范中表明,在整个数字系统中更加严格地控制抖动是必须的。只有全面有效的测试和分析抖动,其根本原因才能被隔离,从而针对引起系统抖动的原因来减少抖动,提高系统性能和稳定性。像PCI-Express、FBD、InfiniBand、SerialATA和DVI等都对于时钟和数据抖动有明确要求。本文针对示波器进行的实时抖动测试方法,探讨了影响抖动测试结果的关键因素。

典型的抖动测试方法

为成功地设计高速数字系统,不仅需要理解什么是抖动,计算抖动的大小,还需要对不同的抖动分量进行隔离和分解,分析造成抖动的原因,进而避免在高速系统中出现抖动造成的系统故障。在了解抖动测试前,明智选择合适的抖动测试工具和方法成为整个抖动测试工作的第一步。目前有几种抖动测试工具可供选择,误码仪(BERT)直接测试系统的误码率,但是价位昂贵,功能单一,不适合设计人员和调试人员;采用时间间隔分析仪测试抖动也存在功能单一,抖动分析能力不足的限制。高性能数字示波器成为当前最流行的抖动测试工具。

对于数字示波器而言,典型的抖动测试方法主要有2种:

1) 采用数字存储示波器的等效采样模式或直接使用采样示波器,通过直方图统计测量定时抖动。等效采样的缺点是无法消除示波器自身的触发抖动对测试结果的影响,并且由于它采用的是多次触发、多次采集、累计显示的工作方式,对于电路设计和调试而言受到较多的限制,无法进行深层的抖动分析。

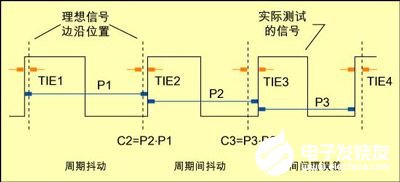

图2:典型的时钟信号抖动测试参数。

2) 更为流行的方法是采用数字存储示波器的实时捕获模式,单次触发,连续采集大量数据,配合相应的抖动测试软件进行抖动测试。对比于等效采样方法它消除由于示波器自身的触发抖动对测试结果造成的影响,并且能够进行复杂的抖动分析和抖动分解得到每一个抖动分量,帮助设计和测试人员分析抖动产生的原因,甚至通过抖动分解估算系统的误码率。例如,在美国国家信息标准委员会(INCITS)下属的T11.2组织在有关抖动和信号完整性方法论(MJSQ)中,推荐泰克实时示波器配合TDSJIT3抖动分析软件进行抖动测试和分析。图1是TDSJIT3实时抖动测试结果。

抖动测试

抖动可以描述为相邻脉冲边沿、甚至非相邻脉冲边沿周期或相位的定时变化。这些指标适合检定长期和短期的时钟和数据稳定性。通过更加深入地分析抖动指标,利用抖动测试结果,预测复杂系统的数据传输性能。

周期抖动用来衡量时钟或数据周期样点的边沿到边沿定时。例如,通过测量1,000个时钟周期上升沿之间的时间,可以对统计的周期取样,统计数据会告诉您信号的质量。标准偏差变成RMS周期抖动,最大周期减去最小周期,得到峰到峰周期抖动。每个不同周期测量的精度决定着抖动测量的精度。

相位抖动用来衡量被测信号边沿相对于一个参考信号边沿的时间偏差,从而可以检测到信号相位中的任何变化。这一指标在许多方面不同于周期测量指标。第一,它单独使用每个边沿,而没有使用“period”或“cycle”一类的说法。第二,它可以测量大的时间位移。边沿相位可以偏离几百或几千度,但仍可以以非常高的精度进行测量(360度等于一个周期或循环时间)。测量相位误差常用的指标是时间间隔误差(TIE),测量结果用相对于度的秒来表示。TIE把信号边沿与参考边沿匹配起来,对各边沿之差相加计算总和。在比较了大量的边沿之后,可以为分析提供一个样点集合。与上面的周期测量一样,标准偏差变成RMS TIE,最大时间减最小时间得到峰到峰值TIE等等。TIE测试精度取决于构成样点集合的各个测量的精度。图2显示的是对一个时钟信号的不同抖动测试参数。

测试精度

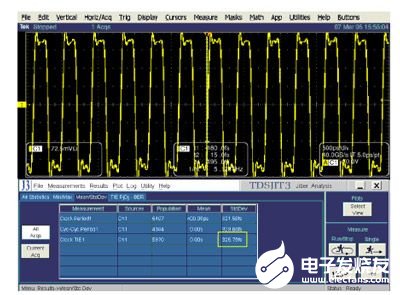

图3:用TDS6154C示波器测量一个稳定信号源。

任何设计人员选择示波器进行参数测量前都会通过产品的指标了解其测试精度,以保证足够的容许误差和测量余量。抖动测试也不例外,例如泰克TDS6804B示波器指明了精度,规定了抖动测量能力的典型值。抖动测试精度受到许多因素的影响,主要包括示波器的定时稳定度、取样噪声、仪器幅度本底噪声和内插误差。

内插误差是由在实际电压样点之间进行线性内插导致的误差。在测量100ps上升时间的信号、示波器以20GSa/s采样率在50%电压门限上进行检测时,这一误差要小于0.3ps RMS。在许多情况下这一误差可以使用示波器中的SIN(X)/X正弦内插及其它方法改善,例如充分利用示波器的垂直动态范围,使输入信号幅度达到示波器满刻度。在大多数情况下,这一原因导致的误差会远小于其它误差源,并且通过使用如Sin(X)/X或Sinc内插,可以进一步减小这一误差。

示波器采样系统中定时元件的稳定性直接影响着定时测量精度。如果时基有误差,那么基于该时基进行的测量会具有同等或更大的误差。示波器中的时基稳定性包括参考时钟、倍频器、计数器等相关电路的稳定性。当通过实时采集模式进行抖动测试时,由于示波器工作在单次触发模式,连续实时采集所有信号,所以它不受仪器多次触发带来的触发抖动影响。

另外两个误差源分别是ADC孔径不确定性和量化误差。这些误差可以表现为幅度噪声和定时噪声,具体取决于取样数据使用的方式。很难区分该误差的实际来源,因为模数转换的时间不同。由于采样头要求有限的时间选通样点(ADC孔径不确定性),任何取样都可能同时包括时间误差和幅度误差。由于ADC分辨率和相关量化误差的综合结果,取样时间和电压样点位置会表现出有限的误差。

最后,幅度噪声是定时测量精度中另一个因素。在快速边沿中,幅度噪声的影响最小,但在边沿速率变慢时,幅度噪声会占据主导地位。这是因为在边沿速率相对于系统带宽变慢时,幅度噪声会改变跨越门限的定时,这样幅度噪声就会变成定时测量误差。

增量时间精度(DTA)

怎样才能确保结果是精确的呢?或者说如何评估示波器的时间测试精度呢?由于抖动测试是时间信息的提取,泰克最早使用“增量时间精度”(Delta Time Accuracy)指明时间测量的精度。这一指标在数字示波器中至关重要,因为它包括前面提到的影响时间精度的多种效应导致的总体影响。

一般增量时间精度(DTA)指标为:

(方程1)

其中SI是取样时间间隔,单位为秒,例如20GS/s采样率下,样点时间间隔为25ps。MI是测量时间间隔,单位为秒。±0.3是示波器采集系统常系数。

采用上面的公式来定义DTA是因为几个不同因素对精度的影响不同。首先是时基精度,一个10.0MHz参考源的校准精度以及校准后是否漂移,都会影响长时间测量结果。例如,在测量一个时间为1.0ms脉冲时,低于皮秒级的影响(如内插误差)相对于0.4ppm校准偏差引起的误差非常小,因为1.0ms×0.4ppm,得到误差达到400ps。

图4:采集10us稳定时钟波形得到的JNF测试结果。

通过使用TDS6804B(8GHz带宽,20GS/s采样率)进行两个时钟测量实例(一个短时钟周期、一个长时钟周期),可以查看主要误差的来源。当测试1.0GHz高速时钟时,使用TDS6804B以20GS/s实时采样率进行采样。根据DTA公式可以得到下面结果:

(方程2)

这是在单次采集或实时采集中进行的任何一项时间测量的峰峰值测量误差。在大量的样本容量(大约1,000次测量值)中,误差的标准偏差一般为0.06×SI+3.5 ppm×MI。在本例中,其约等于3.0 ps RMS(0.06×50ps+3.5ppm×1ns)。

当在测量100kHz时钟时,根据DTA公式可以得到下面结果:

(方程3)

测量误差可能会高达50ps峰值,RMS结果将受到类似的影响,因为时基误差是确定的。在这种情况下,我们看到在测量时间更长时,常数0.3决定的短期效应变得不如时基校准和稳定性对长时间结果的影响明显。在泰克示波器中,采用一种独有硬件技术保证更高的时间测试精度,称为实时内差模式,它作用在示波器采集前端,通过sinx/x内差算法在ADC的样点间插入样点,并且可以调节插入的样点数目,最小样点间隔为500fs。

分辨率

测量分辨率定义了可靠地检测到测量变化的能力。不要把分辨率与测量精度、甚至测量可重复性混为一谈。在定时测量中,分辨率是辨别信号定时中微小变化的能力,而不管变化是有目的的,还是由噪声引起的。

在实时示波器中,定时分辨率受到取样速率、内插精度和基于软件的数学运算库的限制。在使用40GS/s的取样速率和SIN(X)/X内插时,可能会实现几十飞秒的分辨率。由于上面的参考实例中的分辨率基于数学运算库,因此实际分辨能力低于一飞秒(0.0001 ps)。

分辨率是指测量定时中微小变化的能力。但这可能并不一定反映真实情况。当测量变化小于仪器内部固有噪声时会发生什么情况呢?在测量幅度小的噪声或抖动时,必须考虑示波器系统的抖动本底噪声。只知道系统分辨率对理解精度或示波器整体能力的实际极限并没有什么帮助。

抖动本底噪声(JNF)

抖动本底噪声(Jitter Noise Floor)是抖动测量时仪器固有的噪声。在示波器中JNF决定着可以检测到的抖动底限。客观的讲,幅度小于JNF的抖动示波器是观察不到的。尽管某些厂商可能声称可以分辨小于JNF的抖动幅度,但这种能力几乎没有什么参数价值。

检验JNF的方法之一是测量没有噪声的、完美定时的信号。尽管完美信号非常少见,但适当良好的信号源是存在的,可以用来表征抖动本底噪声。一般用于这一测试的常用仪器是具有低相位噪声的高精度RF发生器。

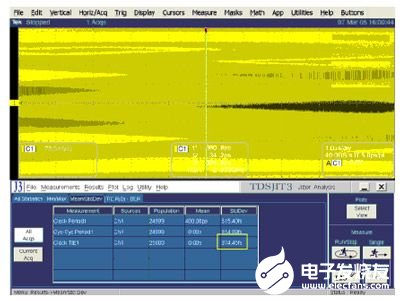

图5:采集1ms稳定时钟波形得到的1K到15G的所有抖动结果。

泰克示波器使用时间间隔误差(TIE)来测量JNF。TIE是最优方法,因为它测试出信号中的任何相位误差,而不管误差具有高频特点还是低频特点,是单次事件误差还是累积误差。此外,在实时示波器中,TIE方法可以将计算得到的完美时钟作为参考时钟源。

内存长度对抖动测试的影响

影响JNF的另一个因素是在测试结果中包括的抖动噪声的频段。所有抖动都具有不同的频率分量,其通常从DC直流到高频部分。因为抖动测试的频率范围是由示波器的高速采集内存的大小决定的,它是单次采集时间窗口的倒数(单次采集时间窗口=高速内存长度×采样间隔时间)。例如,泰克TDS6154C在40GSa/s时实现了64 M的高速采集内存,即一次触发能够以25ps的时间间隔连续采集64M个样点,得到单次采集时间为1.6ms,因此它能够测量最低到625Hz的抖动。在示波器中测量JNF时,还应指明该指标包括的频率范围。泰克示波器一般标称的是在最长记录长度和高采样率下的JNF。

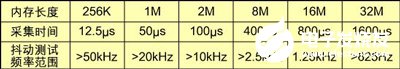

当使用示波器进行抖动测试时,高速采集内存长度是示波器进行抖动测试的关键指标。在示波器的前端放大器和采集电路后面跟随着高速存储电路,它存储ADC转换的采样点。高速内存长度不仅决定了一次抖动测试中样本数的多少,还决定了示波器能够测试的抖动频率范围。表1显示了20GSa/s高采样率下,不同内存长度分析抖动频率范围的大小。

传统示波器设计时采用将高速采集前端(多达80颗ADC)和高速内存在物理上用一颗SoC芯片实现,由于有太多功能在一个芯片内部,导致片内高速内存容量的限制(在40GS/s下一般小于2M),只能测量直到20KHz以上的抖动,并且当需要测试低频抖动时,无法对内存扩展升级。对于大多数应用,测试和分析625Hz到20KHz范围内的抖动信息非常重要。为了弥补这种设计结构的缺陷,这类示波器会采用外部的低速存储器弥补片内高速内存,但外部存储器不能在高采样率下工作,一般只能提供2GS/s,无法提供有意义的抖动测试结果。

TDS6154C采用硅锗(SiGe)半导体集成采集前端,并使用专用的高速存储器。它同时支持最大的带宽,采样率和存储长度。例如,当使用40GS/s实时高速采集时,512K内存一次采集数据量仅为12.5us,只能测试频率范围为80K以上的抖动。在各种串行总线和时钟抖动测试中都很难满足测试要求。

因为内存长度对JNF和实际抖动测试都有至关重要的影响,为了提供和其它示波器厂商的该指标有可比性,泰克还提供了其它情况下的JNF指标。即将TDS6154C示波器的存储长度限制为2M进行JNF测试,以便和其它有内存限制的示波器进行比较。在这一频率范围内,TDS6154C的典型JNF是420fs,该指标比其它类型示波器小一倍。

JNF测试实例

通过和示波器的DTA指标相结合,JNF可以帮助确定该示波器在时间域中进行有效精确测量的能力。图3 所示为泰克TDS6154C示波器测量一个稳定信号源(如BERT或RF发生器)信号的性能。图3测试使用的内存长度约为5ns,TIE测试结果为326fs RMS。这种测试方法对应于其它示波器厂商提供的抖动测量本底噪声指标(JMF),它们的测试方法类似。由于在JMF指标下示波器的时基设置只能测试到大约200 MHz(5ns的倒数)的抖动频率。它无法全面反映该示波器的抖动测试能力,所以泰克示波器提供JNF指标来表征实际情况下抖动测试能力。JMF和JNF指标在绝大多数实际应用环境中不能互换。

表1:在20GSa/s高采样率下不同内存长度分析抖动频率范围的大小。

图3采集5ns稳定时钟波形得到的JNF测试结果(对应于其它示波器厂商提供的JMF指标)

图4表明了使用更长的内存记录长度,连续采集10us信号得到的更合理结果。在这种情况下,TDS6154C 测试的TIE只是略有提高,为374fs。它的采集显示了在更长的采集时间上的抖动本底噪声,其中包括直到大约100kHz(10us的倒数)的低频噪声。这可以更全面地查看信号上超过100K的噪声,但仍不能完全表示示波器的使用方式。当在40GS/s采样率下连续采集10us信号时,需要400K的记录长度。这个记录长度设置已经接近有些示波器的测试极限。

图5表明了在40 GSa/s取样速率、40 Mpts采集内存、连续采集1 ms时间后对稳定的时钟信号进行的TIE测量,这一时间比竞争对手示波器最长的内存长度要长20倍。1ms采集结果中包括从1 kHz直到示波器带宽的噪声来源,本例中的TDS6154C示波器带宽是15 GHz,1ms采集可以直接查看从15 GHz直到1 kHz的信号抖动和调制效应。

通过图3可以看出TIE测试结果约为1.0ps RMS,但更重要的是最大定时误差的峰到峰值。在1 ms采集中,峰值定时误差指标小于±7ps,周期间误差约为±4ps峰值。如果考虑一下目前仪器的典型使用方式,并看一下基于PLL的TIE测量,误差要降低到±3ps峰值以下,在所示的40M采样点、1ms记录中要降低到500fs RMS以下。实际仪器的JNF小于显示的值,因为信号源中也有噪声。

在当前的高速总线标准中,如FBD、PCI Express和DDR2,示波器可以采集和处理长记录长度,显示周期间相关性,检验参考时钟的调制特性,检验PLL和时钟恢复性能。通过图3可以看到TDS6154C在40 GS/s 40Mpt记录长度上拥有非常好的长期性能。

结论

面对当前各种时钟和数据的抖动测试需求,选择合适的示波器和测试方法是第一步。在进行抖动测试前,需要了解示波器对抖动测试精度影响的关键指标和测试方法,例如JNF、DTA等,以及不同测试参数对测试结果的影响,这是保证高精度抖动测试结果的前提。

抖动测试时不仅需要对示波器整体性能进行评估,例如示波器的带宽,采样率,还需要与之匹配的高采样率下的采集内存长度,这样才能测量从接近DC直流到仪器带宽的抖动,同时保持各种相位和谐波关系,对被测信号的抖动有一个全面的分析。

抖动是一种DC到超高频的现象,当试图发现抖动产生的根源时,必需能够查看整个抖动频谱,从不到千赫兹的电源频率直到几百兆赫的相邻时钟和数据频率干扰。TDS6000B/C和TDS7000B系列示波器不仅提供为您提供了与带宽,采样率匹配的高速存储长度,还提供业内最高的抖动测试精度。

责任编辑:gt

-

数字示波器的高精度抖动测试方法2009-10-14 5274

-

精彩研讨会:如何使用实时示波器进行高级抖动分析?2016-10-11 4194

-

示波器的选择2017-09-20 2250

-

安泰示波器维修分享--实时示波器和采样示波器的区别2018-04-26 2294

-

正确选择和应用电缆的5个关键因素2018-11-14 1789

-

RF测量仪器的发展关键因素介绍2019-07-25 1664

-

8步教你进行实时示波器的抖动测量2020-02-28 4188

-

从抖动分析到相噪分析2020-03-09 2207

-

如何利用高带宽实时示波器进行C-RAN组网时的CPRI时延抖动测试2021-05-07 1919

-

请问影响固态硬盘寿命的的关键因素是什么?2021-06-18 2068

-

测试测量仪器选择的关键因素2012-01-08 2148

-

实时示波器抖动测量执行步骤2019-10-03 10388

-

PCB材料选择的关键因素2020-10-28 3094

-

选择晶振元器件的关键因素2023-07-05 1641

-

选择处理器的几个关键因素2023-12-15 1972

全部0条评论

快来发表一下你的评论吧 !