高速模数转换器的性能分析及时钟抖动会对其造成什么影响

模拟技术

描述

对高速信号进行高分辨率的数字化处理需审慎选择时钟,才不至于使其影响模数转换器(ADC)的性能。借助本文,我们将使读者更好地理解时钟抖动问题及其对高速ADC性能的影响。

我们将以凌力尔特(LTC)最新推出的高性能16位、160Msps的ADC LTC2209为例进行说明。LTC2209具有77.4dB的信噪比(SNR),100dB 基带无寄生动态范围(SFDR)。

与当今市场上的许多高速ADC一样,LTC2209也使用采样-保持(S&H)电路,该电路本质上是对ADC输入的点取(Snapshot)。当采样-保持开关闭合后,ADC输入网络被连至采样电容。在开关打开的那一刻(1/2时钟周期后),采样电容上的电压被记录并保持。

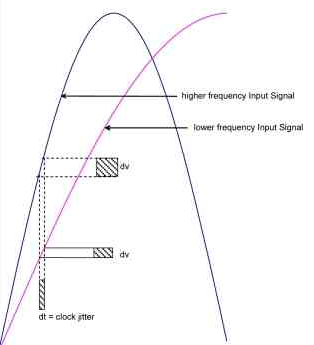

开关打开时间上的变异被称为孔径不确定性(aperture uncertainty),或称为抖动,它将产生一个与抖动或输入信号斜率成比例的误差电压。换句话,输入频率越快、幅值越高,则越易受时钟源的影响。图1显示的是斜率与抖动的关系。

钟描述为“低抖动”已变得几乎毫无意义。这是因为它对不同的关注者意味不同。对可编程逻辑供应商来说,30皮秒、甚至50皮秒都可被认为是低抖动的;相反的,根据输入频率的不同,高性能ADC需要的时钟抖动应在1皮秒以内。

在频谱的最高端将出现满量程信号,否则与对最高频率成分的简单化处理不同,更精确地来讲,采样后信号的频谱功率分布才是决定性因素。举个简化的例子,从DC到1MHz的均匀频带功率在1MHz的等值功率时比单频或窄带的灵敏度低6dB。

任何情况下,都有各种因素会造成抖动,除ADC本身内部的孔径抖动外,还有振荡器、各种频率分割器、时钟缓冲器和由耦合效应引入的任何噪音等其它多种因素。

C2209的内部孔径抖动是70fsec(1fsec=10-15秒)。就LTC2209和LTC其它高速16位系列ADC所表现出的性能看,在某些采样情况下,0.5皮秒的抖动(大多振荡器供应商所能提供的最高指标)就可对SNR产生明显影响。决定所需要的抖动性能的不是ADC,而是具体采样情况。

在140MHz输入频率下具备77dB SNR的ADC都需要相同的抖动性能,以便不折不扣地实现数据手册上标注的SNR。就抖动性能来说,决定性因素是输入频率而非时钟频率。就LTC2209来说,带10皮秒抖动的时钟将在1MHz输入频率仅产生0.7dB的SNR损耗。在140MHz,SNR将被降低至41.1dB。

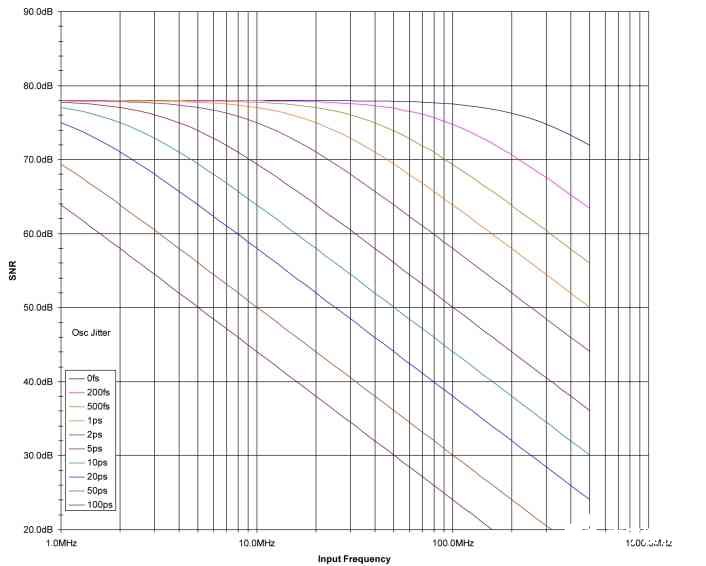

图2显示的是作为采样输入频率函数的时钟抖动对LTC2209的SNR的影响,它包括从完美时钟到带100皮秒抖动时钟所逐渐增加的一系列时钟曲线。在100皮秒,ADC的SNR在输入仅为200kHz时就开始恶化。

时钟抖动对SNR影响的理论极限是:

其中,fin是输入频率、s是以均方根(RMS)秒表示的抖动。

与抖动相关的噪声功率与输入功率(dBFS)成比例。随着输入电平的增高或降低,与抖动相关的噪声成分也相应改变。例如,若我们在70MHz IF有-1dBFS的输入信号并用带1皮秒抖动的时钟进行采样,则我们可预期一个68dBFS的SNR。在-5dBFS,与抖动相关的噪声成分将下降4dB、达72dBFS。

责任编辑:gt

-

模数转换器最高使用频段2025-12-16 825

-

数模和模数转换器2009-09-16 7964

-

NXP 高速模数转换器2012-08-14 2772

-

AD9213BBPZ-10G 标准高速模数转换器2020-03-02 2083

-

高速模数转换器的转换误码率分析2020-12-22 1752

-

高速模数转换器的转换误差率分析2021-04-06 1379

-

时钟抖动会对高速ADC的性能有什么影响?2021-04-08 2449

-

谁来讲解一下高级动态性能模数转换器是什么?2021-04-12 1555

-

高速率的逐次逼近模数转换器ADS8412是如何设计的?2021-04-14 2252

-

如何降低模数转换器的性能2018-12-12 5094

-

模数转换器的性能及时钟抖动对其造成的影响分析2020-08-01 2000

-

AN-1221: 使用ADF4002 PLL产生高速模数转换器所需的极低抖动编码(采样)时钟2021-03-19 864

-

高速模数转换器ADC基础知识2022-09-20 757

-

为高速数据转换器设计低抖动时钟2023-02-25 4462

-

探索ADS900:高速10位模数转换器的卓越性能与应用2025-12-10 732

全部0条评论

快来发表一下你的评论吧 !