基于TMS320C6x系列DSP的并行处理方法优缺点分析

处理器/DSP

描述

在通信、雷达等系统中,特别是在3G无线基站等系统中,随着输入语音 数字和分组数据量急剧增加,系统的处理能力也需要急剧增加,这需要一种功能强大的大型并行阵列信号处理系统。系统往往需要进行非常复杂的数据处理,虽然 DSP技术得到了飞速的发展,出现了高速DSP芯片,但是使用单个DSP芯片还是不能适用系统的需求,迫切需要把多个DSP组成互联系统,以增强整体数据 处理能力。本文主要研究TI公司的TMS320C6x系列DSP的主机接口(HPI)、多通道缓冲串口(McBSP)以及AD公司的ADSP2106x系 列DSP的链路口(Link),介绍了利用其组成DSP并行系统时各种互连方法和优缺点。

1 TMS320C6x简介

TMS320C6x内部主要包括1个中央处理器单元(CPU),1个程序内存和一个数据内存,DMA,1个外部存贮器接口(EMIF),1个主机接口 (HPI),2个多通道缓冲串口(McBSP),TMS320C6x的CPU 内部有8个处理单元,每个时钟最多可处理8条指令。TMS320C6x的接口灵活,处理能力强,运算速率高,因此在民用和军用领域都将有广阔的应用前景, 在军事通信、电子对抗、雷达系统、精确制导武器等需要高度智能化的应用领域,这种芯片的高速处理能力具有不可替代的优势。

2 利用TMS320C6x的HPI组成多DSP互联并行系统

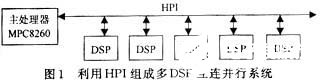

主机口HPI是一个16/32 b宽度的对外接口,外部主机(也叫做上位机)掌管该接口的主控权,外部主机可通过HPI直接访问DSP的存贮空间。另外,主机还可以直接访问 TMS320C6x片内的存贮映射的外围设备。复位时向DSP加载程序,对DSP进行控制。外部主机是HPI的主管方,DSP是HPI的从方。主机可以通 过HPI访问DSP,但DSP不能通过HPI向外部进行访问。在这类系统中,通常包括一个主处理器和很多从处理器,主处理器一般是通信控制器,例如 MPC8260,MC68360等,当然TMS320C6x也可以作为主处理器,用来进行对系统的输入输出数据及整个系统进行进行管理。从处理器一般是多 个DSP(如TMS320C6x),用来进行算法处理。主处理器通过HPI向DSP加载程序,对DSP进行控制,可以通过HPI向DSP写入待处理的数据 或通过HPI读取DSP处理完的数据,DSP之间的数据可以通过HPI由主处理器进行中转。如图1所示,主处理器可以直接连接多个逻辑。此方法结构简单, 但主处理器负担较重,和多个DSP通信效率较低,且主处理和DSP阵列需要在同一块单板上。

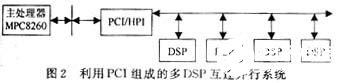

另一种方法如图2所示,主处理器PCI总线连接到PCI/HPI接口转换控制芯片上,接口 转换芯片控制多个DSP并完成主处理器和DSP之间、DSP相互之间的数据交换。此时主处理器和DSP阵列可以不在同一块单板上。在该系统中(若主处理为 MPC8260,需增加8260到PCI总线的桥片),HPI/PCI接口转换控制芯片是整个系统设计的关键,可选TI公司的PCI2040,PLX公司 的PCI9054,Tundra公司的Tsi920。

主处理器也可以通过TMS320C6x来充当,利用DSP的HPI接口组成一个多DSP互 连并行系统,一般是一个主处理器和一个从处理器,此种方法的一个应用实例是在雷达中的应用。滑窗算法是数字信号处理中一种常用的基本算法,但滑窗算法一般 是遍历性的算法,其运算量大,在实时处理中受到限制。利用2片TI公司的高速DSP芯片TMS320C6201,应用其HPI接口并行实现多种滑窗算法, 满足了某雷达系统解模糊的实时需要。系统由2片TMS320C6201完成所有的数字信号处理算法,主要是多重滑窗算法。根据实际系统的需要,将多重滑窗 算法处理分布在2片TMS320C6201上,利用其HPI接口完成多处理机之间的快速数据交换,构成多机并行处理系统,完成多重滑窗算法的多机并行处理。整个系统的基本框图如图3所示。

3 利用TMS320C6x的McBSP组成的多DSP并行互连系统

McBSP称为多通道缓冲串口,他有一个发送端口和一个接收端口,多个DSP可以通过McBSP连接到一个串行时际交换芯片,采用时际交换的方式进行数 据交换。数据收发以帧为单位进行。每个发送帧分成n个发送时隙,不同的发送时隙对应不同的接收DSP,例如:DSP0的发送端口在时隙1给DSP1发送数 据,在时隙2给DSP2发送数据,在时隙n给DSPn发送数据;每个接收帧分成n个接收时隙,不同的接收时隙对应不同的发送DSP。例如:DSP1的接收端口在时隙0接收来自DSP0的数据,在时隙2接收来自DSP2的数据,在时隙n接收来自DSPn的数据。这种方法的优点是接口简单,可以实现多个 DSP的全互连来进行并行处理。缺点是数据以串行方式传输,速率较低。

4 利用ADSP2106x的Link口组成多DSP互连并行系统

首先对ADSP2106x做一简单介绍。ADSP2106x是一种高性能的32 b数字信号处理器,采用超级哈佛结构。内有3条片内总线,他们是PM总线(程序存贮器)、DM总线(数据存贮器)和I/O总线。PM总线既可用来访问指令,也可以用来访问数据。在一个单周期内,处理器可以访问2个数据,一个通过DM总线,另一个通过PM总线,而指令要到指令缓冲中去取。他的外部口提供与 外部存贮器、存贮器映像I/O、主机处理器、多处理机系统中的其他ADSP2106x连接的接口。外部口完成内部和外部的总线仲裁,并且向共享的全局存贮 器和I/O设备提供控制信号。最显著的特点是提供了6个链路口,为多DSP并行处理提供了很大的方便。

ADSP2106x提供了6个链路口, 每个链路口包括4位数据线、1个双向时钟信号、1个双向确认信号、链路握手信号,每个链路口可以按2倍时钟频率的速率进行数据传输。可以独立工作或同时工 作,链路数据可以打包成32 b或48 b数据,可以被处理器核访问,可以与片内存贮器进行DMA传送,外部主机可以直接访问链路口。具有双缓冲的发送和接收寄存器。可通过时钟/确认信号在链路 口通信时握手,每个链路口均可收/发数据,并分别有一个DMA通道支持。由于有6个链路口,所以若数据总线采用紧耦合的方式,则一组多DSP最多可以有6 个DSP。

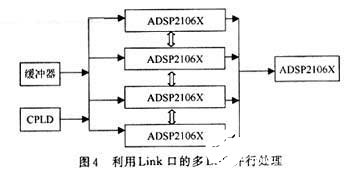

ADSP2106x的Link口的并行处理功能在实际中已得到广泛的应用。在雷达、通信等中都有成功应用的实例,利用Link口为了完成大量的的复杂数据运算且实时性要求高的系统,方法如图4所示。数据通过缓冲区送过来,然后在CPLD的控制下通过发送中断选择第几个DSP芯片,按照CPLD的控制依次将数据通过主总线送给各个DSP进行FFT和恒虚警处理,然后由后端的DSP通过软件控制从Link口依次将各个DSP处理的结果送 到后端的DSP进行处理,缓冲器通过数据总线将数据送给各个DSP,由于CPLD的控制,所以数据总线不会发生冲突。且紧耦合在一块的各个51DSP通过 Link口互相传送数据,各个DSP也通过Link口将处理结果送给后端DSP。这种方法在雷达中已得到成功的应用。当然ADSP2106x利用Link 口进行并行处理的方法在通信中也得到广泛的应用,例如在扩频通信中利用2片ADSP2106x也得到成功应用。利用Link口组成多DSP互连系统方法灵活,除上面所述外,还可根据实际情况进行处理。

5 结 语

不同的应用需要的处理能力不同,对各个DSP之间,DSP与主处理器之间的数据流量和时延要求也不同,故需要的DSP数目、互连方式也不同。利用 DSP不同接口的互连方式,HPI有利于外部主处理器对各个DSP进行控制,适合于主从处理器和多个DSP构成主从方式的互连系统。McBSP接口简单, 适用于对传输速率要求不高的低速全互连并行系统。对于ADSP2106x,由于其Link口的特点,特别适合与构成多种不同的并行多处理系统,在高速实时 处理系统中得到了广泛的应用。

责任编辑:gt

-

TMS320VC55x系列DSP在线烧写方法2010-12-23 1037

-

DSP并行处理的方法2009-11-03 32397

-

DSP的各种并行处理方法和优缺点2019-04-08 4311

-

TMS320C6748 VEM-esay开发板例程中没有#define _TMS320C6X语句2019-04-30 1732

-

DSP的并行互连方法有哪些,其各自的优缺点是什么?2021-04-08 1513

-

TMS320C55x DSP是什么?有什么应用?2021-04-14 2057

-

TMS320C6X DSP结构与测试方法研究2009-11-27 1091

-

TMS320C54X DSP实现UART的技术2009-09-27 1320

-

DSP applications using C and the TMS320C6x DSK2016-06-21 830

-

基于TMS320C6000系列DSP的Flash编程方法2017-10-19 1171

-

TMS320C55x DSP并行处理技术分析2017-11-03 1512

-

关于TMS320C28x系列DSP的指令和编程指南2018-04-04 2557

-

TMS320C64x+ DSP 大字节DSP库 程序员参考2018-04-13 1643

-

TMS320C64x to TMS320C64x+ CPU 迁移指南2018-04-17 1335

-

TMS320F281x与TMS320C281x DSPs:功能特性与应用指南2026-04-23 318

全部0条评论

快来发表一下你的评论吧 !