便携式边界扫描故障诊断仪的软硬件设计与实现

测量仪表

描述

边界扫描原理剖析

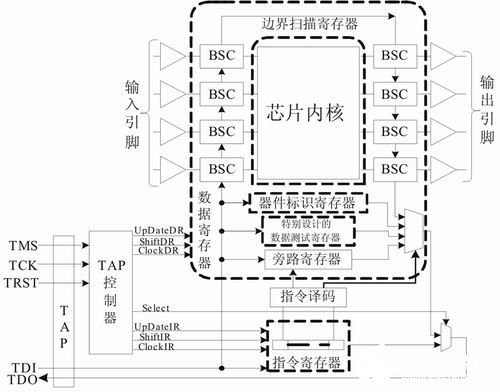

边界扫描技术的核心思想是在器件内部的核心逻辑与I/O引脚之间插入的边界扫描单元,它在芯片正常工作时是“透明”的,不影响电路板的正常工作。各边界扫描单元以串行方式连接成扫描链,通过扫描输入端将测试矢量以串行扫描的方式输入,对相应的引脚状态进行设定,实现测试矢量的加载;通过扫描输出端将系统的测试响应串行输出,进行数据分析与处理,完成电路系统的故障诊断及定位,边界扫描测试原理示意图如图1所示。

图1 边界扫描测试基本原理示意图

边界扫描测试的物理基础是IEEE1149.1边界扫描测试总线和设计在器件内的边界扫描结构,标准的边界扫描结构如图2所示。其中边界扫描测试总线由测试数据输入(TDI)、测试数据输出(TDO)、测试时钟(TCK) 、测试模式选择(TMS)和复位信号(TRST)五根信号线组成。而标准的边界扫描结构就是在器件内部的核心逻辑I/O引脚增加了边界扫描单元(BSC),同时还增加了和边界扫描测试相关的指令寄存器、数据寄存器、测试访问端口TAP控制器等电路。在测试状态时,边界扫描结构可以对数据寄存器或指令寄存器进行操作,即从TDI端口把测试矢量移入边界扫描单元,从TDO端口把测试响应移出。

图2 标准边界扫描结构

总体设计方案

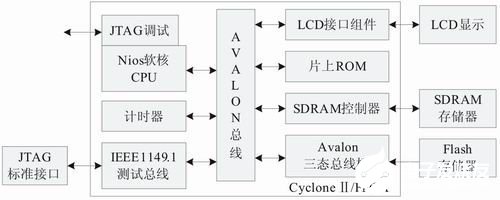

便携式边界扫描故障诊断仪需要根据被测系统电路的描述文件生成边界扫描测试矢量,然后转换为IEEE1149.1边界扫描测试总线信号自动加载到被测系统中,同时从TDI引脚自动读取边界扫描测试响应进行分析处理,根据边界扫描相应算法作出故障诊断决策及定位隔离,最后通过LCD显示诊断结果。本文采用片上可编程系统解决方案将便携式故障诊断仪进行软硬件协同设计在一片FPGA上,使所设计的电路系统在其规模、可靠性、体积、功耗、上市周期、开发成本、产品维护及硬件升级等多方面实现最优化(整体结构示意图如图3所示)。

图3 便携式边界扫描故障诊断仪电路结构示意图

硬件设计

本文采用Altera公司嵌入软核Nios处理器的FPGA作为载体来实现边界扫描故障诊断仪的SOPC系统。边界扫描故障诊断仪主要实现边界扫描测试矢量的生成、JTAG总线信号发生器、边界扫描故障诊断应用软件、故障显示等功能,是便携式边界扫描故障诊断系统的核心。利用SOPC Builder创建Nios软核CPU并进行参数化配置,同时构建储存器、计时器、LCD接口组件、IEEE1149.1测试总线用户逻辑为一体的SOPC系统,边界扫描故障诊断片上可编程系统内部模块配置图如图4所示。

图4 边界扫描故障诊断SOPC系统内部模块配制图

本文利用向导式界面灵活定制边界扫描故障诊断系统,采用标准型Nios II软核处理器,并添加了4K字节的指令缓存Cache。同时为了方便调试边界扫描故障诊断系统的软硬件,在处理器模块中添加JTAG调试单元,在SOPC系统软硬件调试成功且能独立运行后,也可以将JTAG调试单元去掉。

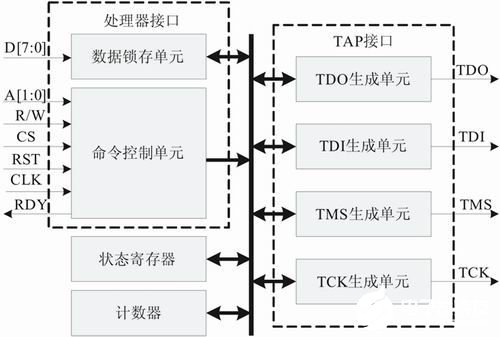

可复用IEEE1149.1测试总线控制器IP核是边界扫描测试控制器的核心,也是整个边界扫描测试平台设计的关键所在。本文设计的IEEE1149.1测试总线控制器IP核主要功能包括:产生边界扫描测试时钟TCK、对被测系统电路输出TMS控制序列、读取被测系统的测试响应和加载测试矢量、与SOPC系统中的微处理器进行通讯及测试数据交换和在TCK和TMS配合下控制被测系统中TAP控制器完成边界扫描测试的全部过程。

在IP核的开发过程中采用IC的设计思想,首先根据功能需求确定外部接口,然后划分内部结构单元,通过实现内部每个小单元的功能,最后组合完成JTAG总线控制IP核的整个设计,JTAG总线控制逻辑内部体系结构图如图5所示。其中TDO缓冲模块主要由FIFO、计数器、并/串转换及控制部分组成。

图5 jTAG IP 核内部体系结构图

系统软件开发

mc/os操作系统移植

将mC/OS-II移植到Nios软核CPU平台上,只需修改与处理器相关的代码OS_CPU.H、OS_CPU_A.ASM、OS_CPU_C.C三个文件。同时根据本系统的功能需要,用OS_CFG.H配置内核设置系统的基本情况以及整个实时系统所需要内核和用户的头文件INCLUDES.H。根据各个任务的重要性和时间关键性,设定每个任务的优先级,以便任务调度之用。

故障诊断软件

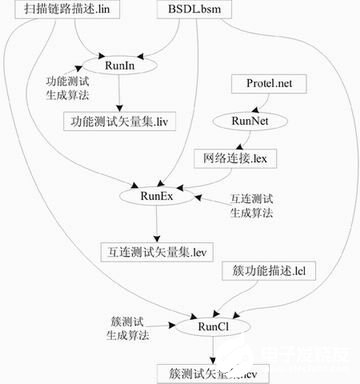

故障诊断软件首先根据预先固化在Flash存储器中的被测系统的边界扫描描述文件(BSDL)和网络表等描述文件生成两个测试数据文件:系统链路信息文件和器件间互连网络节点文件。同时还需要获得测试器件物理引脚号码和器件边界扫描单元的对应关系。然后根据相应的边界扫描测试算法和不同的测试内容生成测试数据:测试指令代码、完整性测试数据、互连测试数据、芯片功能测试数据并且加载到被测系统扫描链路中及读取边界扫描测试响应。其次分析处理测试响应数据,剔除扫描链中垃圾数据,提取获取故障诊断有用信息。最后根据测试内容不同,进行扫描链路完备性测试故障诊断、互连测试故障诊断、器件功能测试故障诊断、簇测试故障诊断作出诊断结果。边界扫描测试故障诊断数据流程图如图6所示。

图6 数据流程图

结语

本文设计的便携式边界扫描故障诊断仪不同于传统的边界扫描设备,不依靠PC就可实现边界扫描测试与诊断,特别适合特殊领域的现场在线使用。尤其是在测试时间方面,克服了PC机上应用软件与边界扫描控制器之间数据传输的延时的缺点,直接进行边界扫描测试矢量的加载和读取,大大提高了边界扫描测试诊断的效率。

责任编辑:gt

-

汽车故障诊断仪的原理与作用详解2022-06-24 7063

-

如何设计一款基于2.4G射频的车栽CAN总线故障诊断仪?2021-05-13 1400

-

求一种故障诊断仪的设计方案2021-05-12 1898

-

怎么设计一款基于C8051F020单片机的汽车故障诊断仪?2021-05-11 1549

-

如何利用SOPC设计一款便携式边界扫描故障诊断仪?2021-04-12 1379

-

基于CAN总线结合射频和USB实现车载故障诊断仪的设计方案2020-04-13 1766

-

使用C8051F020单片机实现汽车故障诊断仪的研究说明2019-10-24 1123

-

AMEYA360设计方案丨便携式超声仪解决方案2018-07-19 2603

-

关于手持式智能化故障诊断仪的实现2018-04-27 1242

-

基于OBD-的汽车故障诊断仪的研制2016-08-05 1320

-

VLSI边界扫描测试故障诊断2011-07-04 901

-

新型便携式心电监测仪的软硬件设计2010-03-01 1928

-

舰船柴油机燃油系统故障诊断仪的研制2009-07-08 598

-

便携式柴油机诊断仪的研制2009-06-01 1058

全部0条评论

快来发表一下你的评论吧 !