采用FPGA+DSP信号处理硬件结构实现弹载SAR成像处理系统的设计

可编程逻辑

描述

引言

弹载SAR制导是将SAR技术应用于主动雷达导引头,可有效提高全天候、全天时的探测能力。相对于其他模式的制导技术,弹载SAR成像制导技术所需的数据存储量和计算量大,导致其硬件成本、功耗、体积等都难以实现,从而制约了其在精确制导武器装备中的应用[1]。随着微电子技术和数字信号处理技术的发展,FPGA和DSP的强大数据处理能力,解决了弹载SAR制导应用的瓶颈问题,SAR制导技术应用成为近年来精确制导技术研究的热点。弹载SAR成像技术实现的主要难点是数据量大、信号处理复杂、实时性要求高。实时成像要求信号处理系统能够在一定的时间内,完成对回波数据的处理,信号处理的速度必须高于回波信号的数据率。由于DSP应用灵活、处理精度高,早期的信号处理主要采用DSP技术。近年来,由于FPGA采用硬件并行处理架构,数据速率高、资源丰富,易于实现高度并行、流水处理的特点,采用FPGA进行实时处理取得了飞速发展。本文针对弹载SAR成像技术难点,提出了一种基于FPGA+DSP弹载SAR成像信号处理系统的设计方法,该方法解决了数据量大的前端处理和算法实时成像的问题。

1 、系统设计

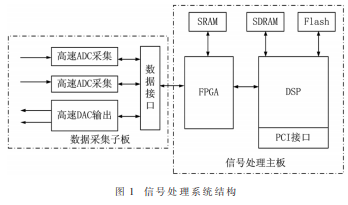

信号处理单元是弹载SAR信号处理系统的核心单元。系统采用FPGA+DSP的信号处理硬件结构,FPGA和DSP分别完成回波数据的预处理和成像算法的实现,所设计的信号处理系统整体结构如图1所示,系统由信号处理主板和数据采集子板构成。信号处理主板主要实现回波数据的预处理、成像算法处理和数据传输接口的扩展,数据采集子板主要完成数据采集和数据输出任务。系统通过AD对线性调频收发机输出的差频信号以100 MS/s的采样率进行采样,将采样后的差频信号传送给FPGA进行信号预处理,FPGA主要完成对差频信号的数字低通滤波,滤除差频信号不规则区的高频分量,并对低通滤波后的信号进行数字正交变换,得到正交的I、Q两路信号。DSP接收到FPGA预处理后的差频信号,对其进行SAR信号处理,主要完成对SAR信号的剩余相位项补偿、距离徙动校正、距离向匹配滤波和方位向匹配滤波。

1.1 A/D转换电路

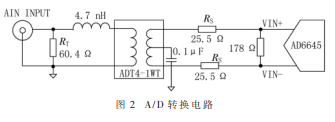

A/D转换电路是信号处理系统的重要组成部分,本文所设计的系统可以同时接收两路中频模拟信号。系统选用AD6645模数转换芯片,AD6645是一款高速、高性能、14 bit单芯片模数转换器,芯片上集成了采样保持器和基准电压源,其最大采样速率可达到105 Mb/s。由于信号会通过衰减和增益级进行处理,AD6645的差分输入不仅改善了片内性能,而且使前端信号输入电路具有高共模抑制性能,能够极大抑制接地和电源噪声等杂声信号。AD6645的差分输入阻抗为1 ,模拟输入功率仅要求为-2 dBm,从而简化了驱动放大器的设计。因此,数据采集子板采用ADT4-1WT射频变压器来驱动AD6645的差分模拟输入,并在变压器副边上使用串联电阻 ,将变压器与A/D隔离开来,以限制从A/D流回到变压器次级的动态电流量,通过射频变压器作为驱动输入不仅不消耗功率,而且所产生的噪声可以忽略不计,A/D转换电路如图2所示。

1.2 FPGA模块设计

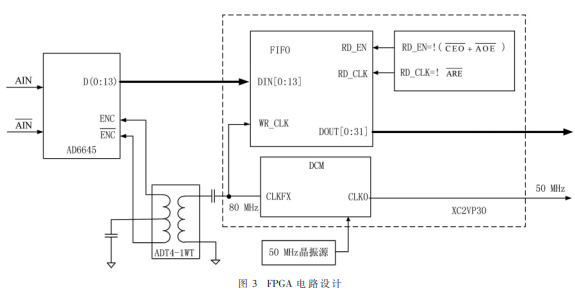

FPGA模块设计的电路如图3所示,系统采用Xilinx公司Virtex II Pro系列的XC2VP30作为数据的预处理。XC2VP30集成了2个32位的PowerPC405处理器硬核、8个I/O Bank、8个DCM、30 186个Logic Cells、136个18×18 bit乘法器模块、13 696个Slice和136个18 KB的Block RAM。系统采用50 MHz外部晶振作为整个系统的时钟源,利用XC2VP30内部的时钟管理器DCM,分别为AD6645、异步FIFO和DSP提供时钟源。DCM输出的CLKFX的80 MHz时钟信号分为两路,一路通过射频变压器ADT4-1WT交流耦合到和引脚,作为AD6645采样时钟信号,保证14位AD输出的精度和低相位噪声。另一路直接送入WR_CLK引脚,作为异步FIFO的写周期。DCM输出的50 MHz的CLK0时钟信号,通过DSP的内部PLL的12倍频为DSP提供600 MHz时钟[6-8]。

1.3 DSP与FPGA接口电路设计

系统采用TI公司32位TMS320C6416作为信号处理主板的核心处理器,其主要任务是实现SAR成像算法。为了实现DSP与FPGA数据高速无误的传输,系统通过FPGA实现异步FIFO把从A/D写入到FPGA的数据准确无误地传送到DSP的EMIF接口[9]。图4所示为TMS320C6416与FPGA的接口连接图,DSP通过EMIF接口与FPGA实现的异步FIFO进行通信,通过设置EMIF控制的存储器为SRAM类型,将FPGA作为DSP的外部SRAM。EMIF为TMS320C6416的外部存储器接口,由EMIFA和EMIFB两个端口组成。系统选取FIFO的宽度为32 bit,深度为192 000,高16位存正交I路信号,低16位存正交Q路信号,采用异步方式传输数据。为设计FIFO的读写使能信号。图5所示为DSP读异步FIFO的时序图。当FIFO缓存达到半满时,HALF_FULL上升沿触发DSP外部中断EXP-INT5,DSP启动DMA以PDT传输模式读取FIFO数据,通过PDT操作,可以实现SDRAM与FIFO之间直接传输数据,而不需要执行2次EMIF操作,提高了数据传输的效率。

2、 成像算法实现

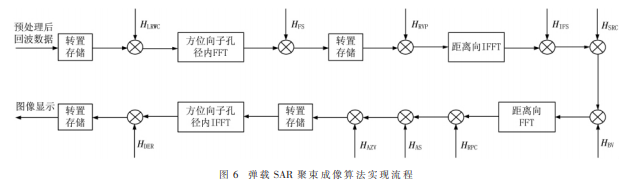

原始回波数据按PRF依次以距离线的形式顺序存入DSP的存储器中,形成一个Na×Nr的数据矩阵,成像算法对数据的处理可分别在距离向和方位向进行。回波数据经过FPGA预处理后,算法处理的第一步由于需要对线性距离走动进行补偿,并对方位向子孔径内的数据进行FFT处理,因此需要首先对输入距离向的数据进行转置存储。同时,由于DSP在成像处理之后按距离线方式将成像结果保存到SDRAM,实现图像显示,因此方位向处理之后还需要增加一次对输出结果的转置存储,这样整个处理过程中共需要四次转置存储处理。在算法处理流程中,需要进行多次的相位因子复乘操作,考虑到系统的实时性,最大限度进行同类运算合并,对距离向处理和方位向处理的补偿因子,可以采用查表的方式得到相应的结果,从而减少成像处理的运算量,提高计算效率[10]。算法中采用子孔径处理实际上是将方位向数据分成二维的数据阵列进行处理操作,实际操作中,DSP可以通过DMA对存储区中数据块进行二维操作,这样可以减小数据重组所消耗的时间,提高程序的执行效率。SAR成像系统是典型的数据流处理系统,处理过程中不需要数据的反馈,弹载SAR聚束成像算法实现流程如图6所示。

3、 实验与分析

系统利用设计的信号处理系统进行外场相关数据测试,测试平台如图7所示,平台由线性调频收发前端、信号处理系统、运动轨道和测试目标四部分组成。收发前端安装在轨道小车上,收发前端可以发射线性调频连续波信号,调制周期在1~10 μs范围内可调,回波信号可调衰减在0~40 dB范围内可调。小车可沿轨道以0~10 m/min速度匀速直线运动,通过收发前端沿轨道匀速直线运动模拟弹载SAR平台。

在外场实验测试中,通过发射信号的同步脉冲信号对回波信号进行间断采样并存储,如图8所示,图8(a)为发射信号与回波信号的时频关系曲线,图8(b)为发射信号的同步脉冲信号。系统开始测试时,选取任一同步脉冲作为方位向起始时间,存储此后一个脉冲宽度T的回波信号;然后利用同步脉冲记录已发射信号的个数,结合系统设置的方位向采样频率,确定下一个需要保存的回波信号起始时间,再存储下一个脉冲宽度的回波信号;重复上述操作,直到采样结束。如图8(b)所示,灰色标记的同步脉冲为信号采样时刻,代表方位向采样点,预设的方位向采样频率为fas,由图可知,fas=1/Tr,则相邻两个方位向采样点之间的脉冲个数N=1/Tfas。

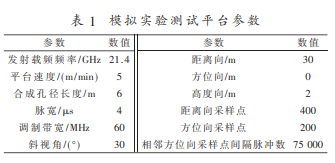

为了获取斜视聚束SAR实测数据,测试过程中,以三角锥反射器作为场景中心目标,其距离轨道垂直距离为50 m,SAR平台天线与轨道垂直方向夹角为30°,模拟实验测试平台参数如表1所示。

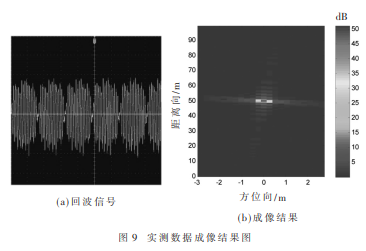

测试平台采集的回波信号如图9(a)所示,经低通滤波后的差频信号进行正交变换,然后送至DSP进行二维组合,最后在DSP中对处理后的信号分别进行距离向和方位向聚焦处理,成像结果如图9(b)所示。由图可知,除去系统固有延迟造成的距离向误差,目标成像位置与场景设计的基本一致。

由于实验室条件限制,模拟实验平台测试仅能取一般斜视成像场景下目标的回波信号,未能获取实测的具有俯冲运动弹载SAR回波数据,但从原理上验证了本文系统设计方法的可行性和正确性。

4、 结论

本文设计了基于FPGA+DSP的弹载SAR成像信号处理系统,通过采用协同处理的硬件结构,一方面解决并行性和速度的问题,另一方面提高了DSP数据处理的能力。实验验证了信号处理系统设计的可行性,既满足系统实时性要求高、数据量大的要求,又解决了复杂算法的实时实现问题。

责任编辑:gt

-

基于DSP的图像处理系统的应用研究2012-12-19 9683

-

基于FPGA+DSP架构的视频处理系统设计2019-06-28 2276

-

一种基于FPGA+DSP的视频处理系统设计2019-07-01 2377

-

怎么利用FPGA+DSP导引头信号处理FPGA?2019-08-19 2192

-

FPGA+DSP导引头信号处理中的FPGA技术该怎么实现?2019-08-30 1523

-

如何利用FPGA+DSP导引头信号处理?2019-11-06 2209

-

可识别方位引信信号处理系统的原理是什么?2020-04-20 1993

-

基于FPGA+DSP的图像处理系统待如何去设计?2021-06-02 1983

-

基于FPGA和DSP的光纤信号实时处理系统2009-06-19 916

-

基于FPGA+DSP实时图像采集处理系统设计2017-01-03 1266

-

基于FPGA+DSP的图像处理系统设计分析2017-10-26 1137

-

基于FPGA+DSP的图像处理系统解析2017-10-31 1307

-

在FPGA+DSP结构的雷达导引头信号处理系统中FPGA的问题解决方案2019-01-08 4054

-

基于FPGA+DSP的高速中频采样信号处理平台2018-10-18 5986

-

基于FPGA+DSP弹载SAR信号处理系统设计2021-12-27 994

全部0条评论

快来发表一下你的评论吧 !