ADA器件TLC320AD75C芯片的应用设计分析

模拟技术

描述

1 Σ-Δ型ADC及DAC

现今使用的绝大部分A/D转换器,例如并行比较型、逐次比较型、积分型等都属于线性脉冲编码调制(LPCM)型 A/D转换器。一个分辨率为n位的这种类型的A/D转换器,为了能区分2n个不同的量化等级,需要相当复杂的比较网络和极高精度的模拟电子器件。当位数n较高时,比较网络的实现是十分困难的,因而限制了转换器分辨率的提高。同时使用A/D转换器构成采集系统时,还必须在转换之前对抽样值进行抽样保持,A/D转换器分辨率越高,这种要求就越重要,因此在一些高精度采集系统中,在A/D转换器的前端除了设置有抗混叠滤波器外,大都还需要设置专门的抽样/保持电路,从而增加了采集系统的复杂度。

所谓总和增量调制编码(Σ-Δ)型A/D转换器则与之不同[2]。LPCM型A/D转换器完全忽略掉信号样值之间的相关性,只是直接根据抽样数据的每个样值的大小进行量化编码;而Σ-Δ型A/D转换器则是根据前一样值与后一样值之差即所谓增量的大小来进行量化编码。Σ-Δ型A/D转换器一般由两部分组成,第一部分为模拟Σ-Δ调制器,第二部分为数字抽取滤波器,如图1(a)所示。Σ-Δ调制器以极高的抽样频率(远高于奈奎斯特抽样频率)对输入模拟信号进行抽样,并对两个抽样值之间的差值进行低位量化(通常为1位),从而得到用低位数码表示的Σ-Δ码,然后将这种Σ-Δ码送给第二部分的数字抽取滤波器进行抽取滤波,从而得到高分辨率的LPCM信号。图1(b)为与之相对应的Σ-Δ型D/A转换器。这种类型的A/D和D/A转换器,就量化而言,由于采用了极低位的量化器,避免了LPCM型A/D转换器中需要制造高位D/A转换器或高精度电阻网络的困难;而且由于它采用Σ-Δ调制器技术和数字抽取滤波器,可以获得极高的分辨率,大大超过了LPCM型A/D转换器;再者由于码位低,抽样与量化编码可以同时完成,几乎不花时间,因此不需要抽样保持电路,这样就使采集系统的构成大为简化。与传统的LPCM型A/D转换器相比,Σ-Δ型A/D转换器实际上是采用以高抽样速率来换取高位量化,即以速度换精度的方案。自90年代以来,Σ-Δ型A/D和D/A转换器获得了很大发展,并在高精度数据采集特别是在数字音响系统、多媒体、地震勘探仪、声纳、电子测量等领域中获得了广泛的应用。

2 TLC320AD75C简介

TLC320AD75C是使用四阶Σ-Δ技术的高性能20位立体声模数和数模转换器(ADA),能同时进行四路20位分辨率的模拟到数字(A/D)和数字到模拟(D/A)信号通道的转换。其它功能还包括数字衰减、数字复原滤波、软静音和片内定时及控制[3]。该芯片具有以下特点:

·单5V(模拟/数字)电源电平及3.3V至5V数字接口电平

·采样速率高达48kHz;

·分辨率为20位;

·ADC的信噪比为100dB;

·ADC的总谐波失真+噪声为0.0017%??

·DAC的信噪比为104dB;

·DAC的总谐波失真+噪声为0.0013%;

·内部电源基准;

·串行接口;

·差分结构;

·DAC具有PWM输出;

·DAC的采样率为32、44.1和48kHz时可进行数字复原滤波;

·DAC具有数字衰减/软静音功能。

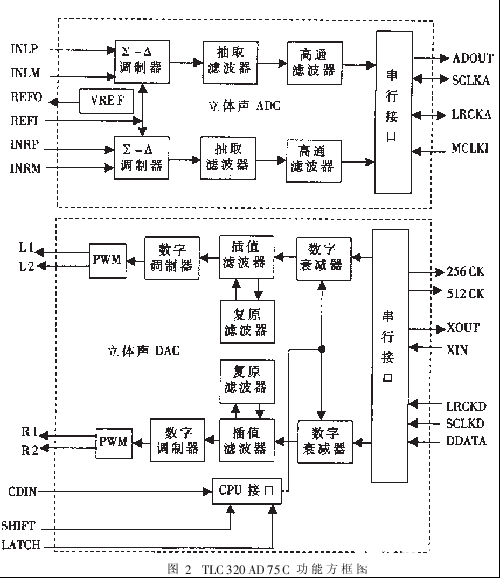

TLC320AD75C的引脚排列及引脚功能请参阅TI公司的产品数据手册,其功能框图如图2所示。

3 TLC320AD75C的接口电路设计

由TLC320AD75C的功能方框图可以看出,TLC320AD75与外电路的接口主要由三部分组成:一是TLC320AD75C与模拟音频数据的接口,包括ADC的差分输入和DAC的PWM输出;二是TLC320AD75C与微控制器的数字音频数据接口;三是DAC的串行控制接口。下面给出具体的电路设计。

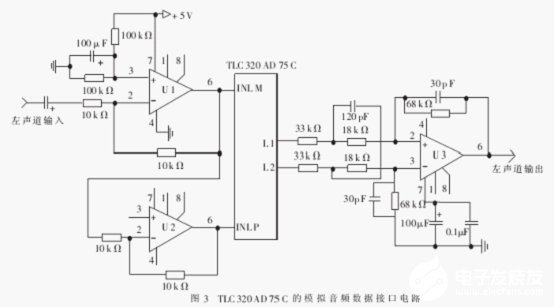

3.1 与模拟音频数据的接口

为了提供高的共模噪声抑制比和增加输入动态范围,TLC320AD75C的ADC的输入采用差分形式;同时还要考虑到TLC320AD75C具有很高的速度和分辨率、开关电容输入结构以及单电源工作等特点,这就要求我们必须仔细设计相关的驱动放大器。驱动放大器必须提供一个低的信号源阻抗和足够的输出电流以驱动ADC输入,并且其高频输出阻抗必须足够低,以避免带来转换误差。图3给出了TLC320AD75C与模拟音频数据的接口电路,由于左、右声道电路完全相同,故只画出了一个声道的接口电路。U1、U2和U3皆选用超低噪声、宽频带、高精度、高速运算放大器OP37。U1和U2将单极性音频输入变换为差分形式的输出,U3则将TLC320AD75C输出的差分信号对L2-L1 (PWM信号)变换成单极性信号。U1中+5V通过两个100KΩ的电阻给运放同相端提供+2.5的静态偏置,100μF的电容则使其交流接地。U2同相端接法同U1,图3中未画

3.2 与数字音频数据的接口

TLC320AD75C的串行端口有两种工作方式:当M/S引脚为高电平时,ADC串行端口配置为主方式,TLC320AD75C从MCLKI产生LRCKA和SCLKA;当M/S接低电平时为从方式,器件从外部接收LRCKA和SCLKA。

本文以ADC的主方式为例说明TLC320AD75C与微控制器间的接口。主方式时LRCKA在内部由MCLKI产生,LRCKA固定为采样频率fs (MCIKI/256)。在此信号为高电平期间,左通道数据串行移至输出端;在低电平期间,右通道数据移至输出端。转换周期由LRCKA的上升沿同步。图 4中的(a)、(b)、(c)三个波形表示了在左、右通道数据所用的32个SCLKA周期中的前20个周期内,从TLC320AD75C中移出的20位、 MSB在前的ADOUT数据。

从图4可以看出,TLC320AD75C与具有同步串口的微控制器如TI公司DSP系列TMS320C2X/3X/5X/2XX/54X的接口相当容易。然而,目前我国DSP的开发和应用还不普遍,大量的科技和工程技术人员对DSP比较生疏。与此相反,单片机如MCS51、8098、MCS196系列却在我国相当普及并得到了广泛的应用。遗憾的是MCS51系列单片机没有同步串口,而且目前的大量数据采集系统的输出要求的是并行数据。考虑到上述情况,为了同MCS51系列接口,就要在满足图4时序的前提下,设计串转并电路和并转串电路。

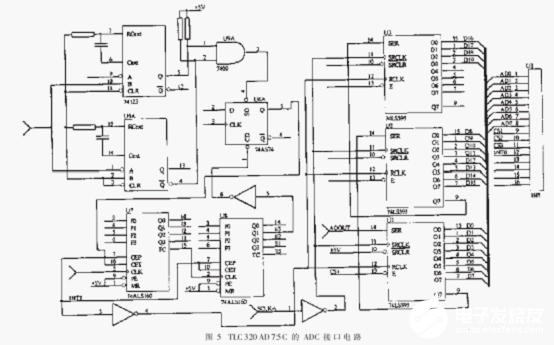

图5是TLC320AD75C 的ADC与MCS51接口电路,DAC接口电路是上述电路的逆过程,只要将8位输出锁存移位寄存器(三态、串入并出)74LS595改成8位输入锁存移位寄存器74LS597(三态、并入串出)即可,此处不再详述。图5与图3的画法一样,鉴于篇幅的限制,省略掉了一些电路细节,读者应用本文中的电路时应补上。下面简单讲述一下图5所示电路的工作过程。根据图4串行接口时序,要求利用LRCKA和SCLKA生成图4(d)所示的脉冲。在该脉冲的高电平期间 20位串行数据送到由三片74LS595级联而成的串入并出接口电路中;在脉冲的下降沿将74LS595中移位寄存器中的数据传输到锁存器;在脉冲的低电平期间发中断到MCS51的INTO,MCS51依次发出三个片选信号,读走该20位数据,从而完成一个声道的采集工作。因此如何产生图4(d)所示的脉冲是本电路的核心问题。在图5所示电路中,74LS123捕捉到的LRCKA上升沿和下降沿通过线与的方式生成图4(e)形式的极窄脉冲。在该脉冲的低电平期间置位74LS74;两片74LS160接成20进制的计数器,在74LS74输出高电平到来时对SCLKA进行计数,当计满20个脉冲时输出一高电平脉冲,该脉冲经一非门倒相去74LS74的复位端。74LS74在上述的置位与复位作用下即产生图4(f)所示的脉冲,同时在该脉冲的低电平期间还要去清除计数器,停止计数器工作,直至该脉冲的下一个高电平到来。要指出的是图4(f)所示脉冲比图4(d)所示的脉冲有一延迟,但只要该延迟时间小于TSCLKA/2,即图4(f)所示脉冲的上升沿比转换开始后SCLKA的第一个上升沿早,同步计数器就可正确计数,不会漏掉1位串行数据。

3.3 DAC的串行控制接口

16 位控制数据输入执行器件的控制功能。TLC320AD75C采用最高有效位在前的格式,因此,对于16位数据字,D16是最高有效位(MSB),D1是最低有效位。图6表示CDIN、SHIFT及LATCH的输入时序。在LATCH为低电平期间,内部装载数据。CDIN是24位数据流,包括16位控制数据 D1~D16和8位器件地址A1~A8。图7示出了TLC320AD75C与MCS51串行口的接口电路。在方式0状态下,MCS51的串行口为同步移位寄存器方式,数据由RXD端出入,同步移位脉冲由TXD端输出。由于MCS51发送、接收的是8位数据,低位在先,而TLC320AD75C采用最高有效位在前的格式,故在MCS51的软件中应将数据高低位颠倒过来。

责任编辑:gt

-

TLC320AD50C在DSP系统中的应用与设计2018-11-30 1714

-

怎样去设计TMS320VC5402与模拟芯片TLC320AD50C的接口?2021-04-23 2060

-

如何去实现TMS320VC5402与TLC320AD50C的接口设计?2021-06-04 1496

-

20 位Σ-Δ立体声ADA电路TLC320AD75C的接口电2010-06-17 1140

-

TLC320AD50,pdf(Sigma-Delta Ana2010-06-23 648

-

音频模拟芯片TLC320AD50C 在数据采集二次通讯中的应2010-07-10 3454

-

TLC320AD50C数据手册2016-08-24 1136

-

TLC320AD58C三角积分立体声模数转换2017-05-19 1020

-

tlc320ad75c的数据手册2017-05-23 1283

-

tlc320ad545的DSP模拟评估板接口电路2017-05-26 1266

-

74ls160应用电路图大全(数字钟\TLC320AD75C\交通灯\LM324)2018-05-08 39920

-

数字信号处理器TMS320VC5402与音频模拟芯片TLC320AD50C的接口设计2019-02-09 1381

全部0条评论

快来发表一下你的评论吧 !