基于Nios软核和FPGA器件实现电缆故障检测仪的设计方案

测量仪表

描述

引言

电缆是通信、测试等系统信号传输的重要载体,随着电缆数量的增多及运行时间的延长,电缆也越来越频繁地发生故障。电缆线路的隐蔽性及测试设备的局限性,使电缆故障的查找非常困难。本文设计了一种以嵌入式微处理器Nios为核心的电缆故障检测仪,应用A/D器件和FPGA组成可变频率的高速数据采集系统,利用低压脉冲反射法原理来实现线缆的断路、短路、断路点、短路点的检测与定位。该仪器可广泛应用于通信维护、工程施工和综合布线,对市话电缆、同轴电缆等各种线缆进行测试和障碍维护。

1 系统总体结构

利用低压脉冲反射法检测电缆故障。主要原理是:向电缆发送一个电压脉冲,当发射脉冲在传输线上遇到故障时,由于故障点阻抗不匹配,产生反向脉冲,通过计算二者的时间差△T,并分析反射脉冲的特性来进行故障的定性与定位。该方法适用于断线、接触不良、低电阻或短路故障的测试。

故障点距离L为:L=V·△T/2。式中,V是脉冲在电缆中的传播速度。根据反向脉冲的极性可判断故障性质:断线或接触不良引起的反向脉冲为正,低电阻或短路故障引起的反向脉冲为负。

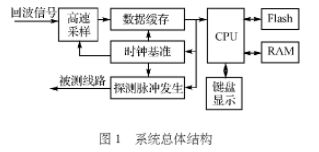

该仪器是一个便携式电缆故障检测设备,可利用现代电子技术(如高速A/D技术、异步FIFO技术、现场可编程逻辑阵列FPGA等)来提高集成度和灵活性。系统总体结构如图1所示。

脉冲发生电路产生探测脉冲,高速的A/D转换器对脉冲及其反射回波信号进行采样,使用异步FIFO作为A/D采样数据的缓存。软核Nios作为系统核心,控制检测任务的启动和结束、脉冲发送接收模式的选择、A/D采样数据的处理计算、故障性质和位置的判断及显示等。其中,软核处理器和逻辑功能都是在现场可编程逻辑器件中编程实现的。

2 功能及性能指标

短路测试:检测电缆芯线之间是否有不必要的连接及其位置。

断路测试:检测电缆中某芯线是否断路及其位置。

显示:显示测试结果,即测量中开路及短路的位置。

测量范围:2~1000 m。

测试精度:可选择2 m和10 m两种精度。

脉冲振幅:负载开路5 V。

脉冲宽度:20 ns,100 ns。

最大采样速率:100 MHz。

波形记录长度:1024点。

3 硬件设计

以Altera公司的Cyelone II系列FPGA器件EP2C20为核心,利用其Nios软核功能设计了微处理器,并完成了相关电路的设计。通过编程FPGA器件定制脉冲发生、高速时钟以及高速数据存储FIFO等模块,以此为基础设计了脉冲发送和接收电路以及高速数据采集和处理电路。

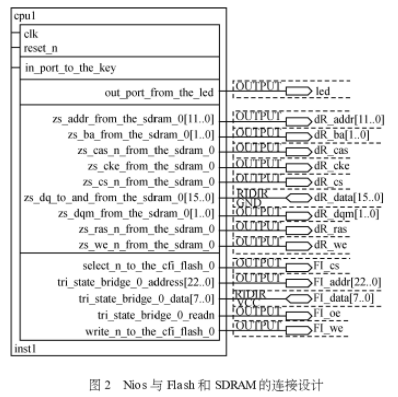

3.1 微处理器系统

简单来说,Nios是一种处理器的IP核,设计者可以将它放到FPGA中。Nios软核处理器是一种基干流水线的精简指令集通用微处理器,时钟信号频率最高可达75 MHz。采用Flash来存储启动代码和应用程序,当系统复位或加电启动时,Flash中的启动代码将被执行。采用SDRAM存储应用程序的可执行代码和数据,为程序提供运行空间。Nios软核与Flash和SDRAM的连接在FPGA中的设计如图2所示。

3.2 探测脉冲的产生

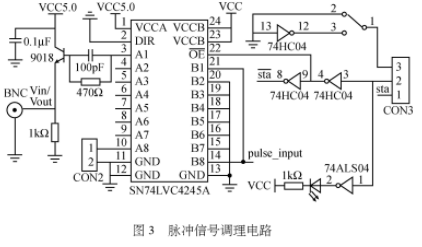

故障检测所用脉冲信号的宽度为20~100 ns,FPGA的工作时钟可以达到200 MHz,在其中生成减法计数器可产生满足脉宽要求的脉冲信号。减法计数器产生脉冲的幅度受限于FPGA的工作电平,对检测来说是不够的,因此从FPGA中出来的方波脉冲还要经过放大,才可以耦合到被检测线缆中去。脉冲信号调理电路如图3所示。SN74LVC4245A用作电平转换。sta和pulse_input均来自FPGA。

本设计采用的是5 V脉冲幅度,脉冲的馈送采取了晶体管射极驱动的方式。这种驱动方式比较简单,适用的器件也比较多。

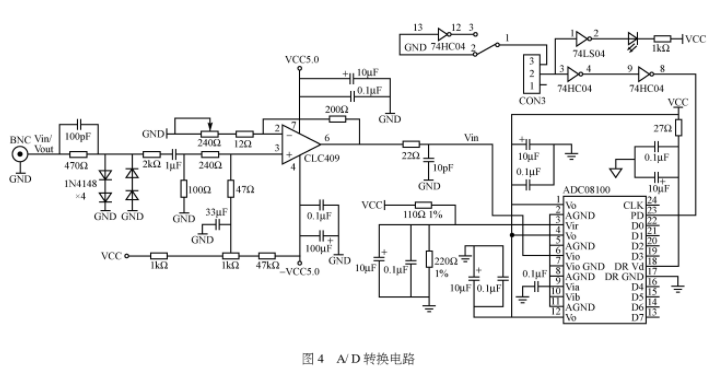

3.3 A/D转换电路

检测脉冲的宽度为20~100 ns,相应的数据采样率在20 MHz和100 MHz之间变化,一般的A/D芯片很难满足采样的要求,而用多片A/D芯片在成本和设计上都比较困难。这里选用美国NS公司的ADC08100,其采样速率为20~100 Msps,此时采样的功耗为1.3 mW/Msps,采样的功耗会随着采样时钟增加而增加,但是采样的特性不会受到影响,因此在采样率多样的系统中一个芯片可以起到多个芯片的作用。根据采样速率的不同,通过一个时钟控制模块产生相应的采样时钟信号,使芯片工作在所要求的速率之下,既可以节约成本,又可以简化设计。ADC08 100和FPGA配合使用,可以方便地改变采样时钟,具有很大的灵活性。

A/D转换电路如图4所示。探测脉冲及回波信号需要转换成适合A/D芯片电压水平的信号后再进行采样。脉冲在输入运算放大器之前进行了钳位处理,采用两组倒置的二极管并联,避免脉冲过高而击穿运算放大器。

3.4 时钟信号的产生

检测脉冲的产生、ADC08100的采样,以及异步FIFO的数据缓存构成了一个高速A/D数据采集系统。这对于各种信号的时间配合要求很高,需要专门的时钟单元来配合,以使电路工作在正确的时序之下。在FPGA中可方便地定制时钟模块来产生A/D采样时钟、异步存储器的读写时钟,以及脉冲发生模块的计数时钟。所有的时钟都是由一个高速的时钟来实现同步的,并且整个系统是在同一个启动信号下同步运行的,从而保证了采样的时序要求。

3.5 电源模块

系统中既有模拟电路又有高速数字电路,使用电源种类复杂,存在+5 V、+3.3 V、+1.2 V、-5 V等多种电源信号。在电路板设计制作中既要减小高频数字信号对模拟信号的电磁干扰,又要避免各种电源之间的干扰,因此需合理规划模块布局及布线走向以提高信号稳定性。

4 软件设计

软件设计主要包括FPGA的开发应用、应用程序设计以及液晶显示器的驱动程序设计等。

4.1 FPGA开发应用

现场可编程逻辑器件FPGA(Field Programming Gate Array)具有高密度、高速度、低功耗、功能强大等特点。在此系统中采用了Altera公司的CycloneII系列器件来实现高速的数据采集、存储功能,是在QuartuslI 7.1软件中使用硬件描述语言VHDL来设计完成的。高密度可编程逻辑器件的设计流程包括:设计准备、设计输入、设计处理和器件编程4个步骤,以及相应的功能仿真(前仿真)、时序仿真(后仿真)和器件测试3个设计验证过程。

本设计中,主要包括Nios微处理器、脉冲发生、高速时钟以及高速数据存储FIFO等模块的设计。

4.2 应用程序设计

应用程序控制检测任务的启动和结束、脉冲发送接收模式的选择、A/D采样数据的处理计算、故障性质和位置的判断以及结果输出等。

结语

本文提出了基于Nios软核的电缆故障检测仪设计方案。对于脉冲反射法检测故障的具体实现,提出了基于现场可编程逻辑器件的高速采样系统的设计思路,并在此基础上对系统进行了全面的设计。仿真和试验结果表明,该系统能够实现对电缆的断路、短路等故障的检测,具有在线监测、易于控制的优点,以及灵活和良好的扩展功能。

责任编辑:gt

-

电缆故障检测仪的设计2014-05-17 3173

-

通信电缆故障测试仪的设计方案2018-09-12 1359

-

电力设备厂家提醒您避免有故障的电缆故障检测仪去检测电缆故障2019-04-02 1873

-

电缆故障测试仪专业检测电缆故障问题2019-07-22 2151

-

嵌入式软核Nios Ⅱ串口直接读写寄存器有哪些编程方法?2019-08-06 1866

-

怎么设计电缆故障检测仪?2019-08-08 2634

-

电缆故障检测仪检测各种电缆的重要工具2019-09-12 1660

-

电机故障检测仪的优点及使用流程介绍2023-03-07 1426

-

基于NiosⅡ软核处理器的SOPC技术来实现数码相框的设计2010-08-23 1636

-

基于微处理器Nios的电缆故障检测仪设计2011-04-23 1474

-

基于Nios软核的电缆故障检测仪设计2011-06-09 1533

-

FPGA和Nios_软核的语音识别系统的研究2016-05-10 774

-

基于嵌入式的电缆故障检测仪设计[图]2018-01-21 952

-

液晶显示屏设计方案:基于Nios嵌入式软核处理器2018-06-04 1501

-

基于Nios软核的SoPC系统硬件设计2019-08-21 1983

全部0条评论

快来发表一下你的评论吧 !