提高功率密度的利弊权衡及所需技术

功率器件

描述

Jefrey Morroni,博士

Kilby 电源、隔离和马达驱动部门经理,电源设计服务部门经理

Pradeep Shenoy,博士,德州仪器(Ti),电源设计服务经理

受限于有限的空间,要实现一个成功的设计,关键之处通常在于减小电源尺寸。人们始终面临着一个挑战,即在更小的空间内实现更大的功率。更广泛地说电源器件的小型化将继续在现有基础上推动新的市场和应用的发展。

本文分析了限制功率密度提高的一些因素,并提供了一些可帮助设计人员克服这些障碍的技术示例。

1 什么是功率密度?

根据应用的不同,可通过几种不同的方式查看功率密度,但目标一致:减小解决方案尺寸以提高功率密度。

2 限制功率密度的因素有哪些?

限制设计人员提高功率密度能力的主要因素是转换器的功率损耗(包括传导、电荷相关、反向恢复以及导通和关断损耗)以及系统的热性能。

3 如何突破功率密度障碍?

设计人员必须多措并举,并行采取多种方式来克服每个限制因素:减少开关损耗;提高封装热性能;采用创新的拓扑和电路;并利用更多的无源集成。

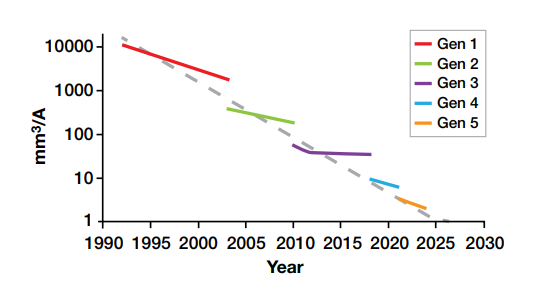

数十年来,功率密度变得越来越高,这一行业发展趋势已成为一个不争的事实,预计这一趋势仍将继续。图 1 显示了 6A 至 10A 电源模块的转换器尺寸随时间推移而不断减小的情况技术的进步可以让尺寸减少或让功率输出能力得到大幅提升每条实线代表了新一代技术,并展示了提高功率密度可带来的相关好处。

图 1. 随着新一代技术的发展,电源模块的尺寸会随着时间的推移而减小。功率密度的提高通常与效率或成本等其他领域的发展息息相关。一般而言,功率转换效率的根本性提高可减小解决方案的尺寸。减小尺寸会带来一系列连锁反应,物理材料更少、组件更少、成本结构更好、解决方案集成更多以及总体拥有成本更低,从而实现成本的节省。

什么是功率密度?

功率密度是衡量在给定空间内可以处理多少功率的指标 可量化为每单位体积处理的功率量,单位为瓦/ 立方米 或瓦/立方英寸。这些值是基于转换器的额定功率以及电源解决方案(所有组件包含在内)的“箱体体积”(长度 x 宽度 x 高度)计算得出的,如图 2 所示。可以将单位缩放到适当的功率等级或大小。例如,千瓦/升是电动汽车车载充电器的常见品质因数 (FoM),因为这些功率转换器可提供千瓦级的功率(介于 3kW 到 22kW 之间)。

图 2. 尺寸为 65mm x 28mm x 25mm 的 65W 有源钳位反激式转换器。电流密度是一种与功率密度有关的指标,它非常有用,可以量化为单位体积的电流,单位为安培/立方英寸或安培/立方毫米。转换器的额定电流(通常是输入电流或输出电流)可用于计算电流密度。电流密度通常是更适合应用于负载点稳压器等应用的 FoM。这些设计的大小与输出电流成比例,并且输出电压电平通常较低,约为 1V。通过假定一个不切实际的高输出电压,可对功率密度值进行人为地夸大。因此,电流密度是一个更为有效的指标,因为它将输出电压排除在考虑因素之外。

有时体积密度并不重要。功率电子器件可能不受高度限制,因为设计的其他部分会相当高。相反,电路板面积可能是限制因素。在这些情况下,提高功率密度可能需要找到堆叠或 3D 集成组件的方法,以减少功率解决方案的空间占用。然后,您可以将用于比较解决方案优劣的指标修改为瓦/平方毫米或安培/平方英寸,从而突出关键的设计目标(如图 3 所示)。

图 3. 一个面积为 13.1mm x 10mm 的 10A 负载点转换器,电流密度为 76mA/mm2 。根据应用的不同,可通过几种不同的方式查看功率密度,但目标一致:减小解决方案尺寸以提高功率密度。现在的问题是如何获得功率密度带来的那些好处。

限制功率密度的因素有哪些?

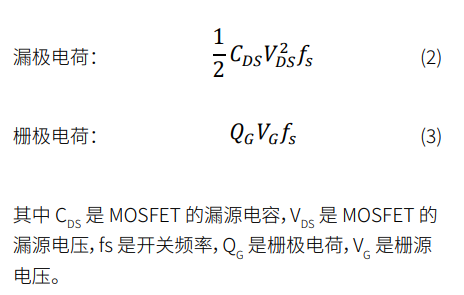

多年来,工程师和研究人员一直致力于寻找提高功率密度的方法。这是一项艰巨的任务。大多数公司将研究重点集中在减小用于能量转换的无源组件的尺寸上。电感器、电容器、变压器和散热器通常占据了电源解决方案尺寸的最大部分,如图 4 所示。半导体开关和控制电路体积更小,集成度更高。

图 4. 诸如电感器和电容器之类的无源组件会占用相当大的空间。

如何减小无源组件的尺寸?一种简单的解决方案是增加开关频率。开关转换器中的无源组件会在每个开关周期内存储和释放能量。开关频率越高,其每个周期内存储的能量越少。例如,根据公式 1,即降压转换器中电感器的设计公式:

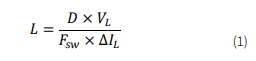

其中 L 是电感,D 是占空比,ΔIL 是电感器电流纹波,FSW 是开关频率,VL 是电感器两端的电压。所需的电感 (L) 与开关频率 (FSW) 成反比。随着开关频率的增加,电感减小。电感越小,所需的电感器也就越小,就越节省空间。图 5 说明了在 400kHz 与 2MHz 频率下开关 3A、36V 转换器所需电感器的尺寸差异。

图 5. 400kHz (a) 和 2MHz (b) 频率下,3A、36V 转换器开关的尺寸比较。

更高的开关频率还有其他尺寸优势。增大开关频率可以增加控制环路带宽,从而可以用较小的输出电容满足瞬态性能要求。您可以设计具有较小电感和电容的差模电磁干扰 (EMI) 滤波器,并选用不会使磁芯材料饱和的较小变压器。

那么,为什么人们不能仅仅依靠增加开关频率来提高功率密度呢?事实证明,说起来容易做起来难。即使将电源转换器中使用的所有无源元件缩小到微不足道的尺寸,也仍然有机会减小电源解决方案的尺寸。电源开关、栅极驱动器、模式设置电阻器、反馈网络组件、EMI 滤波器、电流感应组件、接口电路、散热器和许多其他组件占用了宝贵的空间。总体电源设计的所有这些方面都是可以通过创新来提高功率密度的领域。让我们回顾一下限制设计人员提高功率密度能力的主要因素。

限制功率密度的因素:开关损耗

尽管增加开关频率可以提高功率密度,但在目前,电源转换器的开关频率通常不高于兆赫兹范围,这是因为:开关频率的增加会带来不良副作用,也会导致开关损耗增加和相关的温升。这主要是由一些主要的开关损耗引起的。

要了解这些开关损耗,我们有必要首先介绍一些行业术语。在半导体器件中,与该器件相关的电荷量通常与导通状态电阻有关。较低的电阻会导致较高的栅极电荷和寄生电容。电阻和电荷的这种权衡通常通过 RQ FoM 进行量化,RQ FoM 定义为器件的导通电阻乘以总电荷,其中总电荷是指必须提供给端子以在工作电压下开关器件所需的电荷。此外,器件为达到目标电阻所占用的面积通常称为电阻与面积的乘积 (Rsp)。您可以通过减少金属氧化物半导体场效应晶体管 (MOSFET) 的导通状态电阻 (RDS(on)) 来降低传导损耗。然而,减少 RDS(on) 也将导致与器件开关相关的损耗增加,并增加裸片总面积和成本。

根据实现和应用的不同,不同的开关损耗对总体功率损耗的影响可能会有所不同。有关每种类型损耗的更多详细信息,请参见应用报告“同步降压转换器的功率损耗计算和共源电感注意事项”。出于阐述本文观点的目的,我们来看一个降压转换器示例,并重点介绍与每个损耗分量相关的关键限制因素。

关键限制因素 1:与充电有关的损耗

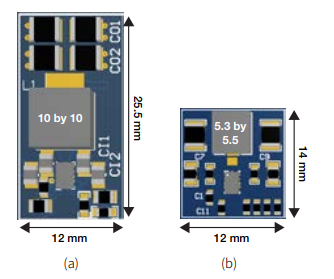

在任何硬开关直流/直流转换器中,系统中寄生电容的充电和放电都需要一定量的能量。对于给定的开关技术和额定电压,通过公式 2 和 3 可估算得出这些损耗为:

从公式 2 和 3 可以看出,可以主要通过降低开关频率(不可取),改善 MOSFET 的电荷相关 FoM(QG 和 CDS)或在传导损耗与开关损耗之间进行权衡来减少这些损耗。

关键限制因素 2:反向恢复损耗

在降压转换器中,当高侧 MOSFET 导通,同时低侧 MOSFET 的体二极管导通电流时,会发生反向恢复,从而迫使低侧二极管电流迅速过渡至高侧 MOSFET。在该过渡过程中,需要电流来消除会造成直接开关损耗的低侧二极管少数电荷。请参见公式 4:

关键限制因素 3:导通和关断损耗

寄生环路电感会导致许多与开关相关的损耗,这会大大降低效率。让我们再次以通过高侧 MOSFET 传导电感电流的降压转换器为例。关闭高侧开关会中断通过寄生电感的电流。瞬态电流 (di/dt) 以及寄生环路电感会引起电压尖峰。di/dt 值越高,开关损耗越低,从而导致器件电压应力越高。在某些关断速度下,降压转换器高侧开关会发生击穿。因此,您必须审慎地控制开关速度,最大限度地提高效率,同时将直流/直流转换器放置在安全工作区域内。

此外,降低高侧 MOSFET 的漏极电荷也会导致其上出现额外的电压尖峰,这是因为作为电感/电容网络的一部分,用于吸收寄生环路电感中所存储能量的电容较小。这带来了另一个挑战,因此最好是将漏极电荷保持在尽可能低的水平,以减少前面提到的与电荷相关的损耗。要减轻与这些寄生效应相关的总损耗,通常需要减少环路电感本身,同时采用其他栅极驱动器技术。

限制功率密度的因素:热性能

在上一部分中,我们重点介绍了在直流/直流转换器中产生与开关相关的损耗的关键机制。影响总体功率密度的另一个关键因素是系统的热性能。封装的散热效果越好,通常可以承受的功率损耗就越多,而不会出现不合理的温升情况。这些因素通常会包含在数据表参数中,例如结至环境热阻 (RΘJA),以及对应用条件的仔细估算;请参见应用报告“半导体和 IC 封装热指标”,了解更多信息。

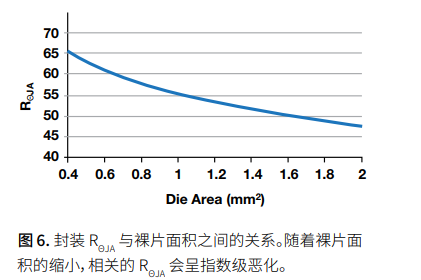

对封装和印刷电路板 (PCB) 进行热优化的总体目标是降低电源转换器损耗的同时减少温升。随着电源设计朝着小型化和降低成本的趋势发展,直流/直流转换器解决方案的整体尺寸缩小了。这使得系统级热设计变得越来越困难,因为更小的硅片和封装尺寸通常会导致更差的热性能,如图 6 所示。

图 6 清楚地表明,随着封装尺寸、裸片尺寸和总体功率密度的提高,预期的热性能会迅速下降,除非您优先考虑创新封装热性能(将热量散发出去)并减少功率损耗(产生更少热量)。

如何突破限制功率密度的障碍

针对上述所言的任一关键因素进行重点研究,都可以提高器件的总体功率密度。但是,要真正实现以前难以企及的功率密度,您必须多措并举,并行采取多种方式来克服限制功率密度的每个因素:降低开关损耗;提高封装热性能;采用创新的拓扑和电路;最后但同样重要的一种方式是集成。

开关损耗创新

为了获得出色的器件性能和 FoM,对半导体技术进行投资显然是必要的。这可能包括用于改进现有技术的创新,或者开发本质上性能更好的新材料,例如用于更高电压开关应用的氮化镓 (GaN) 技术。

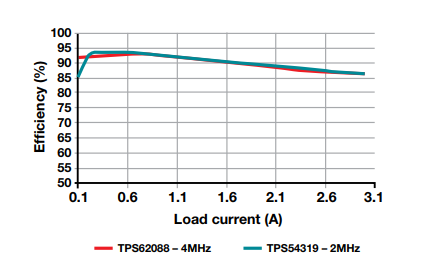

图 7 比较了使用德州仪器 (TI) 的不同电源处理技术的 3.3V 至 1.8V 降压转换器。TPS54319 采用 TI 以前的电源处理节点,而 TPS62088 采用 TI 的最新电源处理节点,其具有更低的 RQ FoM。如效率曲线所示,与以 2MHz 频率进行开关的 TPS54319 相比,TPS62088 能够以 4MHz 频率进行开关,同时保持几乎相同的效率。这可以使外部电感器的尺寸减半。此外,由于 TI 的新型电源处理节点还可以显著降低 Rsp,因此整体封装尺寸从 4mm2 下降到了 0.96mm2 。尽管从功率密度的角度来看,这种尺寸减小非常具有吸引力,但它也带来了与温升有关的挑战,我们将在下一部分中讨论这一问题

图 7. 3.3V 至 1.8V 降压转换器的直流/直流效率比较。TPS54319 的开关频率为 2MHz,并采用 TI 以前的电源处理节点,而 TPS62088 的开关频率为 4MHz,采用 TI 的最新电源处理节点,并具有改进的开关 FoM。

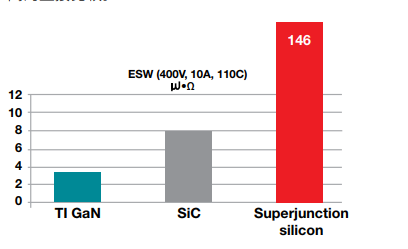

GaN 集独特的零反向恢复、低输出电荷和高压摆率于一体,实现了新的图腾柱拓扑,例如无桥功率因数校正。这些拓扑具有硅 MOSFET 无法实现的更高效率和功率密度。图 8 显示了 TI 的 GaN 技术在 600V 电压下与业界一流的碳化硅 (SiC) 和超结硅器件之间的直接比较。

图 8. GaN、SiC 和超结硅开关技术在 400V 总线电压下工作的开关能量比较。TI GaN 技术可大幅降低损耗,从而实现更高的频率。

封装散热创新

将热量从集成电路 (IC) 封装中散发出来的能力将直接影响功率密度。正如我们前面提到的,随着封装尺寸的不断缩小,这个问题变得越来越重要。此外,在典型的电源转换器中,半导体器件通常是解决方案中最热的部分,在 Rsp 迅速缩小的情况下尤其如此。

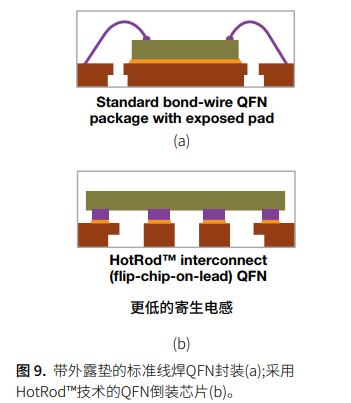

TI 已投资开发并引入了 HotRod™ 封装,它用倒装芯片式封装取代了典型的接合线四方扁平无引线封装 (QFN)。图 9 显示了 HotRod QFN 如何在保持类 QFN 封装的同时消除接合线的情况。这样可以大大降低倒装芯片式封装中常见的寄生环路电感,同时还保留了 QFN 封装热性能的部分优势。

HotRod 封装面临的一个挑战是,制造大型裸片附接焊盘 (DAP) 变得更加困难,该焊盘通常对改善封装的散热非常有帮助。为了克服这一挑战,TI 最近增强了 HotRod QFN 的性能,使其在保持现有优势的同时,还能实现带有大型 DAP 的封装。

图 10 显示了包含这些技术增强功能的 TI 产品。您可以看到,该封装有助于在封装的中心实现一个大型 DAP。与上一代产品相比,该 DAP 具有约 15% 的温升优势。

图 10. 带有用于改善热性能的大型 DAP 的增强型 HotRod QFN 封装 (a);传统 HotRod 封装的热性能 (b);带有 DAP 产品的增强型 HotRod QFN 封装的热性能 (c)。

同样,在使用晶圆芯片级封装 (WCSP) 时,大部分热量直接从凸块传导出去,一直传导到 PCB。WCSP 封装中的凸块面积越大,热性能越好。TI 最近开发并发布了 PowerCSP™ 封装,该封装旨在通过用大型焊锡条代替 WCSP 中的一些典型圆形凸块来改善封装的散热和电气性能。图 11 说明了该技术在 TPS62088 中的示例实现。图 11a 显示了标准 WCSP 封装,而图 11b 显示了采用 PowerCSP 封装的同一器件。正如您所看到的,在系统没有任何其他变化的情况下,温升降低了 5% 左右。

先进的电路设计创新

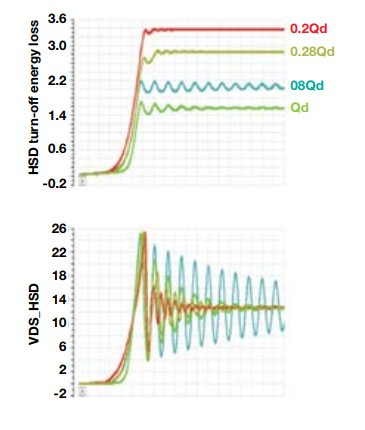

较低 Rsp 和较低 RQ FoM 的不良后果是在漏极电荷减少的情况下,导通转换损耗会产生影响。通过图 12,您可以看到,对于固定的电压过冲量,随着漏极电荷的减少,这种降压转换器的关断损耗会显著增加。遇到这种需要权衡取舍的情况时,尽管 RQ FoM

MOSFET 的性能在持续改进,但仍需要使用新的先进栅极驱动器知识产权 (IP) 来尽快开关 MOSFET,同时将其保持在电气安全的工作范围内。

图 12. 不同 MOSFET 技术的关断能量损耗比较。随着漏极电荷的减少,关断能量将会增加,以维持固定的漏源电压应力。

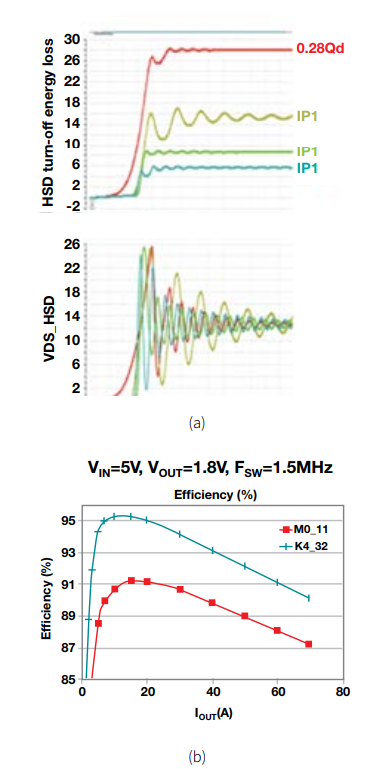

在这方面,TI 最近开发了一系列栅极驱动器技术,尽管 RQ FoM MOSFET 较低,但仍可实现非常快的开关速度,从而可获得更好的充电和转换损耗,同时仍将 MOSFET 保持在其电气安全的工作范围内。正如您在比较图 13a 和图 13b 时所看到的,在保持峰值电压应力固定不变的情况下,可以将关断能量损耗减少 79%。在某些设计中,如图 13b 所示,这种损耗降低可以在峰值效率点产生高达 4% 的效率提升。

图 13. 实现低漏极电荷和低关断能量的栅极驱动器 IP 的比较 (a);栅极驱动器 IP 对系统效率的影响,大约增加了 4% (b)。

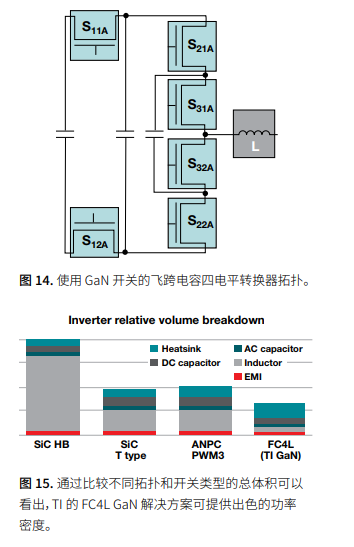

除了先进的栅极驱动器技术以外,还有大量机会可以通过拓扑创新来提高功率密度。图 14 展示了飞跨电容四电平 (FC4L) 转换器拓扑,该拓扑实现了许多关键的功率密度优势,包括通过降低器件额定电压、减小磁滤波器尺寸和改善热分布来提高器件 FoM。这些优势可转化为改进的功率密度,如图 15 所示。与使用 SiC 的其他拓扑相比,TI 解决方案通过使用这种特殊的拓扑,结合 GaN 的优势和先进的封装技术,大大减小了体积。

集成创新

实现最佳功率密度的最后一个方法是集成。具有高性价比的集成减少了寄生效应,减少了物料清单,提高了效率并节省了空间。集成可适用于电源管理的多个方面。它可能需要在 IC 中添加更多的电路,在封装中添加更多的组件,或者通过其他物理或机械方式在电源解决方案中封装更多的组件。在这一领域中,一些技术领先的例子包括与 GaN FET 集成的驱动器、用于降低关键环路电感的电容器集成以及无源组件的 3D 堆叠。

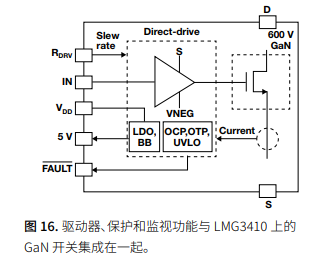

添加带有开关功率 FET 的栅极驱动器有很多好处。开关栅极驱动环路电感减小,可使开关速度更高、运行更稳定、组件更少。GaN FET 尤其受益于这种集成。LMG3410 等器件还包括过流保护、过热保护和监视等附加功能(请参见图 16)。这种集成极大地简化了电源管理解决方案,并使设计人员能够实现 GaN 必须提供的所有功能。

集成的另一个途径是在 IC 封装中加入无源组件。集成高频去耦电容器是 LMQ61460-Q1 中使用的一种技术,如图 17 所示。集成电容器可以通过减少临界环路寄生电感和降低 EMI 来提高效率。该电源解决方案还可以在不牺牲系统稳健性或超过热限制的情况下增加开关时间,从而提高开关频率,并通过使用更少的 EMI 滤波组件减小解决方案尺寸。

UCC12050 利用磁性组件集成来提供隔离式偏置电源,而无需外部变压器。该方法减少了尺寸和设计复杂性并降低了 EMI。

通过集成实现的最后一个例子是组件的 3D 堆叠,这通常发生在带有集成无源组件的电源模块中。图 18 以 TPS82671 为例。该器件将电源 IC 嵌入层压基板中,并在顶部放置一个电感器以及输入输出电容器。这个极小的解决方案不需要其他组件。简单的集成概念可以取得惊人的效果,节省 PCB 面积并简化电源解决方案。

结束语

显而易见,整个行业的发展趋势功率密度越来越高。实现更紧凑的电源解决方案存在一些主要限制。要克服功率损耗和热性能挑战,就需要在开关性能、IC 封装、电路设计和集成方面进行创新。每一种方式本身都有显著改善功率密度的机会,但是每种技术都又彼此融合。因此,通过组合各个类别的技术,可以显著提高功率密度。

不妨设想一下我们最终能够实现的这种产品,它们具有出色的开关器件 FoM 和业界领先的封装热性能,使用了多级拓扑并通过无源集成实现了最低环路电感。技术进步相互作用,并最终实现功率密度突破。

利用 TI 的先进工艺、封装和电路设计技术,现在可以在更小的空间内实现更大的功率,并以更低的系统成本增强系统功能。

-

TPS25981-提高功率密度2024-08-26 435

-

使用集成 GaN 解决方案提高功率密度2023-12-01 1395

-

功率密度权衡——开关频率与热性能2022-12-26 2486

-

高功率密度的解决方案2022-11-07 1275

-

功率密度基础技术简介2022-10-31 873

-

如何提高器件和系统的功率密度2022-05-31 3542

-

电源设计控制的利弊权衡2021-09-29 651

-

如何用PQFN封装技术提高能效和功率密度?2021-04-25 2468

-

什么是功率密度?如何实现高功率密度?2021-03-11 13625

-

权衡功率密度与效率的方法2020-10-27 2325

-

功率密度的基础技术简介2020-10-20 1781

-

德州仪器:功率密度基础技术简介2020-08-20 2214

-

氮化镓GaN技术怎么实现更高的功率密度2019-08-06 4265

全部0条评论

快来发表一下你的评论吧 !