SPI总线协议的工作机制解析

接口/总线/驱动

描述

一、概述

SPI,串行外围设备接口,是Motorola公司推出的一种同步串行接口技术.SPI总线在物理上是通过接在外围设备微控制器(PICmicro)上面的微处理控制单元(MCU)上叫作同步串行端口(SynchronousSerialPort)的模块(Module)来实现的,它允许MCU以全双工的同步串行方式,与各种外围设备进行高速数据通信。

SPI主要应用在EEPROM,Flash,实时时钟(RTC),数模转换器(ADC),数字信号处理器(DSP)以及数字信号解码器之间。它在芯片中只占用四根管脚(Pin)用来控制以及数据传输,节约了芯片的pin数目,同时为PCB在布局上节省了空间。正是出于这种简单易用的特性,现在越来越多的芯片上都集成了SPI技术。

二、特点

1、采用主-从模式(Master-Slave)的控制方式

SPI规定了两个SPI设备之间通信必须由主设备(Master)来控制次设备(Slave)。一个Master设备可以通过提供Clock以及对Slave设备进行片选(SlaveSelect)来控制多个Slave设备,SPI协议还规定Slave设备的Clock由Master设备通过SCK管脚提供给Slave设备,Slave设备本身不能产生或控制Clock,没有Clock则Slave设备不能正常工作。

2、采用同步方式(Synchronous)传输数据

Master设备会根据将要交换的数据来产生相应的时钟脉冲(ClockPulse),时钟脉冲组成了时钟信号(ClockSignal),时钟信号通过时钟极性(CPOL)和时钟相位(CPHA)控制着两个SPI设备间何时数据交换以及何时对接收到的数据进行采样,来保证数据在两个设备之间是同步传输的。

3、数据交换(DataExchanges)

SPI设备间的数据传输之所以又被称为数据交换,是因为SPI协议规定一个SPI设备不能在数据通信过程中仅仅只充当一个“发送者(Transmitter)”或者“接收者(Receiver)”。在每个Clock周期内,SPI设备都会发送并接收一个bit大小的数据,相当于该设备有一个bit大小的数据被交换了。

一个Slave设备要想能够接收到Master发过来的控制信号,必须在此之前能够被Master设备进行访问(Access)。所以,Master设备必须首先通过SS/CSpin对Slave设备进行片选,把想要访问的Slave设备选上。

在数据传输的过程中,每次接收到的数据必须在下一次数据传输之前被采样。如果之前接收到的数据没有被读取,那么这些已经接收完成的数据将有可能会被丢弃,导致SPI物理模块最终失效。因此,在程序中一般都会在SPI传输完数据后,去读取SPI设备里的数据,即使这些数据(DummyData)在我们的程序里是无用的。

三、工作机制

1、概述

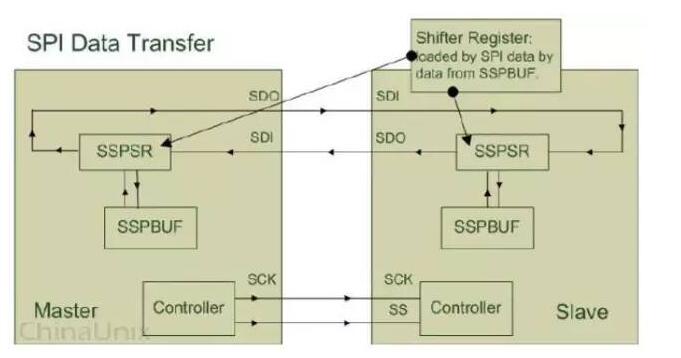

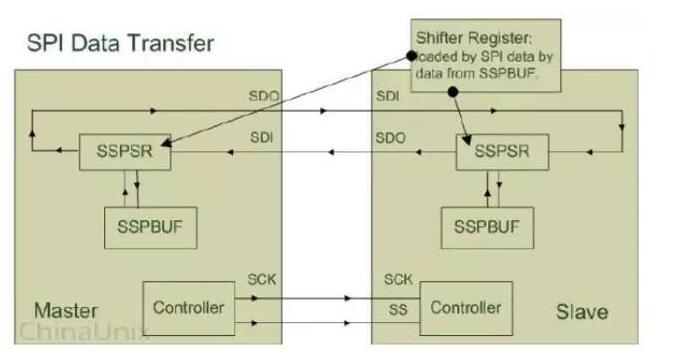

上图只是对SPI设备间通信的一个简单的描述,下面就来解释一下图中所示的几个组件(Module):

SSPBUF,SynchronousSerialPortBuffer,泛指SPI设备里面的内部缓冲区,一般在物理上是以FIFO的形式,保存传输过程中的临时数据;

SSPSR,SynchronousSerialPortRegister,泛指SPI设备里面的移位寄存器(ShiftRegitser),它的作用是根据设置好的数据位宽(bit-width)把数据移入或者移出SSPBUF;

Controller,泛指SPI设备里面的控制寄存器,可以通过配置它们来设置SPI总线的传输模式。

通常情况下,我们只需要对上图所描述的四个管脚(pin)进行编程即可控制整个SPI设备之间的数据通信:

SCK,SerialClock,主要的作用是Master设备往Slave设备传输时钟信号,控制数据交换的时机以及速率;

SS/CS,SlaveSelect/ChipSelect,用于Master设备片选Slave设备,使被选中的Slave设备能够被Master设备所访问;

SDO/MOSI,SerialDataOutput/MasterOutSlaveIn,在Master上面也被称为Tx-Channel,作为数据的出口,主要用于SPI设备发送数据;

SDI/MISO,SerialDataInput/MasterInSlaveOut,在Master上面也被称为Rx-Channel,作为数据的入口,主要用于SPI设备接收数据;

SPI设备在进行通信的过程中,Master设备和Slave设备之间会产生一个数据链路回环(DataLoop),就像上图所画的那样,通过SDO和SDI管脚,SSPSR控制数据移入移出SSPBUF,Controller确定SPI总线的通信模式,SCK传输时钟信号。

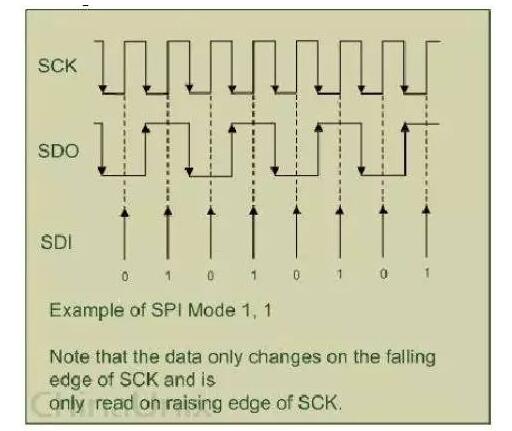

2、Timing.

上图通过Master设备与Slave设备之间交换1Byte数据来说明SPI协议的工作机制。

首先,在这里解释一下两个概念:

CPOL:时钟极性,表示SPI在空闲时,时钟信号是高电平还是低电平。若CPOL被设为1,那么该设备在空闲时SCK管脚下的时钟信号为高电平。当CPOL被设为0时则正好相反。

CPHA:时钟相位,表示SPI设备是在SCK管脚上的时钟信号变为上升沿时触发数据采样,还是在时钟信号变为下降沿时触发数据采样。若CPHA被设置为1,则SPI设备在时钟信号变为下降沿时触发数据采样,在上升沿时发送数据。当CPHA被设为0时也正好相反。

上图里的“Mode1,1”说明了本例所使用的SPI数据传输模式被设置成CPOL=1,CPHA=1.这样,在一个Clock周期内,每个单独的SPI设备都能以全双工(Full-Duplex)的方式,同时发送和接收1bit数据,即相当于交换了1bit大小的数据。如果SPI总线的Channel-Width被设置成Byte,表示SPI总线上每次数据传输的最小单位为Byte,那么挂载在该SPI总线的设备每次数据传输的过程至少需要8个Clock周期(忽略设备的物理延迟)。因此,SPI总线的频率越快,Clock周期越短,则SPI设备间数据交换的速率就越快。

3、SSPSR.

SSPSR是SPI设备内部的移位寄存器(ShiftRegister)。它的主要作用是根据SPI时钟信号状态,往SSPBUF里移入或者移出数据,每次移动的数据大小由Bus-Width以及Channel-Width所决定。

Bus-Width的作用是指定地址总线到Master设备之间数据传输的单位。

例如,我们想要往Master设备里面的SSPBUF写入16Byte大小的数据:首先,给Master设备的配置寄存器设置Bus-Width为Byte;然后往Master设备的Tx-Data移位寄存器在地址总线的入口写入数据,每次写入1Byte大小的数据(使用writeb函数);写完1Byte数据之后,Master设备里面的Tx-Data移位寄存器会自动把从地址总线传来的1Byte数据移入SSPBUF里;上述动作一共需要重复执行16次。

Channel-Width的作用是指定Master设备与Slave设备之间数据传输的单位。与Bus-Width相似,Master设备内部的移位寄存器会依据Channel-Width自动地把数据从Master-SSPBUF里通过Master-SDO管脚搬运到Slave设备里的Slave-SDI引脚,Slave-SSPSR再把每次接收的数据移入Slave-SSPBUF里。

通常情况下,Bus-Width总是会大于或等于Channel-Width,这样能保证不会出现因Master与Slave之间数据交换的频率比地址总线与Master之间的数据交换频率要快,导致SSPBUF里面存放的数据为无效数据这样的情况。

4、SSPBUF.

我们知道,在每个时钟周期内,Master与Slave之间交换的数据其实都是SPI

内部移位寄存器从SSPBUF里面拷贝的。我们可以通过往SSPBUF对应的寄存器(Tx-Data/Rx-Dataregister)里读写数据,间接地操控SPI设备内部的SSPBUF。

例如,在发送数据之前,我们应该先往Master的Tx-Data寄存器写入将要发

送出去的数据,这些数据会被Master-SSPSR移位寄存器根据Bus-Width自动移入Master-SSPBUF里,然后这些数据又会被Master-SSPSR根据Channel-Width从Master-SSPBUF中移出,通过Master-SDO管脚传给Slave-SDI管脚,Slave-SSPSR则把从Slave-SDI接收到的数据移入Slave-SSPBUF里。与此同时,Slave-SSPBUF里面的数据根据每次接收数据的大小(Channel-Width),通过Slave-SDO发往Master-SDI,Master-SSPSR再把从Master-SDI接收的数据移入Master-SSPBUF。在单次数据传输完成之后,用户程序可以通过从Master设备的Rx-Data寄存器读取Master设备数据交换得到的数据。

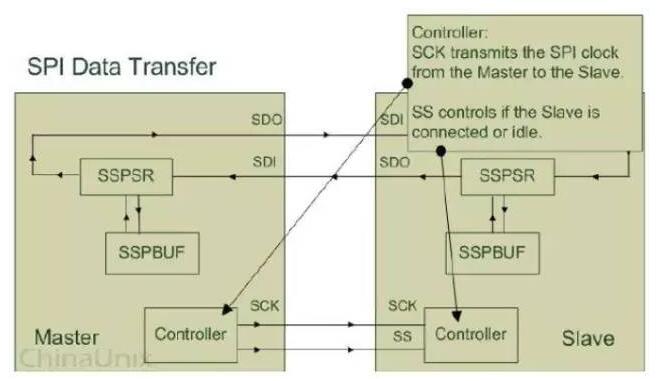

5、Controller.

Master设备里面的Controller主要通过时钟信号(ClockSignal)以及片选信号(SlaveSelectSignal)来控制Slave设备。Slave设备会一直等待,直到接收到Master设备发过来的片选信号,然后根据时钟信号来工作。

Master设备的片选操作必须由程序所实现。例如:由程序把SS/CS管脚的时钟信号拉低电平,完成SPI设备数据通信的前期工作;当程序想让SPI设备结束数据通信时,再把SS/CS管脚上的时钟信号拉高电平。

-

SPI总线学习笔记2023-09-20 2095

-

浅谈SPI总线通信接口及其协议2023-03-22 3106

-

关于SPI通讯的精讲 SPI协议的特点和工作机制2022-05-08 11198

-

SPI总线协议及SPI时序图详解2022-02-11 1218

-

SPI协议2021-12-22 1254

-

SPI总线协议介绍及硬件设计资料分享2021-11-10 1024

-

基于SPI协议的SD卡读写机制与实现方法2021-03-25 1204

-

SPI总线及I2C总线工作原理2015-12-08 1450

-

SPI总线简介与参考实例2015-11-19 920

-

关于I2C和SPI总线协议2015-08-07 3633

-

SPI总线协议2013-04-10 2448

-

SPI总线协议介绍2012-08-18 19135

全部0条评论

快来发表一下你的评论吧 !