UART寄存器介绍与中断操作详解(应用部分)

电子说

描述

我们在让 Altera FPGA 上的嵌入式系统和外部设备进行通信方式的时候,通常会用到拥有Avalon 接口的通用异步收发传输器——UART IP 核。UART 核实现了 RS-232 通讯协议,并使得大家可以设置串口通信相关的波特率、奇偶校验位、停止位和数据位,以及可选的 RTS/CTS 流控制信号等参数。

实验任务

本节实验是:在Qsys系统中通过使用官方UART IP核和PC进行环回,将收到的字符发送给PC。

硬件设计

创建 Quartus II 工程

首先要创建 Quartus II 工程,工程名为“UART_ip”。

创建 Qsys 系统

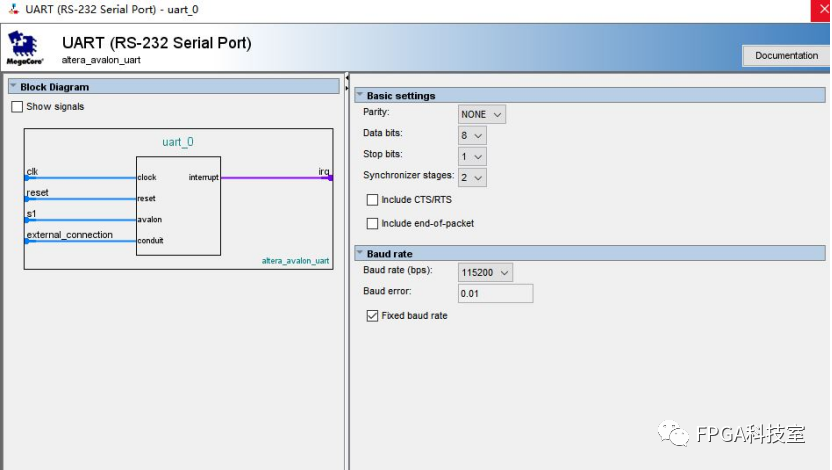

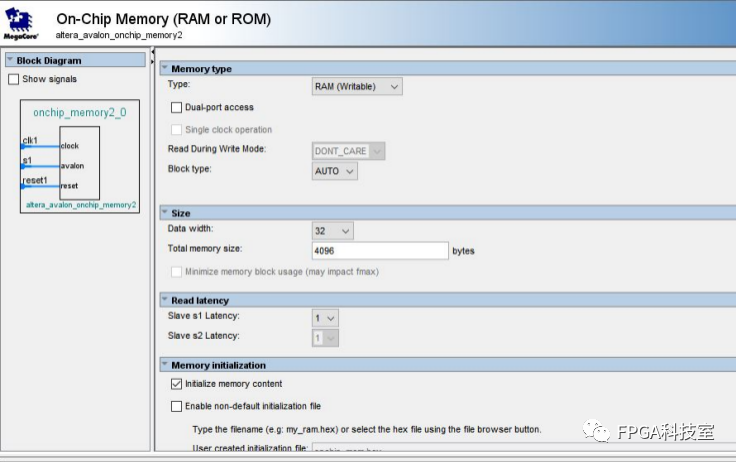

实验中要用到的 IP 核有:clk(时钟)、niosII(处理器)、onchip_ram(片内存储)、jtag_uart、sysid_qsys、UART。其中只有 UART IP 核讲解一下,其他的 IP 核都是按照以前的配置方法进行设置,从 Library 中选择 UART IP 核(RS-232 Serial Port)并打开,出现以下界面:

这里我们使用默认设置,直接点击【Finish】即可。

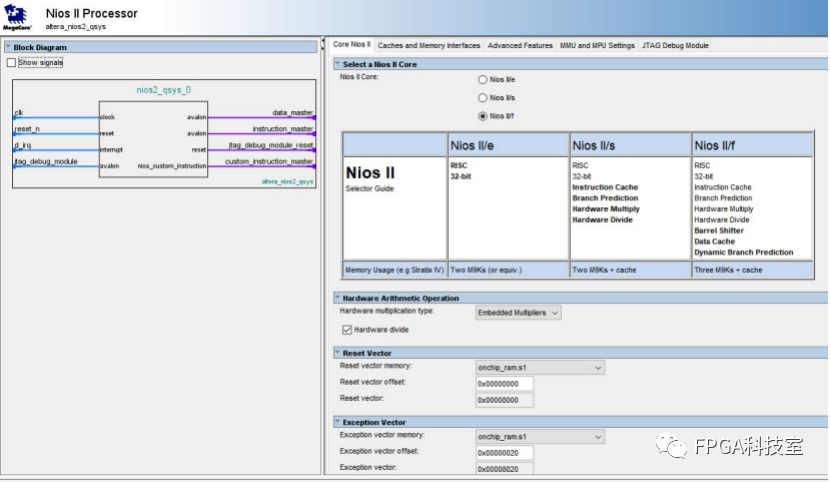

然后,我们打开 niosII IP 核配置界面,因为这里只用了 onchip_ram IP 核存储代码和指令,所以需要对相关的设置进行修改,在 Reset Vector 处将 Reset vector memory 处的选项选为 onchip_ram,同时在 Exception Vector 处也将 Exception vector memory 处的选项选为 onchip_ram。需要注意的是,在系统中加入onchip_ram IP 核之后,niosII IP 核的 Reset Vector 和 Exception Vector 选项中才会出现 onchip_ram 选项。

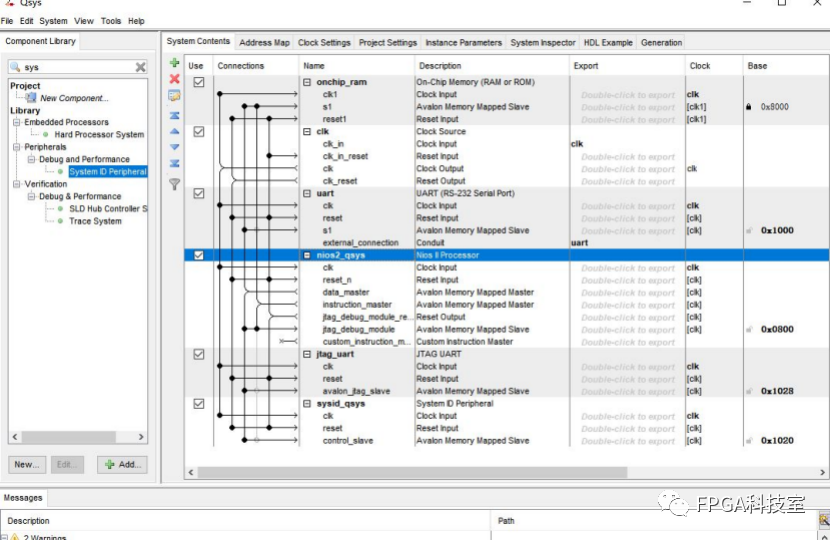

添加完 IP 核后就可以开始连线,大家若是不熟悉怎么连线,可以照着下面完成的 Qsys 系统界面图连。需要注意的是,要将 UART IP 核的端口引出来,引出端口的方法是双击 IP 核的 Export 一栏,然后修改名称,按下 Enter 键即可。

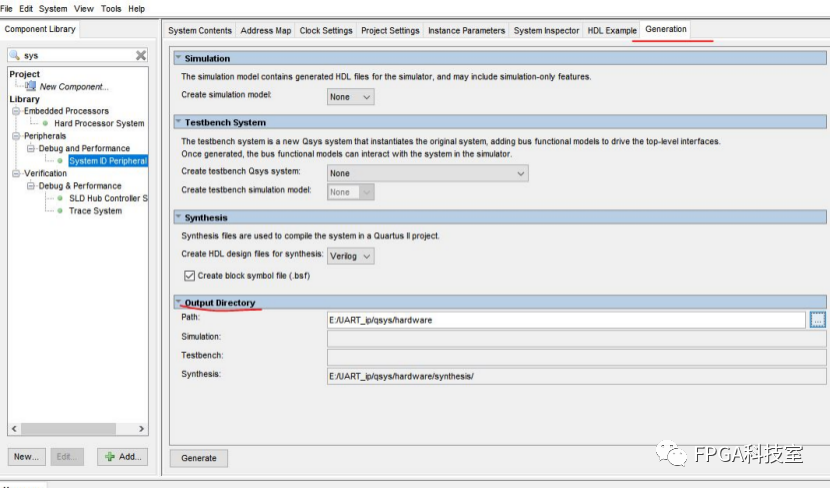

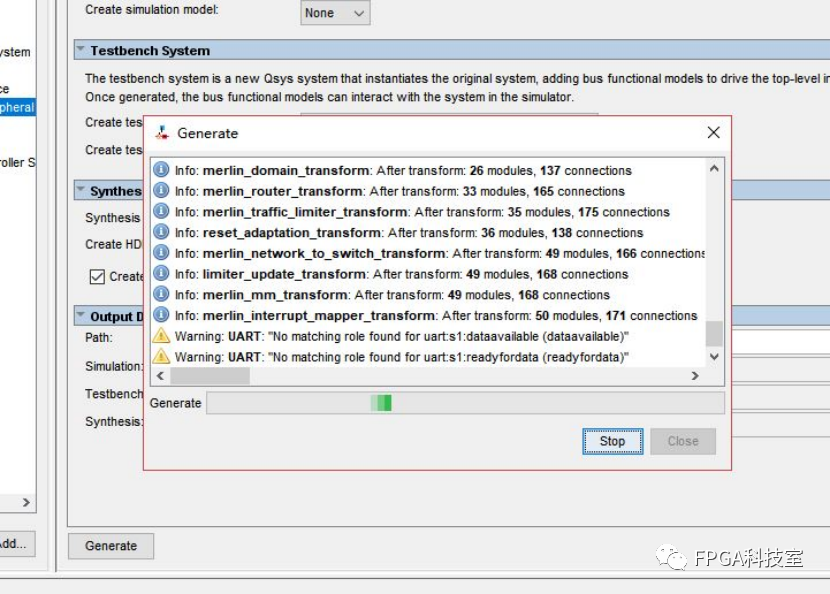

然后,点击 System→Assign Base Addresses 让系统自动分配地址,这里最好把 onchip_ram的地址锁住,这是因为这个 IP 核里存储着指令,最好不要让其地址发生变动。锁住地址的方法是先点击 IP 核,然后点击右键→Lock Base Address。我们还可以将各个 IP 核的名称修改一下。最后就是生成系统了,操作可以按照“Hello,World”推送里的进行。

集成 Qsys 系统

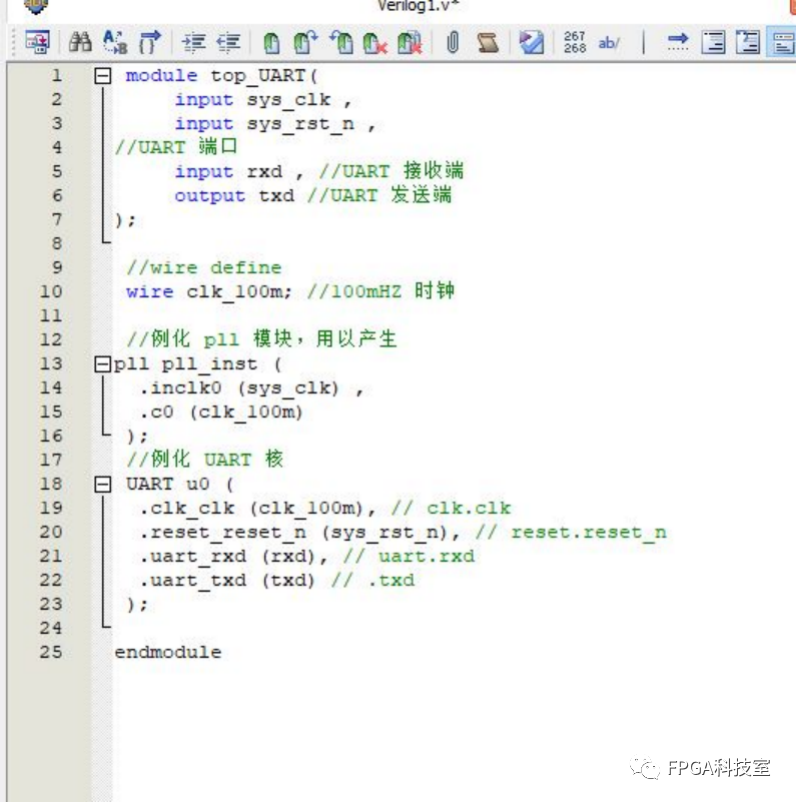

下面两个图为集成Qsys关键步骤,详细集成步骤请参考“Hello,World”推送里的操作。

Quartus II 工程中的顶层代码如下。

编译和下载

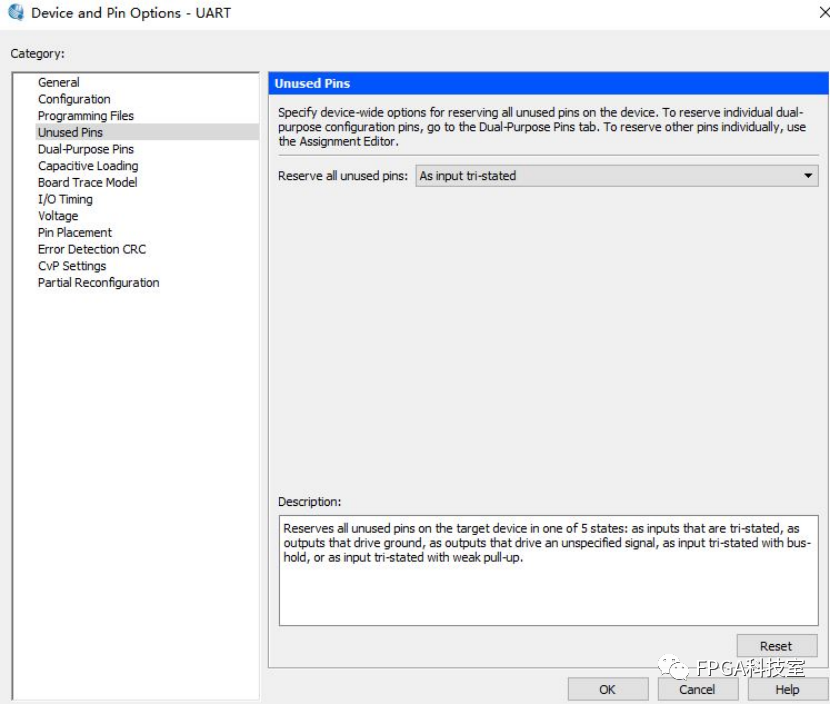

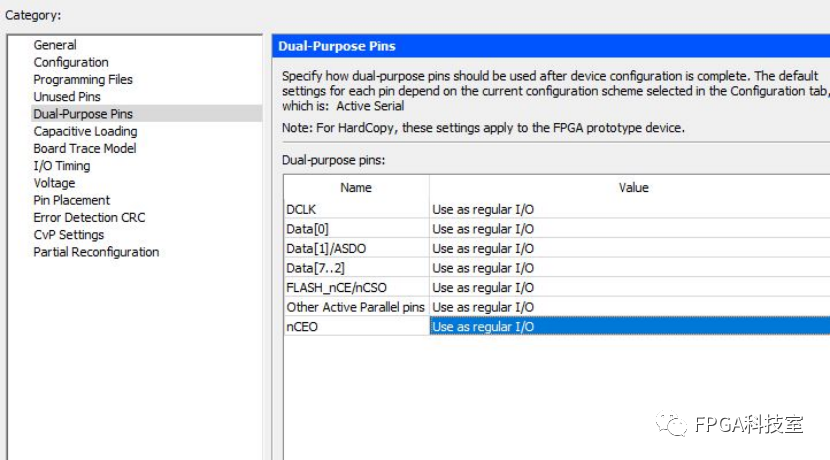

这时,我们便能够进行编译查错了,我们可以通过 Quartus II 软件菜单栏中的【Processing】→【Start Compilation】来进行编译,也可以通过快捷栏中的快捷键进行编译。接下来我们就需要进行配置 IO,分配管脚。首先,点击 Quartus II 软件菜单栏中的【Assignment】→【Device】,然后我们在 Device 界面中找到【Device and Pin Options…】进入页面配置 IO。将未使用引脚设置为高阻输入(As input tri-state),这样上电后FPGA 的所有不使用引脚都将进入高阻抗状态。

接下来,将一些 IO 设置成普通 IO,通过双击红框位置,将一个个 Value 的值修改过来。

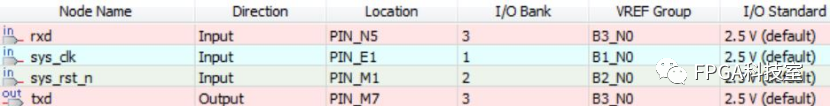

通过 Quartus II 软件菜单栏中的【Assignments】→【Pin Planner】选项分配引脚

最后我们再进行一次全编译,成功编译硬件系统后,将产生用于配置 FPGA 的 UART_ip.sof 文件。下面我们就来说明一下将.sof 文件下载到 FPGA 目标器件的步骤。

将下载器一端连接电脑,另一端与开发板上对应端口连接,最后连接电源线并打开电源开关。接下来我们下载程序。工程打开后通过点击工具栏中的“Programmer”图标打开下载界面,通过“Add File”按钮选择 output_files 目录下的“UART_ip.sof”文件。

开发板电源打开后, 在程序下载界面点击“Hardware Setup”,在弹出的对话框中选择当前 的硬件连接为“USB-Blaster[USB-0]”。然后点击“Start”将工程编译完成后得到的 sof 文件下载到开发板中。

至此,硬件部分设计完成,下面开始基于 Nios II SBT for Eclipse 的软件部分的设计。

软件设计

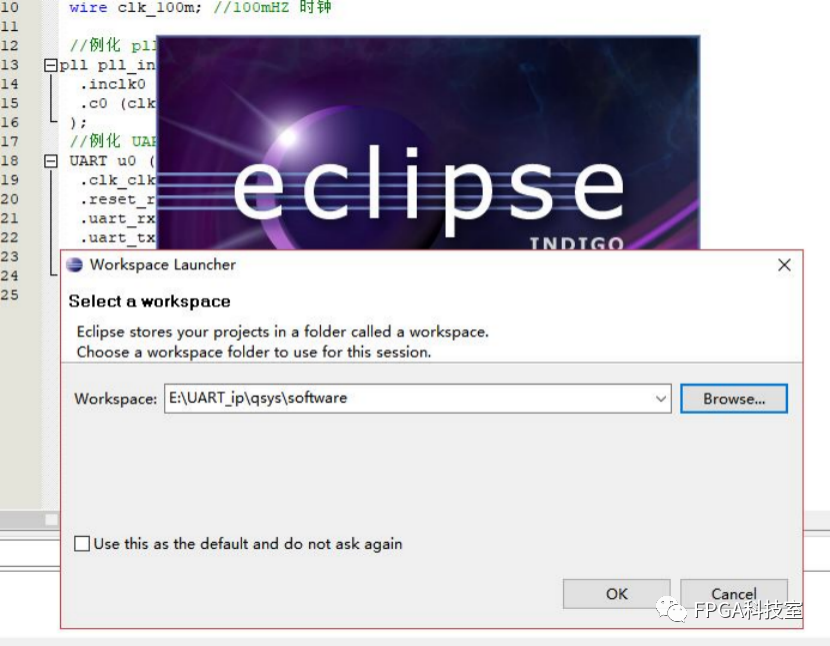

我们通过 Quartus II 软件菜单栏中的【Toos】→【Nios II SBT for Eclipse】,来启动 NiosII SBT for Eclipse 软件。打开 Nios II SBT for Eclipse 软件后,会弹出 Workspace Launcher 页面。我们这里将工作空间设置为qsys 路径下的software 文件夹,如图所示。

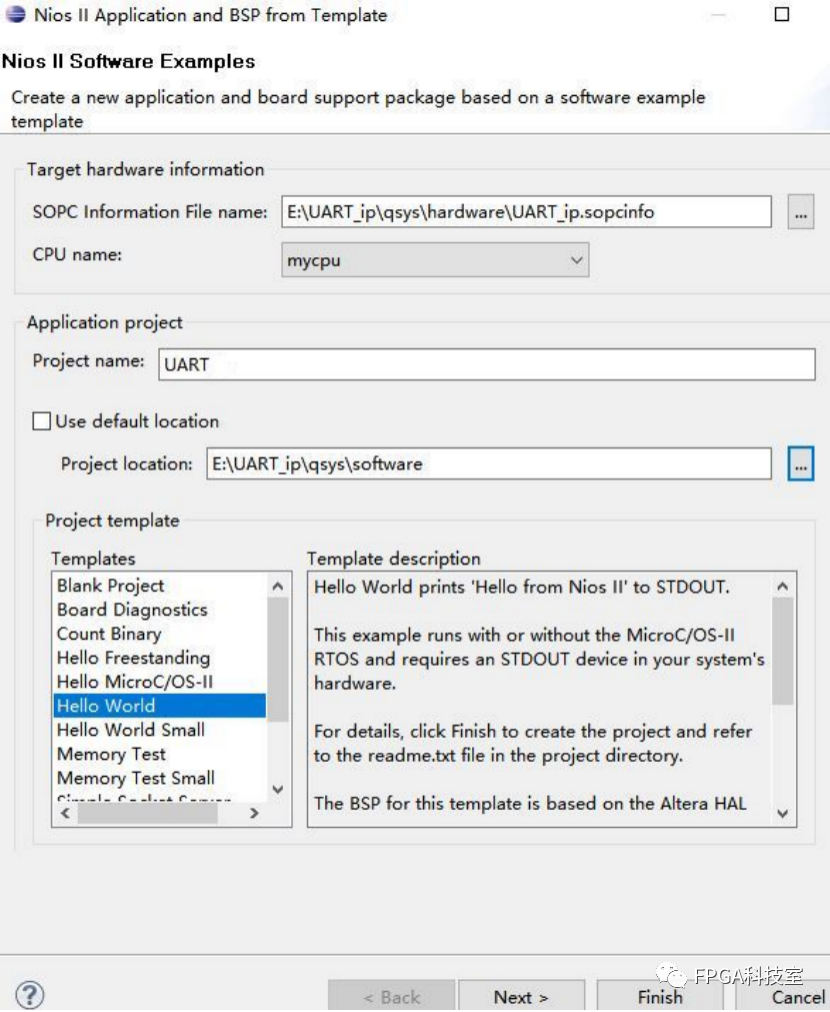

设置好工作空间后,我们点击【OK】进入 Nios II SBT for Eclipse 软件主界面中,在该页面我们通过单击菜单栏中的【File】→【New】→【Nios II Application and BSP from Template】,来新建工程。

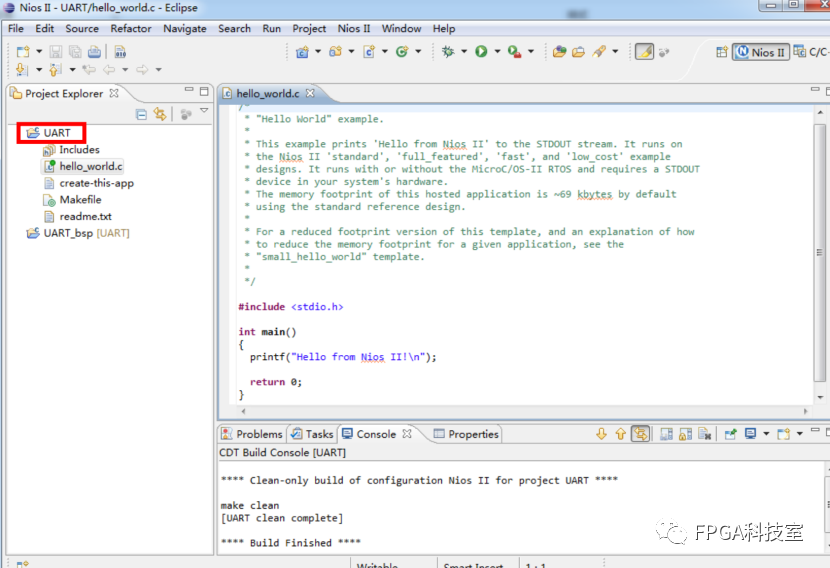

单击【…】按钮来选择 qsyshardware 下的 UART_ip.sopcinfo 文件,即指向当前硬件设计系统。Nios II SBT for Eclipse 软件会自动识别 Qsys 系统中 CPU 的名称,所以 CPU name一项会自动生成。接下来,要给 Nios II SBT for Eclipse 软件中的工程命名,这里的名称没有特殊要求,我们这里名为 UART。然后将工程存放的位置修改为 qsyssoftwareUART。注意不要漏掉了“UART”,不然生成系统的时候会报错。最后我们来看下 Project template 窗口,该窗口中陈列的都是已经设计好的软件工程。我们可以从中选择一个,作为自己的工程的模板来使用。当然也可以选择 Bland Project(空白工程),就需要自己写所有的代码。这里我们选择的是 Hello World 模板工程,然后我们在它的基础上进行修改,这样比空白工程更加方便。设置完工程后,直接点击【Finish】完成工程创建。然后,在 Nios II SBT for Eclipse 软件的

左侧 Project Explorer 窗口中有两个工程:UART 和 UART_bsp。其中 UART 是 C/C++应用工程,而UART_bsp 是描述 Qsys 系统硬件细节的系统库。打开 UART 工程里的 hello_world.c 文件。

我们在这里要验证之前创建的 Qsys 系统是否能正常工作,验证方法和“Hello,World”是一样的。

这时大家点击【Run As】→【Nios II Hardware】,然后点击【Target Connection】标签,然后在 Target Connection 窗口中点击【Refresh Connections】按钮后。这时软件便会自动识别我们开发板上的 Qsys 系统,并显示 Qsys 系统的相关信息。我们接着点击【Run】,软件会把 irq.elf 文件下载至开发板中运行起来。更加详细的图和文字描述,可以在“Hello,World”下载验证部分查看。

这时,若之前创建的 Qsys 系统无误,代码下载完成后在 Nios II console 窗口会显示“Hello from Nios II!”字符,如下图所示。

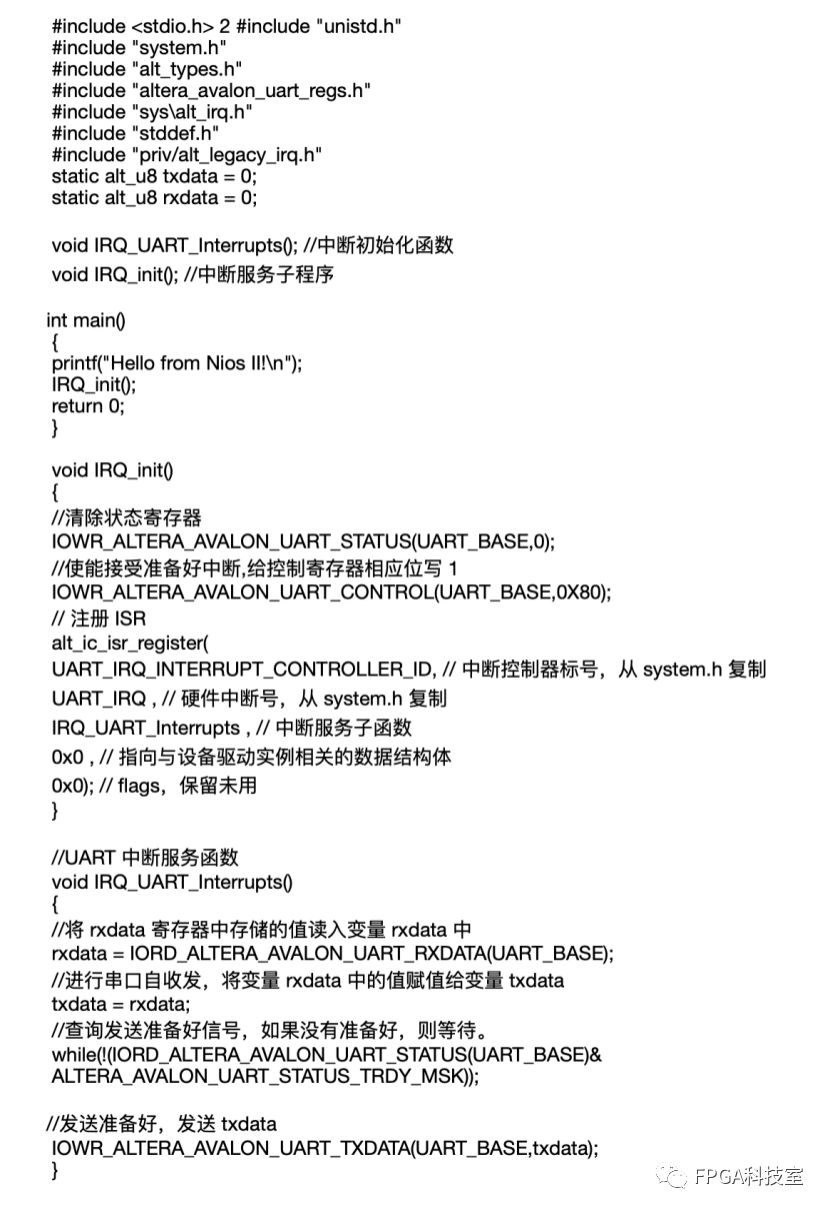

验证完 Qsys 系统是否能正常运行之后,我们就可以开始软件部分的设计了。这时只需要在当前的代码窗口修改代码就可以了。

下载验证

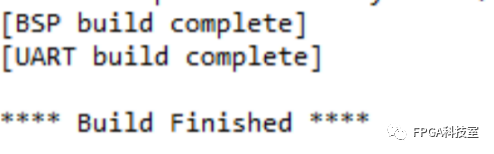

现在可以编译 UART 工程了。右键 UART 工程,点击 build project。稍等片刻,Console 窗口显示的内容如下图所示,这表示工程编译成功。

右键 UART 工程,点击【Run As】→【Nios II Hardware】,代码就被下载到开发板上了。接下来需要连接串口线并利用串口助手进行验证。

-

DSP2812寄存器详解2016-01-08 1171

-

寄存器传输语言详解2017-08-16 7206

-

51寄存器的所有寄存器名称,(包括寄存器每一位的作用及用法)资源详解2017-10-16 1534

-

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途2017-12-22 21281

-

寄存器操作方法_对寄存器操作的通用方法总结2018-05-22 24806

-

Zynq uart软件中断hook的操作过程2019-05-02 2202

-

如何选择51单片机的中断寄存器组2019-04-17 1352

-

ATMEL SAMC21的UART驱动寄存器操作和程序免费下载2019-06-20 1823

-

使用寄存器的逻辑操作指令是什么?2020-06-18 4469

-

UART寄存器介绍与中断操作详解2020-08-25 17740

-

51单片机与中断相关的寄存器2021-11-12 1393

-

STM32的寄存器操作2022-01-13 1432

-

RAL寄存器模型操作指南2023-07-12 2238

-

Linux驱动操作寄存器2023-09-26 2560

-

U54内核中断控制和状态寄存器2023-10-08 2251

全部0条评论

快来发表一下你的评论吧 !