DC-DC 转换器无法对负载阶跃的开关型稳压器造成输出瞬降

电子说

描述

为CPU 或其它高密度逻辑器件供电从来都不是一件容易的事情,尽管技术的进步最终会降低计算任务所需的电力。相对于不断提高的运算能力需求,技术的高速发展所带来的改进仍然入不敷出。这个矛盾在笔记本电脑中尤为突出,尽管每瓦特电能所能提供的运算能力已大大提高,但电池寿命的扩展却日益接近极限。

无论是由于需求和技术的同步提高导致了性能的停滞或者反之,便携系统中越来越高的电源电流需求正迫使设计者去熟悉更新的电源技术。本文将探索一些这方面的新技术。

CPU、DSP 和其它大规模逻辑器件芯片尺寸的缩小使其电源电压不断下降,目前在+1.5V 至+2.5V 范围,不久会降低到 1V。高效率地产生这样低电压的电源会有一些困难,尤其是在输出电流达到 10A 或更高时。

和大多数电子设计一样,高效的电源设计必须综合考虑多种相互冲突的因素,包括成本和元件数量、效率和散热、电路尺寸及瞬态特性(如负载阶跃响应)等。电池寿命是便携系统(由电池供电)的主要考虑,而热耗散问题(也就是效率问题)无论对于电池供电或者是交流供电系统来讲都至关重要。

严格的负载调整 + 高速响应 = 难以赢得的挑战

今日的 CPU 内核要求非常严格的负载调整。至少到目前为止,一些主要的 CPU 制造商都有如此要求。随着电源电压的降低,电源电流和时钟频率却更高了,使得对于电源的要求急剧提高—特别是瞬态响应。日益严格的性能要求使设计的难度和成本越来越高,促使人们重新考虑电源的设计。更高的负载电流和更大负载瞬变带来的后果之一,便是在处理器周围多出一片电容“丛林”,增加了系统的尺寸和成本。

最快的开关型稳压器也无法对负载阶跃造成的输出瞬降做出响应,面对这个现实,以及前面所提到的一些问题,迫使我们必须改变思路(以及规格)。以当今 CPU 的速率,只有完全依靠输出电容来应付其高速阶跃。另一方面,更为严格的负载调整需要更高的环路增益,而更高增益的环路需要更大的输出电容来保持稳定。由此看来,某种程度上放松对于负载调整的要求,对于元件数量的降低及其它诸多方面都极为有利。

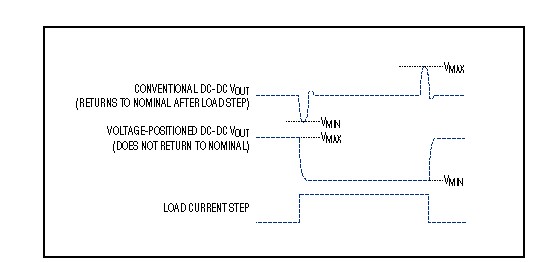

典型的 DC-DC 转换器对于负载阶跃的响应可划分为 5 个基本部分(图 1):

电压瞬降,幅度等于阶跃负载电流乘以输出电容等效串联电阻(ESR)。

瞬降之后、DC-DC 转换器响应之前会有一段电压缓降,电容上的电压随着电容向负载供电而跌落。

电压恢复期,电感接通并供出负载电流,同时使输出电容得到补充。

负载撤离引起“ESR 上跳”(与电压瞬降效应相反)。

电压过冲,前一个开关周期储存于电感的能量(负载撤离后)被转储到输出电容。

其中 2、3 和 5 可以通过仔细的设计和正确选择 DC-DC 控制器而控制到最小。但其中的瞬态电压阶跃部分(1 和 4)则无法消除,除非降低输出电容的 ESR。快速调节器能够在发生跳变之后更快地将输出拉回,但也无法消除跳变本身。即便是最快速的 DC-DC 转换器(例如 MAX1711,可以在不足 100ns 的时间内响应)对于运行于 600MHz 的 CPU 来讲也太慢了。

图 1. 该波形表示一次瞬态负载阶跃响应的主要组成部分

电压定位

显然,强迫 DC-DC 达到不切实际的瞬态响应是没有希望的。一个 600MHz 的 CPU 在 MAX1711 的 100ns 响应时间内已经飞驰了 60 个时钟周期。既然电源电压总是要跌落 ESRCOUT × ILOAD STEP 并保持若干个时钟周期,那么,是否将它拉回正常值能有多大关系呢? 从 CPU 的角度来看,无关紧要。从电源的角度来看,很有关系。

从电源的角度考虑,更愿意使负载电压不再恢复“正常”。这样,当负载移去时,将能够适应将近两倍的瞬态电压上升。同样,当负载接入时也可允许两倍的瞬态跌落。图 2 可以说明两种电压转换器负载阶跃响应的不同。

图 2. 由于电压定位调节器在每次负载阶跃后并不试图恢复输出电压至“正常”,它们能够允许更大的瞬态偏移。而且这个额外的裕量还可以降低功率消耗和输出电容数量。

基于这种思想,产生了一种新型的 CPU 电源规范(见图 1 中的灰色方框)。标称电压为 1.6V,允许被负载拉低 7.5% (根据目前 CPU 标准)。当负载从满载变为零时,允许有 7.5%的上升(短暂脉冲式)。稳态输出电压包括噪声和纹波在内不应超过 1.65V。这些数据十分有助于降低电容数量,同时在延长电池寿命及降低热量耗散方面获得可观的收益。

为了充分利用 CPU 电源规格放宽所带来的好处,可以为给定电源规定一个电压 / 负载曲线。根据这个特征曲线,实现一种受控形式的负载抑制—有时称为电压定位—输出电压按照某种负载电流的函数而定位。这种电压定位允许一定的输出跌落,而不耗费能量和成本试图将其拉回。随着负载电流的升高,输出按照预先规定的轨迹下落。相比于强行拉回的方式,这种方法对于瞬态问题能够给出更为圆满的解决,前者仅提供有限的好处,却要求更大的电容和更高速的 DC-DC 转换器。

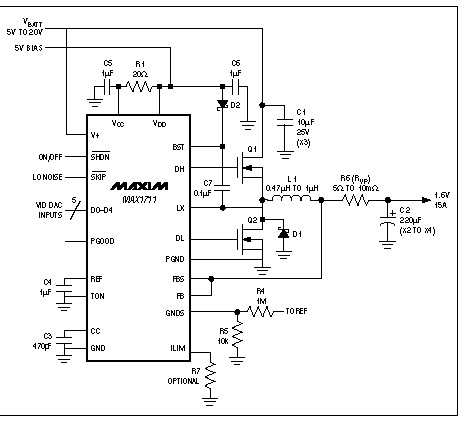

只需不超过三只电阻,就可为许多 DC-DC 转换器增加电压定位功能(图 3)。R4 和 R5 使输出电压产生一个很小的正向偏移,使其从(本例中的)标称 1.6V 升高至 1.62V。R6 (RVP)串联于输出,匹配于最差情况下的输出电容 ESR。RVP 的作用是产生一个确定的、与负载相关的电压跌落。

图 3. 这个高效的 15A 稳压电源很容易转变为电压定位设计,只需增加三只电阻:R4、R5 和 R6 (RVP)。

C1 = 陶瓷电容,C2 = Panasonic SP 系列:EEFUEOE221R.

*对于连续 15A 负载电流的情况,由于 IR7809 的散热限制,请使用(2) IRF7811 或(2) IRF7805。

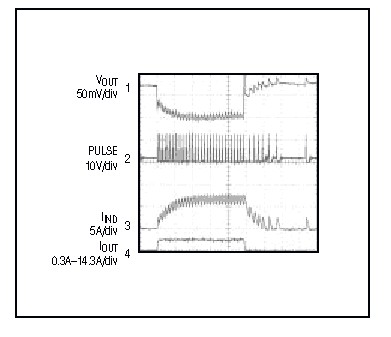

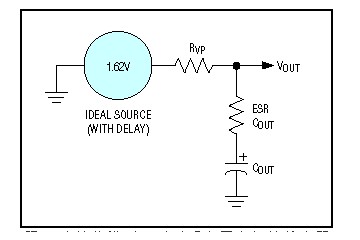

如果 RVP 与滤波电容的 ESR 相匹配,输出电压在经历了负载阶跃造成的瞬降(ESR × ILOAD)之后将停留在原位,直到负载再次发生变化。降低负载会引起(ΔI × ESR)的电平上移。经过一个短暂的、因上一次电感放电造成的瞬态脉冲之后,在控制器的 100ns 响应之前(在 7.5%门限以内),直流电平就能够恢复到预定的空载电压(本例中为 1.62V)减去 ILOAD × RZ。

图 4. 图 3 所示电路的阶跃响应可以说明电压定位输出带来的好处

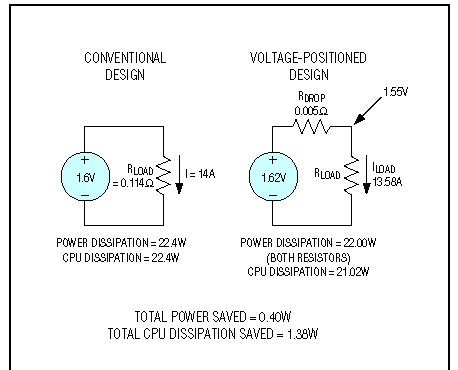

输出端增加 5mΩ的串联电阻会降低转换效率。然而,它也降低了重载时的 CPU 工作电压,有利于降低功耗并延长电池寿命。和传统的(无电压定位的)调节器相比,电压定位设计可以降低 CPU 功耗 1.38W,降低系统整体功耗 0.4W (图 5、图 6)。

图 5. 该简化模型可以说明电压定位的基本原理。当 RVP 等于 ESR (COUT 的等效串联电阻)时,对于负载阶跃可得到理想的“方波”电压响应(图 2)。

图 6. 尽管输出电阻的增加降低了转换效率,电压定位设计同时也降低了消耗在电源和 CPU 内部的功率。

等效效率

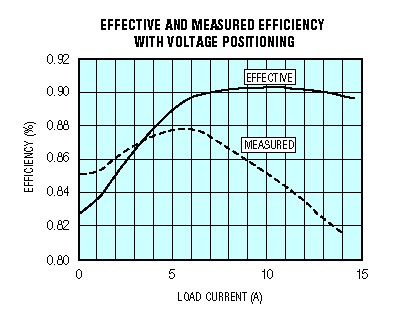

这种改善是以牺牲一部分转换效率为代价的,为便于将其与传统的(无电压定位的)电路相比较,引入一个新的概念“等效效率”。等效效率是指无电压定位的设计要达到和电压定位设计相同的性能所需具备的效率。

要确定电压定位调节器的等效效率,首先用传统方法[(VOUT × IOUT)/(VIN × IIN)]测出其效率,然后,在每个测点将负载等效为一个电阻(RLOAD = VOUT/IOUT)。对每个测点的 RLOAD 数据,利用无电压定位时的输出电压计算输出电流(INP = VNP/RLOAD,其中本例中 VNP = 1.6V)。然后,在每个 INP 测点计算等效效率,将对应的无电压定位时的输出功率(VNP × INP)除以实际测得的带有电压定位的输出功率(VOUT × IOUT)便得到等效效率。注意,等效效率超出 100%理论上来讲是可能的,不过还未能实现。

图 7 可以说明,对于一个典型的 CPU 电源,这种改善有多明显。一个传统设计需要将其满载效率提高将近 8%才能和电压定位所带来的好处相比。

图 7. 这些曲线显示,电压定位的 CPU 电源在满载时获得 8%的改善。14A 负载时,传统设计必须有 90%的转换效率才能与 82%效率的电压定位设计相匹敌。

责任编辑:pj

-

什么是DC/DC转换器?2024-09-29 854

-

降压型DC-DC转换器与升压型DC-DC转换器的输出纹波差异2024-04-24 2845

-

用开关稳压器设计您自己的DC-DC转换器2023-11-24 1276

-

R课堂 | 用开关稳压器设计您自己的DC-DC转换器2023-06-08 1534

-

MAX8515并联稳压器在DC-DC转换器的输出应用中的应用2023-03-30 2813

-

负载点DC-DC转换器解决电压精度、效率和延迟问题2021-12-14 2908

-

为什么使用DC-DC转换器应尽可能靠近负载的负载点(POL)电源?2021-12-01 2870

-

DC-DC转换器包括哪些部分2021-10-28 1873

-

电源芯片选择DC-DC还是LDO看了就知道2020-12-09 3035

-

何谓DC/DC转换器? 线性稳压器和开关稳压器(1)2019-05-15 2230

-

DC-DC转换器2010-03-09 4011

-

合理选择DC-DC 转换器2009-05-13 710

全部0条评论

快来发表一下你的评论吧 !