SRAM工作原理及设计

存储技术

描述

SRAM(Static Random Access Memory),即静态随机存取存储器。它是一种具有静止存取功能的内存,不需要刷新电路即能保存它内部存储的数据。

SRAM六管结构的工作原理

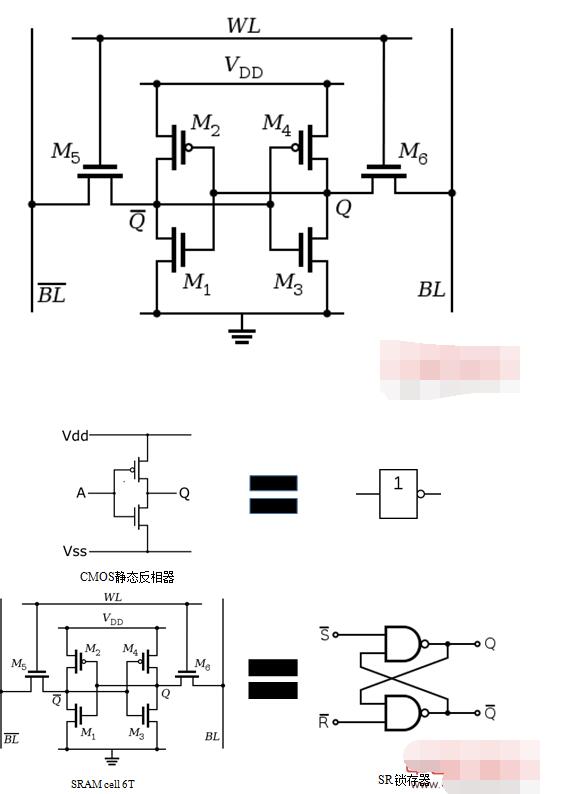

注:其实CMOS静态反相器等价于一个非门!SRAM cell 6T等价于SR锁存器(也就是RS触发器)

6T:指的是由六个晶体管组成,如图中的M1、M2、M3、M4、M5、M6.

SRAM中的每一bit存储在由4个场效应管(M1, M2, M3, M4)构成两个交叉耦合的反相器中。另外两个场效应管(M5, M6)是存储基本单元到用于读写的位线(Bit Line)的控制开关。

SRAM的设计

一个SRAM基本单元有0 and 1两个电平稳定状态。

SRAM基本单元由两个CMOS反相器组成。两个反相器的输入、输出交叉连接,即第一个反相器的输出连接第二个反相器的输入,第二个反相器的输出连接第一个反相器的输入。这实现了两个反相器的输出状态的锁定、保存,即存储了1个位元的状态。

除了6管的SRAM,其他SRAM还有8管、10管甚至每个位元使用更多的晶体管的实现。 这可用于实现多端口(port)的读写访问,如显存或者寄存器堆的多口SRAM电路的实现。

一般说来,每个基本单元用的晶体管数量越少,其占用面积就越小。由于硅芯片(silicon wafer)的生产成本是相对固定的,因此SRAM基本单元的面积越小,在硅芯片上就可以制造更多的位元存储,每位元存储的成本就越低。

内存基本单元使用少于6个晶体管是可能的— 如3管[5][6] 甚至单管,但单管存储单元是DRAM,不是SRAM。

访问SRAM时,字线(Word Line)加高电平,使得每个基本单元的两个控制开关用的晶体管M5与M6开通,把基本单元与位线(Bit Line)连通。位线用于读或写基本单元的保存的状态。虽然不是必须两条取反的位线,但是这种取反的位线有助于改善噪声容限。

SRAM的操作

SRAM的基本单元有3种状态:standby (电路处于空闲), reading (读)与writing (修改内容)。

SRAM的读或写模式必须分别具有“readability”(可读)与“write stability”(写稳定)。

Standby

如果字线(Word Line)没有被选为高电平, 那么作为控制用的M5与M6两个晶体管处于断路,把基本单元与位线隔离。由M1 – M4组成的两个反相器继续保持其状态,只要保持与高、低电平的连接。

Reading

假定存储的内容为1, 即在Q处的电平为高。 读周期之初,两根位线预充值为逻辑1, 随后字线WL充高电平,使得两个访问控制晶体管M5与M6通路。第二步是保存在Q的值传递给位线BL在它预充的电位,而泻掉(BL非)预充的值,这是通过M1与M5的通路直接连到低电平使其值为逻辑0 (即Q的高电平使得晶体管M1通路)。 在位线BL一侧,晶体管M4与M6通路,把位线连接到VDD所代表的逻辑1 (M4作为P沟道场效应管,由于栅极加了(Q非)的低电平而M4通路)。 如果存储的内容为0, 相反的电路状态将会使(BL非)为1而BL为0. 只需要(BL非)与BL有一个很小的电位差,读取的放大电路将会辨识出哪根位线是1哪根是0. 敏感度越高,读取速度越快。

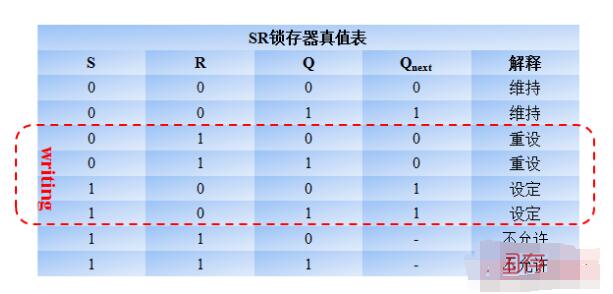

Writing

写周期之初,把要写入的状态加载到位线。如果要写入0,则设置(BL非)为1且BL为0。随后字线WL加载为高电平,位线的状态被载入SRAM的基本单元。这是通过位线输入驱动(的晶体管)被设计为比基本单元(的晶体管)更为强壮,使得位线状态可以覆盖基本单元交叉耦合的反相器的以前的状态!

-

SRAM特点及工作原理2010-08-02 6273

-

SRAM的基础电路及原理分析2023-10-01 7210

-

如何利用Verilog HDL在FPGA上实现SRAM的读写测试2025-10-22 4639

-

感光太阳能灯工作原理。#工作原理大揭秘jf_24750660 2022-11-07

-

【内存知识】DRAM芯片工作原理2010-07-15 9587

-

MOS存储单元的工作原理2021-07-28 2082

-

SRAM的工作原理及其使用方法了解2021-12-08 2450

-

声卡的工作原理2009-12-21 2369

-

QDR SRAM与Spartan3 FPGA的接口设计2011-06-01 6376

-

光耦的工作原理2015-12-25 2698

-

SRAM的工作原理图解2020-07-15 50420

-

SRAM存储器的工作原理2023-03-21 12567

-

NVSRAM的工作原理和架构分析2023-12-05 2164

-

SRAM和DRAM有什么区别2024-09-26 9955

全部0条评论

快来发表一下你的评论吧 !