基于51内核和FPGA器件实现便携式幅频特性测试仪的应用方案

电子说

描述

来源:电子技术应用,作者:丁昊;庄贵敏;宋杰;关键

在现代电力电子系统中,随着内场测试和外场维护工作量的增加,对目前通用的测试仪器也提出了新的要求,研制低成本、体积小的便携式幅频特性测试仪具有深远的现实意义。目前,结合新型微处理器芯片进行幅频特性测试仪的研制主要有三种技术途径:(1)采用单片机作为主控芯片,通过软件编程方式实现部分硬件功能,这种方案可以有效降低系统的复杂度,但在实时性上不尽人意。(2)应用可编程逻辑器件(如FPGA)进行设计可以有效解决高速数据流的实时处理问题,但在人机界面的设计中具有较大困难。(3)采用单片机与FPGA芯片结合的方式,通过外部总线连接和数据传输协议的设计,使得系统兼具两者的优势,从而成为设计人员首选的主流方案。

现代EDA(Electronic Design Automation)技术的发展和大规模FPGA器件的推出,使得在单片FPGA芯片中进行嵌入式8051 IP核设计成为可能。应用现代EDA技术,以FPGA器件为硬件平台,使用VHDL语言编程,可以实现与MCS-51系列单片机指令系统完全兼容的微控制器芯片IP(Intellectual Property)核。本文以此为基础,提出了幅频特性测试仪设计的新途径。系统以FPGA为核心采集处理模块,以Oregano公司开发的嵌入式MC8051内核(以下简称51内核)为显示控制核心,通过FPGA内部的正弦查找表IP核外加D/A模块的思想产生系统需要的扫频信号源,同时采用2.4英寸TFT彩屏液晶显示器进行人机界面设计,实现了便携式幅频特性测试仪的基本功能。该仪器具有小型化、频带宽、操作简单、测量精确度高、界面显示友好等优点,具有广阔的应用空间。

1 系统组成与工作原理

1.1 系统组成

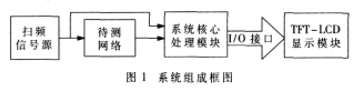

系统主要由正弦激励信号的产生模块和信号采集、处理和实时显示模块组成。其中前者采用基于“IP核+高速D/A”的思想产生扫频信号,后者主要包括FPGA核心板、双路高速A/D以及人机交互界面。在系统时钟和触发信号的驱动下,同时采集待测网络的输出信号以及系统的激励信号,并进行相应的数据处理,实现对有源或无源四端网络的幅频特性测试。系统组成框图如图1所示。

系统设计中需要解决的核心问题:(1)51内核的初始化配置问题。系统使用的51内核,可以直接通过顶层文件的端口例化实现与FPGA内部定义信号之间的连接,而51内核使用的存储器模块则需要用户进行配置。(2)数据流的速率匹配问题。经A/D采集得到的数据率远远超出了51内核的运算处理能力,因此系统中要进行数据缓存模块的设计。(3)彩屏液晶的显示控制。显示部分是该仪器的关键模块,系统采用TFT-LCD显示技术,可以进行友好的人机界面设计,但是彩屏液晶的初始化时序极其复杂,在动态曲线和测量数据的实时显示方面要进行优化设计。这些问题在实际设计中均得到了合理解决。

1.2 测量原理

对于一个线性时不变(LTI)系统,其冲激响应为h(t),在激励为正弦信号e(t)=Acos(?棕0t+?兹)时,系统的零状态响应为:

由此可以看出,系统输出的稳态响应也是一个正弦信号,其频率和输入信号的频率相同,但幅度和相位发生了变化,其中幅度变为原激励信号幅度的|H(j?棕0)|倍,|H(j?棕0)|称为电路网络幅频特性。

系统工作时,将等幅的正弦扫频信号作为输入信号激励被测网络。扫频信号的起始频率、终止频率、频率步进值以及扫描时间均可以通过按键输入的方式设置,也可以采用系统默认的设置方式(扫频范围1 kHz~1 MHz,频率步进1 kHz,扫描时间1 s)。高速A/D采集网络的输出信号和原始激励信号,并在FPGA内通过峰值检波程序得到网络输出信号的包络数据,同时与激励信号的幅值比较计算不同频点的增益数据。采用异步FIFO作为FPGA与51内核之间传输数据的缓冲器,并将其配置为“乒乓”工作模式。当触发信号到来时,将增益数据按照一定的格式和速率写入异步FIFO。当FIFO中存储一定数量的数据以后,在51内核同步时钟的控制下将数据读出并送往LCD模块,同时禁止数据继续写入FIFO,实现幅频特性曲线的显示。

2 系统硬件设计

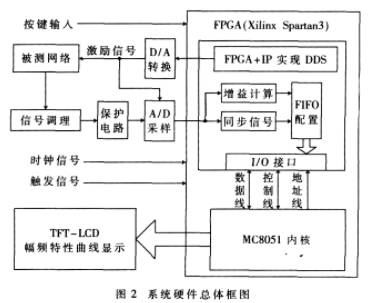

系统硬件主要实现正弦扫频信号的产生、网络输出信号的采集处理、数据的传输以及TFT液晶模块接口电路等功能,硬件总体框图如图2所示。

2.1 FPGA核心板模块

FPGA核心板模块是系统的核心,根据需要设计出FPGA最小系统板以及相关的A/D、D/A电路。其中,FPGA最小系统板采用Xilinx公司Spartan3系列的XC3S400-PQ208型40万门芯片,核心板采用5 V输入,由3片AMS1117实现5 V到3.3 V、5 V到2.5 V和5 V到1.2 V的电平转换。板上采用40 MHz有源晶振,满足高速设计要求。A/D为ADI公司高速模/数转换芯片AD9224,具有12位精度,且功耗低。D/A采用高性能高速率的AD9764AR芯片,该芯片具有14位分辨率和极佳的动态无杂波失真范围。

2.2 扫频信号源设计

扫频信号源的性能指标直接影响仪器的测试精度,本文采用DDS技术产生扫频信号。这里有两条途径可供选择,一种是采用专用的DDS芯片,如AD9854等,利用FPGA发送频率控制字产生扫频信号;另一种是采用FPGA中集成的正弦查询表IP核,这是一种利用“IP核+D/A”相结合来实现DDS技术的方法,在充分提高FPGA内部资源利用率的前提下,又可以有效降低系统的硬件复杂度和成本,因此系统采用该方式。

设计环境使用Xilinx公司的ISE7.1,通过Core Generator生成正弦查询表IP Core,查询表中的波形数据存储在FPGA的块存储器(Block Memory)中。查询表IP核的输入相位控制字THETA与实际相位之间的关系为:

该频率精度完全达到设计要求。

2.3 系统接口模块

在该系统中,液晶模块采用ILI9320片上系统(SoC)驱动器[2],颜色显示深度为18位,分辨率为240RGB×320像素。系统采用i80总线结构控制液晶显示,即通过读使能(RDB)和写使能(WRB)两条控制线进行读写操作,数据线的宽度为8位。液晶模块中的控制信号和数据信号均为标准的TTL电平,可以直接与FPGA的I/O接口相连。

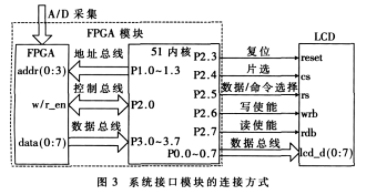

51内核具有8位总线宽度,通过内部端口映射的方式实现与FPGA模块的接口连接。为了实现FPGA采集数据的实时传输和显示,在接口设计中除了数据总线(data)以外,还需要地址总线(addr)和控制总线(w/r_en),按照程序设定的通信协议与FIFO中缓存的数据通信,实现数据传输和译码显示。系统接口模块的连接方式如图3所示。

3 系统软件设计

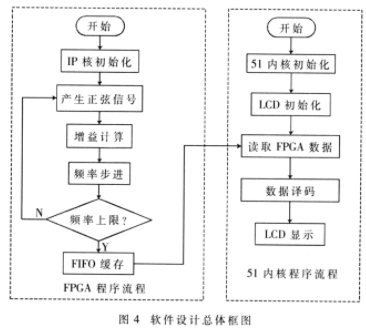

系统软件设计主要完成对正弦查找表IP核的初始化、峰值检波程序的设计、异步FIFO设计、FPGA与异步FIFO的通信协议设计以及同步显示等问题。软件设计总体框图如图4所示。

3.1 51内核的初始化配置

51内核采用完全同步的设计方案,在统一的时钟信号下控制每一个存储单元的读写操作。根据51内核处理速度的要求,在设计中使用20 MHz的时钟,时钟信号通过系统总时钟分频得到。设计中,首先在Keil编程环境中编译C语言代码,该代码主要负责LCD的初始化并将FPGA采集得到的实时数据进行译码和显示。编译后生成的.hex文件经相应的格式转换,生成FPGA的ROM资源可加载的.coe文件类型。

通过Xilinx提供的Core Generator工具,对IP核使用的DATA、XDATA和CODE三种存储区进行初始化配置,存储区的大小设置要以C语言程序所消耗的存储资源以及FPGA内部Block Memory资源总的大小而定。本系统中所有存储区的数据宽度均设置为8位,其中各存储区对应的地址信号宽度为7位、11位和14位。将CODE区配置为只读模式(Read Only),用于存放51内核的指令代码,并载入已经生成的.coe文件。经综合、翻译、映射、布局布线和生成编程文件完成51内核的设计过程[3]。

在51内核中实现彩屏液晶的显示控制和数据译码显示,可以大大减小因彩屏初始化时序复杂和FPGA在人机交互界面设计中的不灵活性而带来的难度[4]。同时,采用C代码对液晶屏进行操作具有广泛的通用性和可扩展性,当LCD的型号改变时,只需对初始化控制字稍作修改就可以实现显示控制。

3.2 峰值检波模块

系统采用软件编程的方法实现峰值检波的功能。首先将扫频区间等分,逐个测量等分点处的信号峰值并将计算出的增益存入FIFO中,当一次扫描结束后就能获得系统的幅频特性数据。

在对信号最值电压进行测量之前,由于信号很容易受到干扰,所以不排除信号会发生抖动的可能。基于这个原因,在测量前采用简易滤波对信号进行平滑处理,以减少最值测量的误差。这里采用取均值的方法。对输入信号依次取值、保存,形成一个新的信号,该信号电压由原输入信号的前两个时钟所得电压和后两个时钟所得电压之和取均值得到。对信号进行简易平滑处理后,所产生的新信号作为最值测量的基准信号。信号整形后得到标准的方波信号,该信号的一个周期刚好对应输入信号的两个周期,其中高电平和低电平各对应一个周期。

信号电压的峰峰值即为最大值减去最小值。但是,信号经过A/D转换器量化以后,所得到的值为12位偏码,扩展成为16位偏码,“1111111111111111”表示电压为2 V,“1000000000000000”表示电压为0

V,“0000000000000000”表示电压为-2 V。如果直接将最大值和最小值的偏码相减,结果会出现错误。因此采用先将最小值(电压负值)变为相应的电压正值的方法,即:

其中B表示最小值,A表示相应的电压正值,然后再将相应的电压正值与最大值相加,即为信号电压的峰峰值。

3.3 异步FIFO设计

A/D采集数据的数据率很高,本文中系统时钟为40 MHz,采集数据宽度为12位,这样每秒采集的数据量为40 M×12 bit/8=60 MB/s,如此高速的数据流远远超出了51内核的处理能力。为保证51内核读取数据的有效性和可靠性,系统中使用异步FIFO对数据进行缓存。FIFO的设计是通过配置FPGA内部的Block RAM资源实现的[5,6]。为了实现边采集边显示的目的,配置两块相同的FIFO,大小均为512×8 bit。在读写时钟的控制下,通过读使能和写使能信号的设置,使得在同一时刻始终有一块FIFO在进行写操作,而另一块FIFO将写满的数据读出。对于同一块FIFO不允许读写信号同时有效,这样接收和读取A/D数据并交给51内核处理可以同时进行,从而保证数据传输的连续性。

4 系统调试和测试

在完成了系统的硬件和软件设计以后,需要进行调试和测试。在测试时,使用一阶LC低通滤波网络,从所得到的频率特性曲线可以看出,系统主界面显示稳定,颜色信息丰富。当切换到系统状态设置或测试信息显示界面时,可以对激励信号的扫频范围、步进值、扫描时间等参数进行设置,同时还可以通过按键输入频点的方式查询各频点对应的增益,且具有较高的测试精度。

系统实现了在FPGA和51内核的平台下进行便携式幅频特性测试仪的总体设计。对设计中的核心模块进行调试,如51内核、TFT-LCD液晶、异步FIFO等。测试表明,系统工作稳定、测量精度高、实时性强,且硬件电路结构简单。目前系统已经应用到某型变压器绕组的幅频特性测试中,并取得了良好的测试效果。本文打破了以时序仿真和功能验证为目的的51内核研究,将51内核合理应用到电子系统设计实例中,并取得了成功,对于以后更加复杂的电子系统设计提供了参考和依据。

责任编辑:gt

-

便携式电容器测试仪的设计2009-12-07 816

-

应用于飞机线束检测的便携式线缆测试仪2018-08-31 3002

-

基于单片机和FPGA的频率特性测试仪的设计方案2019-07-22 1774

-

点阵液晶显示器在便携式频率特性测试仪中有哪些应用?2021-05-12 2179

-

便携式无线遥测应力测试仪的设计2009-08-14 977

-

基于ARM处理器的便携式XDSL测试仪设计2009-12-23 776

-

便携式低频幅频特性测试仪的研制?2009-05-06 1288

-

一种新型便携式转辙机测试仪的设计与实现_王全刚2017-02-07 813

-

便携式蓄电池内阻测试仪的研制2017-10-13 1684

-

基于MC8051内核的便携幅频特性测试仪设计[图]2018-01-19 632

-

便携式水质测试仪的应用、原理及特点2021-09-03 2365

-

ENJ2010 IGBT便携式测试仪2023-02-24 631

-

便携式三轴插拔力测试仪:工业精密测量革新工具2024-01-09 1605

-

474-便携式手提万兆网络协议测试仪2024-05-16 1117

-

信号测试仪设计方案476-便携式8路高频电压电流信号测试仪2024-05-28 1165

全部0条评论

快来发表一下你的评论吧 !