为什么微控制器接收的 CRC 编码与计算的 CRC 不一致?

处理器/DSP

描述

数字输出驱动器广泛用于工业应用中的过程控制(PLC 系统)和楼宇自动化,也可用于任何使用 24V DC 系统进行控制的应用,例如电机控制、机器人和机械自动化。

乍一看,数字输出驱动器是只有两种输出状态的简单器件:开或关;略微深入了解,就会发现,成功替代机械开关和继电器能够为工程师带来诸多好处,例如可靠性、低功耗、简单、较小尺寸、灵活性,可编程性,可以用其构建自动化、容错控制系统。

Maxim 的数字输出驱动器拥有高达 200kHz 的开关频率、快速且安全的电感负载消磁、负载开路 / 低电压 / 欠压检测、过流和过温保护、看门狗定时器以及 SPI 检错。器件能够承受高达 60V 电源尖峰脉冲、±1kV 浪涌脉冲,以及高达 12kV ESD 冲击,工作在 -40°C 至+125°C 宽温工作范围。

本文中,我们讨论如何有效利用 MAX14912/MAX14913 输出驱动器的不同特性。为实现这一目的,我们讨论系统设计师必须采取的决策,并了解综合权衡因素和 MAX14912/MAX14913 提供的好处。

确定系统工作状态

高边(HS)或推挽(PP)式?

一般来说,推挽式工作方式用于高速通信,信号波形应具有陡峭的边沿。该模式的缺点是输出总处于工作状态,为高电平或低电平,不能处于三态或具有高阻抗,除非使用 Global EN 引脚。

相反,高边工作方式允许工程师将输出置于高阻态,但信号波形很大程度上依赖于负载阻抗。高边模式下也可以将输出并联,支持高达 9.6A 的较大负载。

因此,工作模式的选择取决于具体的应用。

电源要求

MAX14912/MAX14913 支持从 12V 至 36V 的较宽范围电源,所以能够用于较宽范围的应用,甚至用于电源要求较低以及容限更宽的系统。这样可保证系统设计的可靠性和灵活性。

集成 5V DC-DC 转换器省去了额外的电源,最大程度减少外部元件的数量,以及提高系统效率。系统中的其它器件可由该 5V DC 电源供电,该电源能够为外部电路提供超过 100mA 的电流。

系统集成

数字输出驱动器是低电压 MCU/FPGA 与相对高电压(12V 至 36V)外设器件之间的接口,外设的例子包括执行器、电机、照明灯、继电器、LED 等。器件提供了对电压和电流尖峰脉冲、电感或电容负载、磁干扰和静态放电的高抗扰性。

此外,MAX14912/MAX14913 提供全面的诊断能力,包括热关断、开路检测、低电源和欠压检测、过压和过流保护。4 × 4 LED 驱动器矩阵可以对每通道的输出状态和故障状态进行指示。

数字接口

MAX14912 和 MAX14913 支持两种接口:并行和串行。系统设计师能够灵活使用并行或串行接口进行控制,或者同时使用两种接口。为便于理解接口,我们首先了解几个全局配置引脚。

全局配置引脚

EN – 该引脚为高电平时,器件处于正常工作模式;该引脚为低电平时,禁止任何输出操作,例如设置所有输出为高阻态。

SRIAL – 该引脚为高电平时,使能串行(SPI)操作;该引脚为低电平时,使能并行操作。

PUSHPUL – 该引脚为高电平时,使能推挽式工作模式;该引脚为低电平或浮空时,所有输出引脚处于高边工作模式。

FLTR – 该引脚为高电平时,使能所有并行逻辑输入和 CS 引脚上的尖峰脉冲滤波。

并行接口

并行接口是基于引脚的简单接口,用于控制驱动器输出。如果 SRIAL 引脚连接至地(SRIAL = 低电平),则通过并行接口控制器件。OUT_ 引脚的状态由对应 IN_ 引脚和全局配置引脚控制:PUSHPL、FLTR 和 EN。在并行模式下控制 MAX14912/MAX14913,至少需要 9 个 GPIO 引脚:控制 8 个输入引脚 IN_ 和 PUSHPL 引脚。FLTR 和 EN 引脚可始终保持为高电平。表 1 为引脚设置汇总。

并行模式引脚配置

注:MAX14913 在并行模式下不允许通过串行接口进行配置,而 MAX14912 即使在 SRIAL 为低电平时也可通过串行接口进行配置。该模式下可访问除寄存器 0 之外的全部寄存器(参见下文的“串行接口”部分)。

通过串行接口进行配置的优先级比 PUSHPL 引脚设置高。逻辑电平 0 (低电平)或 1 (高电平)取决于 VL 输入,1.6V 至 5.5V 有效。并行模式的缺点是缺少诊断信息。

串行接口

将 SRIAL 引脚驱动为 VL 电平(SRIAL = 高电平)时,使能 SPI 串行接口。串行模式下,所有输出引脚由内部寄存器设置和输入引脚控制。可通过串行接口引脚访问寄存器:CS、CLK、SDI 和 SDO。详细信息请参考 MAX14912/MAX14913 数据资料的串行接口部分。

循环冗余校验(CRC)、看门狗和滤波等部分特性仅受 CRC/IN3、WDEN/IN5 和 FLTR 引脚的输入逻辑控制,而负载开路检测和输出配置由 OL/IN1 和 PUSHPL 引脚的输入逻辑控制或通过寄存器设置控制。

此外,CMND/IN2、CNFG/IN7 和 S16/IN8 的设置见表 2 中的汇总。

SPI 接口模式选择

直接模式

直接 SPI 模式下,不需要命令字节。16 位模式下,高字节控制输出电平,低字节控制输出配置。CNFG/IN7 和 S16/IN8 设置为低电平时,只能访问寄存器 0;CNFG/IN7 和 S16/IN8 设置为高电平时,只能访问寄存器 1 和寄存器 2。

直接模式写操作期间,通过 SDO 引脚提供故障(F)和输出电平(L)诊断信息。

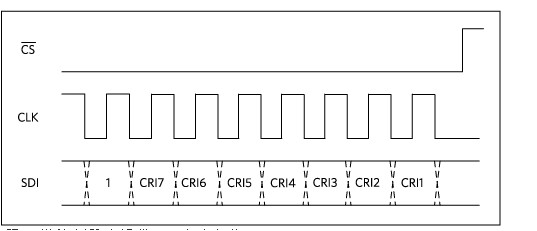

图 1. 16 位直接 SPI 模式下的 SPI 周期。

16 位 SPI 直接模式位定义

总结:

S16/IN8 = 低电平,且 CNFG/IN7 = 低电平时,一个字节的串行数据控制 OUT_ 状态;S16/IN8 = 低电平,且 CNFG/IN7 = 高电平时,一个字节的串行数据控制输出模式:高边或推挽式。

S16/IN8 = 高电平,且 CNFG/IN7 = 低电平时,两个字节的串行数据控制 OUT_ 状态和输出模式配置:高边或推挽式。

S16/IN8 = 高电平,且 CNFG/IN7 = 高电平时,第一个字节设置输出配置(高边 / 推挽),第二个字节使能 / 禁止负载开路检测功能。

建议首先设置配置寄存器,然后再更新输出电平。

注:返回的 F_ (故障)和 L_ (电平)信息针对之前写入的命令。为了获得实时故障和电平诊断信息,写两次。驱动器处于高边模式且使能负载开路检测时,无负载的 OUT_ 引脚由 75μA 电流上拉至 VDD 电平。在这种情况下,确定为 FAULT 条件。

命令模式

命令模式下,通过 SPI 接口提供所有特性和增强诊断信息。为设置为命令模式,CNMD/IN2 引脚必须为高电平。S16/IN8 和 CNFG/IN7 引脚输入被忽略。命令包含命令字节和之后的数据字节。总共有六种命令类型(命令说明见表 4,寄存器映射见表 5)。更多信息请参考数据资料。

命令模式协议

注:所有故障寄存器只能由任意命令周期中设置 Z = 1 清除。

寄存器映射

通信错误(CRC 检测)

循环冗余校验(CRC)是一种检错机制,可提高通信可靠性,以及避免意外执行错误命令。SPI 协议初始没有任何检错能力,在恶劣工业环境下可能破坏串行数据。使能 CRC 检测时(SRIAL= 高电平,CRC/IN3 = 高电平),来自 SPI 主机的所有命令之后必须有一个包括 7 位 CRC 编码的附加字节,如图 2 所示。

图 2. 微控制器应提供 SDI 校验字节

7 位 CRC 编码,也称为 CRC 帧校验序列(FCS),根据生成多项式计算(x7 + x5 + x4 + x2 + x + 1)。MAX14900E 也使用相同的多项式。更多信息以及 CRC 计算的 C 语言示例代码,请参考应用笔记 6002:“MAX14900E 八通道、高速工业开关的 CRC 编程”。

MAX14912 或 MAX14913 安装好后,器件检查接收到的数据是否存在误码,如果未检测到错误则执行命令。如果从微控制器接收的 CRC 编码与计算的 CRC 不一致,则忽略该命令,并置位寄存器 6 中的第 6 位 CRC 错误位。在下一个 SPI 帧将 CRC 错误报告给主机微控制器。

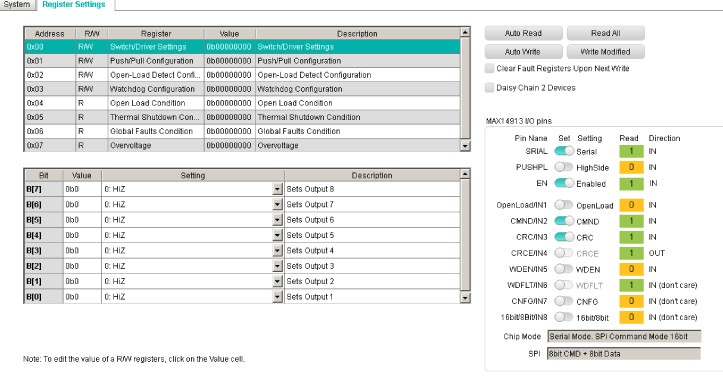

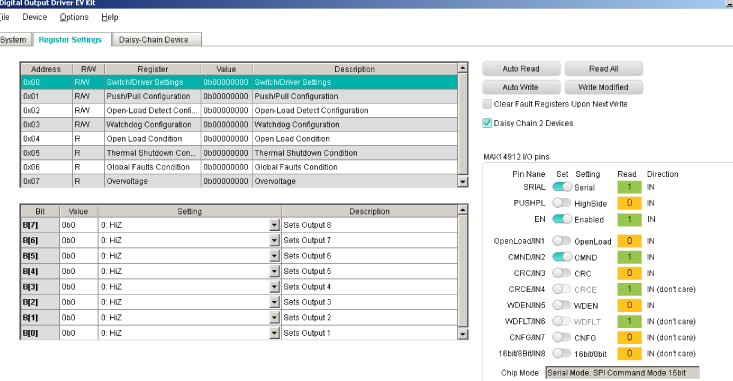

MAX14912EVKIT 评估软件内置有 CRC 计算器。如果 CRC/IN3 引脚为高电平,自动计算 CRC 字节并附加到 SPI 命令帧。从 Option 菜单中选中 Show Status Log 选项后,可在 Status Log 窗口中看到。

图 3. 数字输出驱动器 GUI 中的 CRC 计算。图 3. 数字输出驱动器 GUI 中的 CRC 计算。

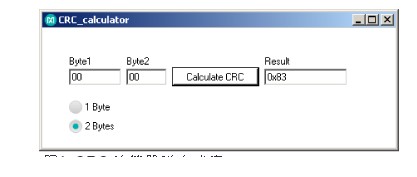

在 CRC 计算器弹出式窗口中,可手动计算 CRC 编码。进入 Help 菜单,点击 CRC 计算器,将其调出。输入字节 1 和字节 2 的值,然后点击 Calculate CRC 按钮,如图 4 所示。

图 4. CRC 计算器弹出式窗口。图 4. CRC 计算器弹出式窗口。

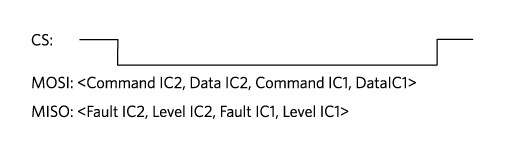

多个 IC 的菊链配置

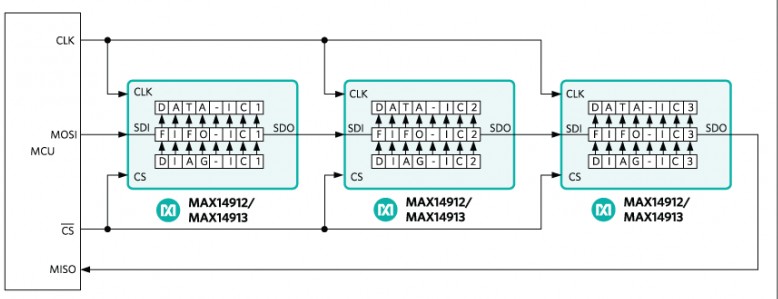

MAX14912 和 MAX14913 支持多个器件采用菊链配置,通过单命令方法控制 / 监测同一 SPI 总线上的所有器件。所有器件使用相同的 CLK 和 CS 信号;第一片器件的 SDI 引脚连接到主机的 MOSI 引脚,最后一片器件的 SDO 引脚连接到主机的 MISO 引脚。第一片器件的数据输出(SDO)引脚连接到第二片器件的数据输入(SDI)引脚,如图 5 所示。其它器件通过类似的方式以菊链连接。

图 5. 菊链连接。

MAX14912/MAX14913EVKIT 支持两个评估板采用菊链连接,但相同的命令结构适用于三片或更多器件。

例如,16 位模式下两片器件菊链连接的命令帧。

Daisy-chain devices

安装评估板时,应使下一片器件 EVKIT #2 的 J24 连接头连接到上一片器件 EVKIT #1 的 J23,如图 6 所示。USB 电缆或外部主机应连接到 EVKIT #1。此外,EVKIT #1 的跳线 J26 必须处于位置 2 至 3,EVKIT #2 的跳线 J26 应处于位置 1 至 2。必须手动将 EVKIT #2 的跳线 J9、J5、J4、J22、J10、J6、J12、JMP1、J11、JMP2、J8 和 J3 的位置设置为与 GUI 中一致。更多信息请参考 MAX14912/MAX14913 数据资料和原理图。

图 6. 菊链连接的 MAX14912EVKIT。

如图 7 所示,应选中菊链连接选择框。

图 7. 菊链操作。

菊链连接不仅对扩展输出通道的数量没有限制,而且也支持通过组合使用数字输出驱动器和数字输入接收器,构建更加复杂的系统。例如八通道数字输入隔离器 / 串行器家族,MAX31910/MAX31913。

驱动电感负载

MAX14912 和 MAX14913 具有对电感负载进行安全消磁(SafeDemag)的功能,防止高边模式下电感负载关断时引起的反冲电压损坏芯片。如果您需要驱动大电感,例如执行器、继电器或电机,当电流由芯片通过负载流向地时,电感负载中储存较大的能量。当高边开关关断造成电流终止时,能量转换为 OUT_ 引脚上的负向尖峰脉冲。内部齐纳二极管将尖峰脉冲箝位到(VDD -56V)。例如,如果 VDD = 24V,则将 OUT_ 引脚箝位到 -32V (相对于地)。在这种情况下,由于能量与|V x I|成比例,电感负载中储存的能量将快速释放。然而,能量越大,释放需要的时间越长。在此时间期间,芯片的温度可能会达到安全门限。为防止危险的热击穿,激活低边开关,使能量释放较小,直到内部温度达到安全范围。

责任编辑:pj

-

CAN总线采样点不一致的危害2025-06-07 885

-

增量编码器计数值和实际角度不一致怎么办?2024-04-08 5060

-

充放电不一致影响超级电容器性能的原因及解决方案2024-02-03 3937

-

什么是电芯的不一致性?电芯不一致会造成什么后果?2023-11-06 6630

-

为什么bootloader发出CRC校验与固件的校验值不一致呢2022-08-24 2342

-

锂电池组不一致性的原因及危害是怎样的2021-03-17 13274

-

如何实现对通信数据的CRC计算2020-09-29 4300

-

CRC校验 、STM32中CRC计算单元、 CRC应用2020-03-04 7663

-

CRC算法原理和CRC编码的实现方式与使用Verilog对CRC编码进行描述2019-08-06 2350

-

分布式大数据不一致性检测2018-01-12 1056

-

感兴趣区域不一致性决策算法2018-01-02 984

-

基于偏好不一致熵的偏好决策方法2017-12-05 858

-

CRC的LSB表示方式该如何计算?2015-03-05 3211

全部0条评论

快来发表一下你的评论吧 !