基于DSP控制算法和可编程逻辑器件实现多相变频控制器的设计

处理器/DSP

描述

在电机驱动系统应用中,多相电机驱动系统可以应用在供电电压受限制的场合,其作用是:(1)解决低压大功率的问题;(2)减小振动和噪音。由于电机相数增加,输出转矩脉动减小、脉动频率增加,使驱动系统低速特性得到很大的改善;(3)提高可靠性。由于相数冗余,当多相电机驱动系统中有一相甚至几相发生故障时,电机仍可运行。因此,多相电机驱动系统特别适合于高可靠性要求的场合,多相系统的这些优点引起学术界和工程界的广泛关注。由于多相系统采用的开关器件多,控制系统复杂,所以对多相系统控制器的性能要求较高[1-3]。

在三相变频控制系统中,虽然DSP控制算法结构复杂,但运算速度高、寻址方式灵活和通信性能强大等特点,已经得到了广泛应用。而对于多相变频控制系统,还要求控制器的实时性能高、能够处理大量数据,并且要有更多接口用于PWM驱动信号,而这些要求FPGA都能满足。

因此,本文在三相PWM信号产生方法的基础上,提出一种基于DSP和FPGA的多相PWM信号的产生方法。采用这种方法设计了多相变频控制器,其具有一定的通用性,可以通过上位机软件对相数、调制波波形和控制方法进行在线设置。

1 多相变频控制器设计思想

多相变频控制器的通用性表现在:(1)多相电机的相数可选;(2)载波频率可选;(3)根据谐波注入的需要,可选择不同调制波;(4)依据电机连接方式,可选择不同的控制方法。

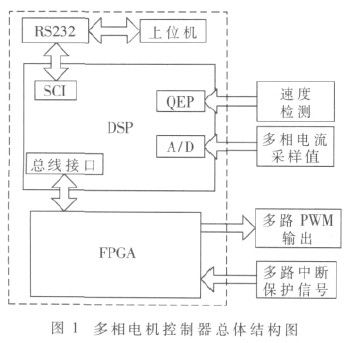

为了实现上述功能,本文采用模块化的方法对控制器结构进行了设计,控制器由上位机、DSP和FPGA三部分构成,其总体结构框图如图1所示。

上位机的操作软件由面向对象的软件实现。从控制面板上可以控制电机运行、停止,并且可对电机相数、载波频率、调制波波形、死区时间等进行设置。

为了最大限度地发挥DSP和FPGA各自的优势,由DSP主要实现控制算法、采集反馈信号及与上位机进行通信;由FPGA实现调制算法,产生多相PWM信号,这部分占用硬件资源多,而且对实时性要求高。

控制过程如下:

(1)上位机与DSP通过串行接口相连,在需要动作时向DSP发出指令。

(2)DSP根据接收到的指令调用相关函数,如对系统进行初始化、运行相应的控制算法、进行信号采集等。

(3)通过DSP与FPGA并行通信,DSP对FPGA进行调制算法的初始化并解除PWM封锁,FPGA根据接收到的频率和幅值进行计算,产生PWM信号。

2 多相PWM波形产生

2.1 SPWM波形产生原理

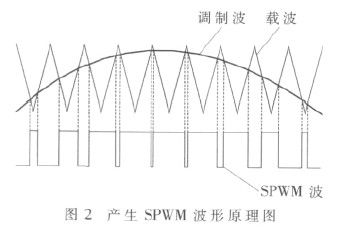

正弦脉宽调制(SPWM)的产生原理如图2所示。用一组等腰三角形波与一个正弦波比较,其交点作为SPWM波的上升或下降时刻。当正弦波幅值大于三角波幅值时,输出为高电平;当正弦波的幅值小于三角波的幅值时,输出为低电平。

利用FPGA生成SPWM的基本原理是将三角波发生器产生的数字信号与存储在ROM中的正弦波信号相比较,根据两者的大小来决定SPWM波的输出。

2.2 多相PWM波形产生

图3给出了三相SPWM信号的产生方法。序列发生器的作用是按顺序产生A相、B相、C相的时钟信号;地址合成与数据分离利用了分时复用的原理,目的是为了减少ROM的使用数量。多相正弦波只需一个ROM即可,也为外挂ROM创造了条件[5]。

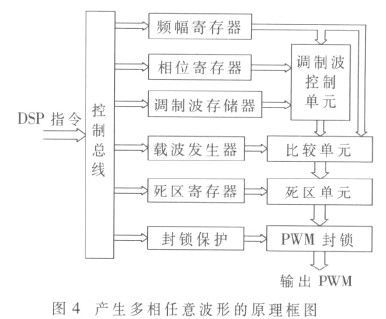

在三相SPWM信号产生方法的基础上,本文提出一种基于DSP和FPGA的能产生任意相数、任意波形(即调制波形)的方法,如图4所示。

相位寄存器中保存着各相调制波间移向角度(如三相为120°)的信息,所以对相位寄存器的设置是实现多相PWM信号的必要步骤。

调制波控制单元是实现多相PWM信号的核心部分,这部分的功能与图3中序列发生器、地址合成及数据分离部分类似,但是有如下不同:

(1)生成的调制波之间的相移是可以通过设置相位寄存器而自由改变的,而图3中其相移是固定的,无法在线更改。

(2)规定三相调制波信号构成一组调制波发生器(如图3为一组),而调制波控制单元则由多组调制波发生器构成,组间的对应相相差的相移是可以设置的。例如在控制双三相电机时,通常采用组内相移设为120°,组间相移设为60°或30°。

调制波存储器的功能类似于图3中的正弦波ROM,它存储由DSP计算得到的正弦波形或带有谐波的调制波波形。控制器每次上电后都要通过DSP对调制波存储器进行初始化设置,将DSP计算出的调制波表下载到调制波存储器。

频幅寄存器中存储着调制波幅值和频率,幅值和频率在每个控制周期中由DSP计算得到。载波发生器(即三角波发生器)的载波频率在线可调;死区寄存器存有当前的死区值,也可在线更改。封锁保护单元用于在系统出现故障时封锁PWM输出信号,保护主电路。

由于每个寄存器或存储器中的数字信号均由DSP计算产生,所以必须通过DSP对FPGA的初始化和设置,FPGA才能实现以上功能。

3 多相变频控制器实现

控制器采用型号为TMS320F2812的DSP作为主控芯片,这是一款专为电机控制所设计的芯片,不仅具有运算速度快的特点,而且集成了丰富的片内外设资源。利用TMS320F2812片内集成的16路12 bit A/D,可以对多达16路的电流或电压进行采样;TMS320F2812的事件管理器模块带有QEP电路,可以对编码器的正交编码脉冲进行解码和计数,从而实现计算电机转子位置和转速。

考虑到多相系统需要的资源很大以及功能的扩展,采用Altera公司CycloneII系列的FPGA芯片EP2C35F484作为控制芯片,并在外部扩展了100 MHz的有源晶振作为时钟输入,以提高控制精度。FPGA在完成PWM信号产生的同时,还兼顾故障保护的任务,当接收到某一相的外部故障信号时,封锁这一相的PWM信号。硬件的实时保护,提高了控制器的可靠性。

3.1 DSP与FPGA的通信接口设计

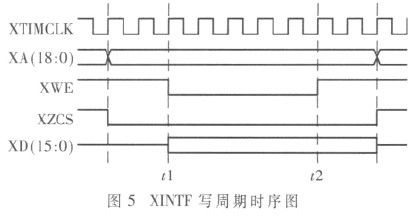

为了保证DSP和FPGA通信的快速性,DSP利用外部接口(XINTF)模块与FPGA的用户I/O口相连。由于选用的芯片两者接口电压都为3.3 V,故将DSP外部接口(XINTF)模块的16 bit数据总线、19 bit地址总线与写信号线XWE和FPGA的用户I/O口直接相连,实现并行通信。

XINTF写周期时序如图5所示[6]。从图中可以看出,在XWE的下降沿时刻,地址线XA的信号已送到总线上,而数据线XD的信号刚送到总线上;在XWE的上升沿时刻,地址线XA和数据线XD的信号均存在于总线上一段时间,而且已经稳定,所以令FPGA捕捉XWE的上升沿,在此时刻读取信号,以保证DSP和FPGA通信的准确性。

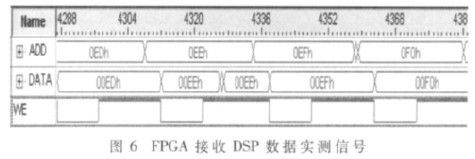

通过DSP和FPGA的并行通信实验,得到如图6所示

的FPGA 在线接收到的由DSP 发送出的递增数据( 地址和数据相同) 实测信号图, 与分析结果相符。

3.2 软件设计流程

系统软件部分主要由主程序和中断服务程序构成。主程序包括对DSP 中断、外设以及FPGA 调制策略的初

始化; 中断服务程序主要完成恒压频比控制算法、速度闭环PID 调节器的控制算法以及刷新频幅寄存器。其程序流程图分别如图7 、图8 所示。

4 实验结果

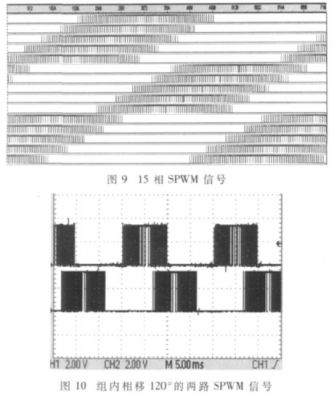

利用本文方法设计的控制器产生5组、每组3相(即15相SPWM)信号,组内相移设为120°,组间相移设为72°。图9为利用FPGA的输入口观测15相SPWM的15个上桥信号的波形,图10为利用示波器观测组内相移120°的两路SPWM信号波形,图11为组间相移72°的两路SPWM信号波形,图12为同一相上下桥SPWM信号的波形。

本文提出了一种基于DSP和FPGA的多相PWM信号实现方法,并设计实现了多相变频控制器。此控制器可以对多种相数的电机进行变频控制和多种控制方法的选择,虽然目前还不够完善(如无法实现矢量控制),但是其通用性和灵活性为多相电机的研究提供了一个良好的实验平台。

责任编辑:gt

-

Xilinx可编程逻辑器件的高级应用与设计技巧绝版教程2012-02-27 17685

-

可编程逻辑器件2014-04-15 3676

-

什么是可编程逻辑控制器?可编程逻辑控制器有哪些特点?2021-07-05 3292

-

PLD可编程逻辑器件2021-07-22 2321

-

可编程逻辑器件设计2006-03-25 1179

-

可编程逻辑器件基础及应用实验指导书2010-03-24 785

-

什么是PLD(可编程逻辑器件)2009-06-20 30042

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1163

-

复杂可编程逻辑器件_CPLD_在DSP交流电机控制系统中的应用2016-04-15 651

-

由可编程逻辑器件与单片机构成的双控制器2017-01-12 886

-

可编程逻辑器件(书皮)2022-07-10 786

-

电可编程逻辑器件EPLD是如何设计的2022-08-22 2248

-

可编程逻辑器件的结构2023-03-24 2130

-

可编程逻辑器件测试2023-06-06 1302

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4576

全部0条评论

快来发表一下你的评论吧 !