AD9772A在WCDMA发送电路中的应用(ad9772a中文资料)

应用电子电路

描述

在介绍数模转换芯片AD9772A的基础上,详细描述了AD9772A的两大特点。结合实际工程,给出了芯片的一种应用方案,提供了一些调试经验。

关键词:数模转换,锁相环,内插滤波,WCDMA

AD9772A是ADI公司推出的一款高速、宽带的数模转换器(DAC),采用单电源供电、内插过采样,最高支持160 MSPS的输入数据速率。在提供充分动态输入范围情况下,可以最优的重构产生基带和中频波形。CMOS工艺制造,片内集成了带有2倍内插滤波器和锁相环路的低失真DAC,锁相环路提供了所有片内所需时钟和控制信号。基于外部稳定时钟源考虑,AD9772A为时钟提供了灵活的输入管脚,既可支持单端形式输入时钟,也可支持差分时钟输入;模拟输出也有两个差分电流输出管脚,为AD9772A应用拓宽了空间。

1 AD9772A内部结构

AD9772A内部模块依据功能可以划分为:时钟产生和控制模块,输入锁存模块,内插滤波模块,“零填充”模块,数模转换模块以及输出参考电路。图1是AD9772A的功能模块图。

1.1 时钟产生和控制模块

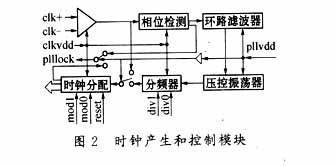

时钟产生和控制模块使用锁相环实现,主要为片内各个功能模块提供时钟和控制信号,环路的参数直接决定了数模转换的性能。

时钟产生和控制模块由差分输入,相位检测,环路滤波(外围电路配置),压控振荡器(VCO),分频器和时钟分配模块组成。

依据输入数据速率,锁相环路有两种工作模式:当输入数据速率大于6 MSPS时,锁相环路工作,相应的管脚PLLVDD=Vcc,PLLCOM=gnd;当数据速率小于6 MSPS时,为了获得更高的相噪性能,不使用内部的锁相环路,相应的管脚PLLVDD=PLLCOM=gnd。

无“零填充”时,参考时钟是输入数据速率的2倍;有“零填充”时,参考时钟是输入数据速率的4倍。对于QPSK调制来说,当使用内部锁相环时,锁相环路本身可以保证2个AD9772A芯片时钟和数据同步;不使用内部锁相环时,通过复位管脚(RESET),能够实现2个AD9772A芯片时钟和数据同步。

锁相环典型的开机锁定时间是100 ms。

时钟产生和控制模块的环路滤波器和压控振荡器模块由PLLVDD管脚统一供电,时钟差分输入、相位检测、分频器和时钟分配模块由CLKVDD管脚统一供电,为了确保最优的环路相位噪声性能,在设计电路时,要保证PLLVDD和CLKVDD来自相同的“干净的”模拟电源。是否使用片内锁相环,可以通过配置PLLVDD管脚实现,当使用内部锁相环路时,PLLLOCK表征环路是否锁定的信号,PLLLOCK电平为高,环路锁定;PLLLOCK电平处于高和低之间时,环路未锁定。当禁止内部锁相环路时,PLLLOCK提供了1倍内部时钟输出。

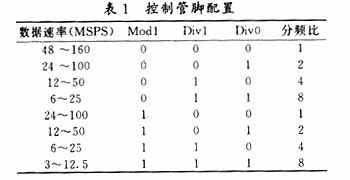

根据输入数据速率,分频器和时钟分配模块的控制管脚配置如表1所示。

1.2 内插滤波器

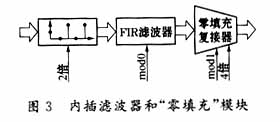

AD9772A内插滤波器是在两个原始抽样点之间插入1个零值,然后通过一个FIR滤波器,插入的零点就可以还原为准确的内插值,提高了时域分辨率〔1〕。内插后的信号频谱为原始离散序列谱经2倍压缩后得到的谱,但是得到的频谱包含了有效频谱的高频镜像,根据AD9772A的应用环境,合适地选择低频频谱或高频镜像。如果保留高频镜像,输出信号频率提高了2倍,频谱结构没有变化,起到了上变频的作用。

AD9772A的FIR滤波器采用43阶对称滤波器实现,阻带可以达到73 dB的衰减。如果系统需要在宽带内获得更高的动态范围,AD9772A必须工作在基带方式下,相应的管脚MOD0=gnd,FIR内插滤波器表现为低通特性,输入数据频谱到第一个镜像频谱的距离增加,有利于模拟低通滤波器的设计。基带模式下使用“零填充”,相应的管脚MOD1=Vcc,虽然频谱的通带更加平坦,但是无杂散动态范围(SFDR)减小,阻带抑制不够,信噪比(SNR)减小。AD9772A工作在中频模式下时,MOD0=Vcc,FIR内插滤波器表现为高通特性,当中频超过输入数据速率,必须使用“零填充”,增加通带的范围。

输入时钟经过信号产生和控制模块送给各个功能子模块,输入数据经过一级锁存,进入2倍内插滤波器和“零填充”,增加了DAC的更新速度,使后继电路容易设计,内插和填充后的数据送入模数转换器,完成数字信号到模拟信号的变换。

2 AD9772A在WCDMA发送电路中的应用

WCDMA(宽带码分多址)系统基站发送物理信道多,数据动态范围较大,AD9772A提供了14位输入管脚、0.1dB的带内波动、73dB的带外衰减和高达74dB的SFDR,通过与模拟低通滤波器的配合,能够获得失真和噪声性能很好的基带模拟信号,可以满足基带发射性能指标。AD9772A应用时,应该从系统的角度设计AD9772A的参数,这些参数包括:输入数据速率、时钟频率、复位信号、锁相环路、模式配置、分频比和参考电阻等。图4是WCDMA基站部分发送电路功能框图。

2.1 电路设计

为了获得“干净”的基带信号,做印刷电路板(PCB)时,模拟电路部分和数字电路部分尽量集中,不能交叉布线。而AD9772A输入是数字信号,输出是模拟信号,芯片中同时存在数字电压、数字地、模拟电压和模拟地,芯片各个功能模块由不同电源供电,对这些信号处理时,要遵循以下原则:片内锁相环路工作时,PLLVDD=CLKVDD=3.1V~3.5V;DVDD1-2=CLKVDD±0.3V。

数模转换部分受电源纹波的影响较大,经过稳压器的电源一定要滤掉电源纹波后才可以加到DAC的5个电源输入管脚。一般的措施是电源和相应地之间加几个不等值的滤波电容,滤掉不同频率的纹波。

2.2 输入数据速率和时钟频率

AD9772A的输入数据和时钟不仅仅要满足工作时序的要求,同时要根据后继电路设计参数以及系统要求的一些参数来决定。对于WCDMA的BTS(基站)基带发送电路来说,电路板上共有4类时钟资源,3.84 MHz,7.68 MHz,15.36 MHz,30.72 MHz。从频域看,内插滤波器的输出是以DAC频率为周期频谱,π的位置是时钟频率,且DAC频率为时钟频率的2倍,扩频信号的带宽为3.84 MHz。DAC输出信号经过宽带运算放大器和模拟低通滤波器送给模拟调制模块。为了尽可能保留基带谱和有效抑制带外频谱,模拟低通滤波器选用SCLF-5。SCLF-5的通带截止频率是5 MHz,3 dB带宽5.8 MHz,8 MHz~10 MHz内只能达到大于20 dB的衰减,10 MHz~200 MHz内可以达到大于40 dB的衰减,BTS基带发送扩频信号的带宽是5 MHz。根据以上参数,选择时钟频率为15.36MHz。

2.3 内插滤波器对输入数据的要求

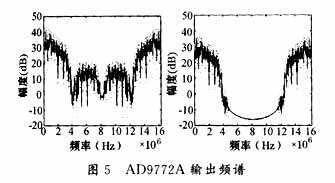

输入数据的动态范围不够时,例如,BPSK调制系统中,信号线、高电压和地三种资源如何分配到AD9772A的14位输入管脚,对重构模拟信号的周期频谱影响很大。主要原因是内插时,内插滤波器能否插出准确的值。当输入数据的最大值接近16383时,对两个输入数据最大值之间的插值就不能够通过内插滤波器得到,内插出现错误,重构信号频谱如图5所示。

上述仿真是在采样速率为15.36 MHz,信号带宽4.08 MHz的条件下获得的。第一个仿真图是输入数据的最大值太大时,输出信号的频谱。很显然,在周期频谱之间存在很大的能量谱,这部分谱经过模拟低通滤波器滤不掉,导致系统性能下降。第二个仿真图是输入数据的最大值适中时,输出信号的频谱,符合要求,模拟低通滤波器可以将基带谱提取出来。根据仿真结 果,输入数据没有丰富的动态范围时,要使其输入数据集中在中值附近,上下波动是最大值的1/4。

3 结束语

AD9772A最高支持160MSPS的数模转换速率,提供了宽广的动态输入范围,特别适合应用在宽带通信系统中。AD9772A采用48管脚的低四方扁平封装(LQFP),工业级温度系数,占用印刷电路板空间小,适应环境能力强。

AD9772A可以直接处理低中频信号,在软件无线电方面也有一定的应用。

-

AD9772A:高性能14位DAC的全面解析2026-04-16 386

-

MPC9772数据表2023-03-24 371

-

AD9772A14位、160MSPS TxDAC+®,带2 X插值过滤数据表2021-06-16 721

-

AD9772:14位、150MSPS TxDAC+™,带2个插值过滤过时数据表2021-05-07 727

-

数模转换芯片AD9772A具有什么特点?有什么应用?2021-04-21 1187

-

14位MSPS的160个DAC的插值滤波器AD9772A数据表2017-10-17 892

-

采用幅值调制的红外线发送电路2011-07-26 1288

-

采用幅值调制的红外发送电路2010-02-25 949

-

AD9772A,pdf datasheet (with In2009-09-21 475

-

数模转换芯片AD9772A的特点及其应用2009-05-04 3823

-

接触传感器信号发送电路2009-04-26 522

-

光发送电路2009-03-06 1446

-

心电信号监测发送电路2009-02-28 966

全部0条评论

快来发表一下你的评论吧 !