CDMA手机中频率合成器设计方案

网络协议

14人已加入

描述

对CDMA手机频率合成器的各关键部分进行分析,提出了设计方案。

关键词:CDMA手机,射频前端,频率合成器,相位噪声

1引言

随着移动通信技术的发展,CDMA作为新一代的工作制式正得到广泛的应用和研究,中国联通已初步在全国范围内建立了CDMA的网络。CDMA手机的研制开发成为国内外各大手机厂商的热点。频率合成器在CDMA手机射频部分起着心脏的作用。在CDMA移动台规范标准IS-98C中,要求频率间隔为30kHz,这就使得频率合成器具有很大的分频比,可达30000以上,要满足在分频比很大情况下的带内相位噪声要求就成为需要解决的问题。另外,还要考虑高阶环路的设计、锁定时间和电路简单性等问题。本文针对这一课题进行分析与设计,提出了解决方案,得到了较好的结果。

2CDMA手机频率合成器指标要求及分析

CDMA手机频率合成器指标要求如下:输出频率范围954.42~979.35MHz;频率增量30kHz;输出功率范围-6~0dBm;相位噪声-136dBc/Hz@900kHz;转换时间4ms。

2.1 锁相环频率合成器的原理及噪声的来源

频率合成器的组成如图1所示。在锁相环路的反馈支路中插入一个可变数字分频器。环路输入信号是一个高稳定度的参考源经Rref次分频后,频率为fr的脉冲信号。它与压控振荡器的输出经N次分频后得到频率为fN的脉冲信号,在鉴相器进行相位比较。当环路锁定时,压控振荡器输出频率fo=Nfr,改变分频比N,就可以改变输出频率。任何频率源的输出频谱都不可能是完全纯净的,或多或少都伴随有随机性的相位噪声和周期性的杂散干扰。前者呈现为连续的频谱,用功率谱密度表示;后者为集中的线谱。噪声的来源分为两大类:一类是输入噪声与干扰;另一类是内部噪声与干扰。这些噪声和干扰会使环路产生输出相位噪声,使输出信号频谱不纯,频率稳定度变差。

2.2 数字式单环锁相频率合成器的杂散输出分析

(1)环路对杂散干扰的滤除能力

按杂散干扰作用于环路的不同位置,可将干扰分为三类。

第一类干扰:作用于鉴相器的输入端,即参考晶振的谐波干扰。环路对第一类干扰的滤波能力H1

(jΩ)为:

式中:N为可变分频器分频比;Kd为鉴相器鉴相增益;Ko为VCO压控灵敏度;

H(jΩ)为环路闭环传递函数;F(jΩ)为环路滤波器传递函数;Ω为基带角频率。

第二类干扰:作用于鉴相器的输出端,主要是鉴相器的纹波干扰。环路对第二类干扰的滤波能力H2(jΩ)为:

第三类干扰:作用于压控振荡器的输入端,凡能进入压控控制线的干扰均属此类。环路对第三类干扰的滤波能力为:

综上所述,环路对第一、二类干扰呈现低通滤波特性,而对第三类干扰呈现带通滤波特性。欲降低第一、二类干扰的影响则环路带宽越窄越好,但对Ω?ωn的第三类干扰则环路带宽大些为好。这显然给环路带宽的选择带来了矛盾,必须针对具体的干扰来源合理选择环路参数才能使环路对干扰具有优良的滤波能力。

(2)减小寄生杂散干扰输出的方法

寄生杂散干扰主要是鉴相器的纹波干扰。当环路锁定时鉴相器的输出电压或电流实际上并非理想的直流电压或电流,多少存在一些有害的交流成分,这些有害成分一般为鉴相频率的基波和谐波,习惯上称为纹波。若环路对此纹波抑制不力,纹波就会对压控振荡器进行调频,使输出产生寄生杂散干扰边带。此纹波电压出现在鉴相器的输出端,属于第二类干扰。根据(1)式和调制理论可推得环路的边带纹波抑制比为:

式中:N为可变分频器分频比;ΔV为鉴相器输出纹波的幅度,由所用PLLIC决定;τ为鉴相器输出纹波的脉宽,由所用PLLIC决定;Kd为鉴相器鉴相增益,由所用PLLIC决定;ξ为环路的阻尼系数;ωn为环路的自然谐振角频率;为了减小VCO由于纹波电压造成的寄生边带,除了设计时要注意减小N外,只有减小ωn或ξ。然而ωn也不能太小,它受到环路锁定捕捉时间的限制。要进一步对纹波进行滤除,需在环路中加入辅助滤波器。增加一级RC辅助低通滤波器带来的边带纹波抑制比改善为:

R′=20lg(ωc/ωr) (5)

式中:ωc为RC低通的截止角频率;ωr为环路的鉴相角频率;为了不影响原二阶环各项性能,要求:ωc≥5ωn;ξ的值也不是越小越好,因为环路的暂态过程有过冲现象,过冲量的大小与ξ有关,ξ越小,过冲量越大,环路的相对稳定性就越差。综合考虑,工程上一般选择ξ=0.707。电源的不完善或抖动也会造成寄生杂散输出。频率合成器中对电源噪声最敏感的部件是振荡器,特别是一个宽调谐的VCO。当VCO的调谐斜率是15MHz/V,它表示每μV的根均方纹波产生15Hz的根均方频率。在50Hz上它表示根均方相移φ为0.3rad。在150Hz上1μV的根均方纹波成分给出:

从噪声和纹波两者的观点出发,不应当把任何电源直接馈给一个高斜率VCO的调谐控制部分。必须把电源接到一个电源纹波抑制作用大的,而同时具有低噪声特性的运算放大器。在频率合成器中电源的设计是很严格的,特别对于VCO,一般来说,它必须采用与自己位置尽可能靠近的低噪声、低纹波稳压器来供电。

2.3 数字式单环锁相频率合成器的输出相位噪声

(1)传递函数的分析

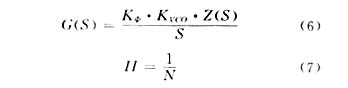

单环数字式频率合成器中,噪声的来源很多。不同的噪声源对环路输出噪声的贡献也不相同。于图2所示的锁相环路,定义:

不同相位噪声源的传递函数见表1。

从表1中可以看出,参考源、分频器、鉴相器相位噪声的传递函数中含有一个共同的因子,即:

因此,可以把这几个噪声源称为带内噪声源。环路带宽及相位裕量可以定义为:

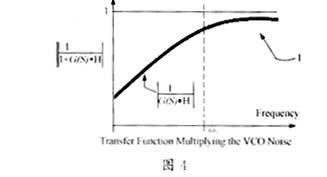

从G(S)单调递减的特性,可得VCO。

(2)最佳环路带宽的分析设计

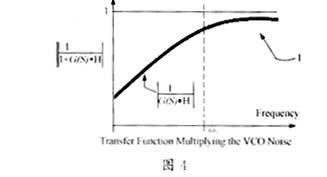

从上面的分析中可以看出,在环路带宽以内,输出信号的相位噪声主要由带内噪声源贡献,在环路带宽以外,输出信号的相位噪声则主要是由VCO引起的,如图5所示。测量的结果表明,当环路带宽足够大以至可以消除VCO噪声的影响时,离载波频率很近的地方的相位噪声大小基本上与环路带宽

无关。在设计锁相环时,为了使输出的总的相位噪声的性能最好,通常把图5中VCO的相位噪声曲线与带内噪声源的相位噪声曲线(折合到VCO的输出频率)的交点取为最佳环路带宽。要注意,尽管环路带宽以内的相位噪声主要取决于带内噪声源,但也含有一点VCO的噪声贡献。特别是在环路带宽

很窄,VCO的相位噪声很差的情况下。

(3)相位噪声基底分析相位噪声基底计算公式是:

相位噪声基底主要由PLL的制造商的工艺和电路结构决定,鉴相频率每下降一个倍频程,噪声基底改善3dB。在美国国家半导体的PLL资料上,给出的基底噪声可达-210dBc/Hz以上。

(4)输出相位噪声的综合考虑

由分析可知,CDMA手机中采用的频率合成器,只要选取的参考晶振的指标比较好(这一点是很容易满足的,而且成本也不高),带内的相位噪声几乎全部取决于鉴相器的噪声基底,带外的相位噪声则取决于未控VCO的相位噪声性能。根据下面的公式,可以得到带内噪声的理论值:

3器件的选择与电路实现

作为手机中使用的频率合成器的元器件选择,通常主要考虑相位噪声、体积、功耗、价格等因素。下面就简单地分析一下用我们所选择的PLL、VCO、TCXO可能达到的最佳指标。

PLL选用国家半导体的LM2332;PLL折合到900MHz,有效噪声基底恶化为-75dBc/Hz。

MURATA公司的VCO芯片MQK002-967可以满足调谐灵敏度典型值24MHz/V±6MHz的要求,其相位噪声指标为:-82dBC/Hz@1kHz,-100dBC/Hz@10kHz,通过对其建模,可算出·81·@900kHz处,相位噪声优于-138dBC/Hz。TCXO频率合成器的频率稳定度取决于TCXO的稳定度。TCXO采用的是kinseki:频率为19.68MHz、相位噪声-105dBc/Hz@100Hz、-125dBc/Hz@1kHz、-140dBc/Hz @10kHzOffset。

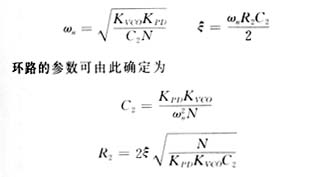

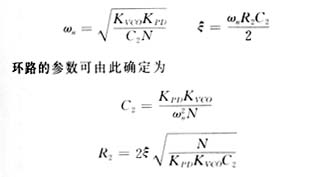

环路滤波器有无源和有源两种形式,考虑到体积与噪声等因素,在手机中一般采用无源三阶环路滤波器。至于元件参数的确定,很多资料上都给出了很成熟的经验公式,这里不再讨论。具体电路如图6所示。实践证明,按照公式:

C1可选择为C2/15<C1<C2/10,计算结果与实际能很好地吻合。

通过对电路的连接调试,得到当环路带宽为1kHz时,带内相位噪声可以达到-72dBc/Hz,与理论值基本相同。因此带内噪声主要由鉴相器和分频器的相位噪声基底产生,晶振的相位噪声由于总分频比N/R不大,所以对带内噪声基本没有影响。带外噪声由VCO决定,在偏频900kHz处为-138dBc/Hz,能够满足系统要求。由于辅助滤波器的作用,基本看不到鉴相频率的纹波。而此时环路的锁定时间为800μs,符合电路要求。

参 考 文 献

1 卢尔瑞等.移动通信工程.北京:人民邮电出版社,1993

2 Recommended Minimum Performance Standard forDual-Mode Wideband Spread Spectrum Cell ular MobileStation.TIA/EIA IS-98-A Interim Standard,April 1996

3 Mobile Station-Base Station Compatibility Standard forDual-Mode Wideband Spread Spe ctrum CellularSystem.TIA/EIA IS-95-A,December,1992

4 张厥盛等.锁相技术.西安:西安电子科技大学出版社,1998

打开APP阅读更多精彩内容

关键词:CDMA手机,射频前端,频率合成器,相位噪声

1引言

随着移动通信技术的发展,CDMA作为新一代的工作制式正得到广泛的应用和研究,中国联通已初步在全国范围内建立了CDMA的网络。CDMA手机的研制开发成为国内外各大手机厂商的热点。频率合成器在CDMA手机射频部分起着心脏的作用。在CDMA移动台规范标准IS-98C中,要求频率间隔为30kHz,这就使得频率合成器具有很大的分频比,可达30000以上,要满足在分频比很大情况下的带内相位噪声要求就成为需要解决的问题。另外,还要考虑高阶环路的设计、锁定时间和电路简单性等问题。本文针对这一课题进行分析与设计,提出了解决方案,得到了较好的结果。

2CDMA手机频率合成器指标要求及分析

CDMA手机频率合成器指标要求如下:输出频率范围954.42~979.35MHz;频率增量30kHz;输出功率范围-6~0dBm;相位噪声-136dBc/Hz@900kHz;转换时间4ms。

2.1 锁相环频率合成器的原理及噪声的来源

频率合成器的组成如图1所示。在锁相环路的反馈支路中插入一个可变数字分频器。环路输入信号是一个高稳定度的参考源经Rref次分频后,频率为fr的脉冲信号。它与压控振荡器的输出经N次分频后得到频率为fN的脉冲信号,在鉴相器进行相位比较。当环路锁定时,压控振荡器输出频率fo=Nfr,改变分频比N,就可以改变输出频率。任何频率源的输出频谱都不可能是完全纯净的,或多或少都伴随有随机性的相位噪声和周期性的杂散干扰。前者呈现为连续的频谱,用功率谱密度表示;后者为集中的线谱。噪声的来源分为两大类:一类是输入噪声与干扰;另一类是内部噪声与干扰。这些噪声和干扰会使环路产生输出相位噪声,使输出信号频谱不纯,频率稳定度变差。

(1)环路对杂散干扰的滤除能力

按杂散干扰作用于环路的不同位置,可将干扰分为三类。

第一类干扰:作用于鉴相器的输入端,即参考晶振的谐波干扰。环路对第一类干扰的滤波能力H1

(jΩ)为:

式中:N为可变分频器分频比;Kd为鉴相器鉴相增益;Ko为VCO压控灵敏度;

H(jΩ)为环路闭环传递函数;F(jΩ)为环路滤波器传递函数;Ω为基带角频率。

第二类干扰:作用于鉴相器的输出端,主要是鉴相器的纹波干扰。环路对第二类干扰的滤波能力H2(jΩ)为:

第三类干扰:作用于压控振荡器的输入端,凡能进入压控控制线的干扰均属此类。环路对第三类干扰的滤波能力为:

综上所述,环路对第一、二类干扰呈现低通滤波特性,而对第三类干扰呈现带通滤波特性。欲降低第一、二类干扰的影响则环路带宽越窄越好,但对Ω?ωn的第三类干扰则环路带宽大些为好。这显然给环路带宽的选择带来了矛盾,必须针对具体的干扰来源合理选择环路参数才能使环路对干扰具有优良的滤波能力。

(2)减小寄生杂散干扰输出的方法

寄生杂散干扰主要是鉴相器的纹波干扰。当环路锁定时鉴相器的输出电压或电流实际上并非理想的直流电压或电流,多少存在一些有害的交流成分,这些有害成分一般为鉴相频率的基波和谐波,习惯上称为纹波。若环路对此纹波抑制不力,纹波就会对压控振荡器进行调频,使输出产生寄生杂散干扰边带。此纹波电压出现在鉴相器的输出端,属于第二类干扰。根据(1)式和调制理论可推得环路的边带纹波抑制比为:

式中:N为可变分频器分频比;ΔV为鉴相器输出纹波的幅度,由所用PLLIC决定;τ为鉴相器输出纹波的脉宽,由所用PLLIC决定;Kd为鉴相器鉴相增益,由所用PLLIC决定;ξ为环路的阻尼系数;ωn为环路的自然谐振角频率;为了减小VCO由于纹波电压造成的寄生边带,除了设计时要注意减小N外,只有减小ωn或ξ。然而ωn也不能太小,它受到环路锁定捕捉时间的限制。要进一步对纹波进行滤除,需在环路中加入辅助滤波器。增加一级RC辅助低通滤波器带来的边带纹波抑制比改善为:

R′=20lg(ωc/ωr) (5)

式中:ωc为RC低通的截止角频率;ωr为环路的鉴相角频率;为了不影响原二阶环各项性能,要求:ωc≥5ωn;ξ的值也不是越小越好,因为环路的暂态过程有过冲现象,过冲量的大小与ξ有关,ξ越小,过冲量越大,环路的相对稳定性就越差。综合考虑,工程上一般选择ξ=0.707。电源的不完善或抖动也会造成寄生杂散输出。频率合成器中对电源噪声最敏感的部件是振荡器,特别是一个宽调谐的VCO。当VCO的调谐斜率是15MHz/V,它表示每μV的根均方纹波产生15Hz的根均方频率。在50Hz上它表示根均方相移φ为0.3rad。在150Hz上1μV的根均方纹波成分给出:

从噪声和纹波两者的观点出发,不应当把任何电源直接馈给一个高斜率VCO的调谐控制部分。必须把电源接到一个电源纹波抑制作用大的,而同时具有低噪声特性的运算放大器。在频率合成器中电源的设计是很严格的,特别对于VCO,一般来说,它必须采用与自己位置尽可能靠近的低噪声、低纹波稳压器来供电。

2.3 数字式单环锁相频率合成器的输出相位噪声

(1)传递函数的分析

单环数字式频率合成器中,噪声的来源很多。不同的噪声源对环路输出噪声的贡献也不相同。于图2所示的锁相环路,定义:

因此,可以把这几个噪声源称为带内噪声源。环路带宽及相位裕量可以定义为:

从G(S)单调递减的特性,可得VCO。

(2)最佳环路带宽的分析设计

从上面的分析中可以看出,在环路带宽以内,输出信号的相位噪声主要由带内噪声源贡献,在环路带宽以外,输出信号的相位噪声则主要是由VCO引起的,如图5所示。测量的结果表明,当环路带宽足够大以至可以消除VCO噪声的影响时,离载波频率很近的地方的相位噪声大小基本上与环路带宽

很窄,VCO的相位噪声很差的情况下。

(3)相位噪声基底分析相位噪声基底计算公式是:

相位噪声基底主要由PLL的制造商的工艺和电路结构决定,鉴相频率每下降一个倍频程,噪声基底改善3dB。在美国国家半导体的PLL资料上,给出的基底噪声可达-210dBc/Hz以上。

(4)输出相位噪声的综合考虑

由分析可知,CDMA手机中采用的频率合成器,只要选取的参考晶振的指标比较好(这一点是很容易满足的,而且成本也不高),带内的相位噪声几乎全部取决于鉴相器的噪声基底,带外的相位噪声则取决于未控VCO的相位噪声性能。根据下面的公式,可以得到带内噪声的理论值:

3器件的选择与电路实现

作为手机中使用的频率合成器的元器件选择,通常主要考虑相位噪声、体积、功耗、价格等因素。下面就简单地分析一下用我们所选择的PLL、VCO、TCXO可能达到的最佳指标。

PLL选用国家半导体的LM2332;PLL折合到900MHz,有效噪声基底恶化为-75dBc/Hz。

MURATA公司的VCO芯片MQK002-967可以满足调谐灵敏度典型值24MHz/V±6MHz的要求,其相位噪声指标为:-82dBC/Hz@1kHz,-100dBC/Hz@10kHz,通过对其建模,可算出·81·@900kHz处,相位噪声优于-138dBC/Hz。TCXO频率合成器的频率稳定度取决于TCXO的稳定度。TCXO采用的是kinseki:频率为19.68MHz、相位噪声-105dBc/Hz@100Hz、-125dBc/Hz@1kHz、-140dBc/Hz @10kHzOffset。

C1可选择为C2/15<C1<C2/10,计算结果与实际能很好地吻合。

通过对电路的连接调试,得到当环路带宽为1kHz时,带内相位噪声可以达到-72dBc/Hz,与理论值基本相同。因此带内噪声主要由鉴相器和分频器的相位噪声基底产生,晶振的相位噪声由于总分频比N/R不大,所以对带内噪声基本没有影响。带外噪声由VCO决定,在偏频900kHz处为-138dBc/Hz,能够满足系统要求。由于辅助滤波器的作用,基本看不到鉴相频率的纹波。而此时环路的锁定时间为800μs,符合电路要求。

参 考 文 献

2 Recommended Minimum Performance Standard forDual-Mode Wideband Spread Spectrum Cell ular MobileStation.TIA/EIA IS-98-A Interim Standard,April 1996

3 Mobile Station-Base Station Compatibility Standard forDual-Mode Wideband Spread Spe ctrum CellularSystem.TIA/EIA IS-95-A,December,1992

4 张厥盛等.锁相技术.西安:西安电子科技大学出版社,1998

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

一种用DDS激励PLL的X波段频率合成器的设计方案2023-10-24 439

-

将MAX2902与外部频率合成器组合2023-03-03 1452

-

pll频率合成器工作原理与pll频率合成器的原理图解释2023-02-24 11306

-

锁相环频率合成器是什么原理?2021-04-22 2571

-

如何采用DDS实现频率合成器的设计?2021-04-20 1658

-

什么是频率合成器2019-08-19 5672

-

如何利用FPGA设计PLL频率合成器?2019-07-30 4438

-

无线寻呼系统中频率合成器的设计2011-05-17 631

-

低相噪毫米波频率合成器设计2010-04-22 2978

-

DDS+PLL高性能频率合成器的设计方案2010-04-17 5003

-

频率合成器,频率合成器原理及作用是什么?2010-03-23 15270

全部0条评论

快来发表一下你的评论吧 !