混合压缩/内置自我测试解决方案的应用优势分析

测量仪表

描述

作者:明导公司Ron Press

扫描测试是测试集成电路的标准方法。绝大部分集成电路生产测试是基于利用扫描逻辑的 ATPG(自动测试向量生成)。扫描 ATPG 是一项成熟的技术,特点是结果的可预测性高并且效果不错。它还能实现精确的缺陷诊断,有助于进行分析并改进。随着集成电路尺寸的增长并且制造工艺的规模越来越小,嵌入式压缩被加入了扫描 DFT(可测性设计)逻辑,从而将测试时间缩短了多个数量级。如今,嵌入式压缩已经十分常见。

但是,当很少有或没有可用的测试仪界面时,有些设备必须进行测试。在这种情况下,内置自我测试 (BIST) 十分有必要。最近,集成电路在安全关键型应用(如汽车应用和医疗应用)方面的增长已经带动了内置自我测试的需求增长。但越来越多的集成电路会同时需要这两种不同类型的测试。嵌入式压缩和逻辑内置自我测试使用了类似的逻辑方法,因此通过在混合测试解决方案中共享压缩和内置自我测试逻辑来节省 DFT 逻辑面积就变得十分合理。DFT 和每项技术的基础架构也能为其它技术带来优势。这种混合压缩/内置自我测试解决方案不仅能够节省 DFT 面积,还能带来更好的测试质量。

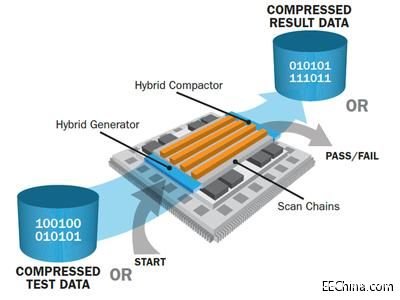

有了混合测试方法,你就能选择从测试仪中提供嵌入式压缩 ATPG 向量或在设备逻辑内置自我测试中自动应用和分析向量。你可以凭借在一个或多个区段中(图1)的中央控制器和共享压缩解码器/ LFSR 和压缩器/MISR 逻辑按照从上到下的流程插入混合逻辑。你也可以按照从下到上的流程插入混合逻辑,使你能够在每个区段完成逻辑插入,包括包装器 (Wrapper) 隔离链。拥有混合测试逻辑的区段能够用于任何一种集成电路中并且逻辑内置自我测试或区块嵌入式压缩向量能够被直接重复使用。即插即用逻辑和向量方法在顶级集成电路中节省了大量的 ATPG 时间。

图1. 混合测试解决方案,压缩(嵌入式决定性测试)和逻辑内置自我测试共享大部分解码器/ LFSR 和压缩器 /MSIR 逻辑

嵌入式压缩 ATPG 为混合解决方案中的逻辑内置自我测试带来了优势。由于嵌入式压缩 ATPG 拥有出色的生产缺陷检测功能,逻辑内置自我测试就不需要拥有强大的缺陷检测能力。因此,随机向量抵抗逻辑所需的测试点相应要少,从而大大减少逻辑内置自我测试面积。嵌入式压缩的另一个优势就是低功耗测试。混合测试方法利用低功耗移位逻辑,因此用户能够在 ATPG 或内置自我测试中选择切换活动。

同样地,混合方法中的逻辑内置自我测试为嵌入式压缩 ATPG 带来了优势。逻辑内置自我测试为去除未知状态而使用的 X-bounding 对于在 MISR 内生成可预测的信号十分必要。它还能加强 ATPG 电路的可测性,尤其是在增加更多测试点的情况下。因此,混合方法中的逻辑内置自我测试基础架构能够使嵌入式压缩 ATPG 拥有更高覆盖和更少向量。ATPG 通常是缺陷检测的主要方法,但有了逻辑内置自我测试,每个缺陷的检测次数提高了(较高的多重检测),因此能够加强检测。

这就是混合测试方法吸引逻辑内置自我测试用户的所有理由。事实上,需要自发测试和高品质生产 ATPG 向量的汽车集成电路设计师已经采用了这种方法。许多人没有意识到的是,这种方法还为 ATPG 带来了显着的优势,虽然现在还没有严苛的逻辑内置自我测试要求。有了这种方法,老化不再需要测试仪来应用 ATPG 向量,因为用户能够使用逻辑内置自我测试,并且整体 ATPG 压缩和向量数目能够得到改进。

作者简介:

Ron Press 是明导硅测试解决方案产品的技术营销经理。他在测试和 DFT(可测性设计)行业有着25年的经验,曾多次出席全球各地的 DFT 和测试研讨会。他出版了数十篇与测试相关的论文,是国际测试会议 (ITC) 指导委员会的成员、IEEE 计算机学会 (IEEE Computer Society) 的 Golden Core 成员以及 IEEE 的高级会员。Press 拥有多项减少引脚数测试和无干扰时钟切换的专利。

责任编辑:gt

-

混合系统的优势所在2009-02-25 4800

-

汽车电子测试测量解决方案2009-11-26 48685

-

【资料分享】免费获取测试测量解决方案,轻松愉快解决问题2015-06-17 3677

-

介绍混合信号测试解决方案2015-06-25 3382

-

DKH企业级大数据解决方案的优势分析2018-11-02 2710

-

混合信号示波器解决方案2019-06-03 2448

-

什么是思科CleanAir解决方案?2019-08-07 2382

-

用于LCD TV电源的内置和测试的GreenPoint解决方案2020-06-17 2423

-

混合扫描测试解决方案的优势是什么2021-05-11 1526

-

测试应用与解决方案手册分享2022-06-08 7027

-

泰克嵌入式系统及混合信号电路测试解决方案2010-07-26 904

-

混合信号测试解决方案介绍2010-08-06 661

-

深度解读混合信号测试解决方案2015-05-26 1128

-

一种混合前缀编码的测试数据压缩方法2017-01-07 717

-

数字示波器及混合信号的测试解决方案介绍2017-11-13 1442

全部0条评论

快来发表一下你的评论吧 !