通过利用XCore处理器的特点及硬件设计软件化方案

处理器/DSP

描述

引言

英国的XMOS Semiconductor公司推出了一种全新的控制器件:事件驱动多核心处理器(以后简称XCore处理器)。凭借一种叫作软件化芯片(Software Defined Silicon)的新技术,XMOS提出了一种革命性的电子设计方法:硬件设计软件化。通过软件设计,可以使用XCore处理器实现以前需要通过FPGA,ASIC实现的硬件性能。这种新的处理器集RISC CPU的效率、DSP的性能和FPGA的灵活性于一体。

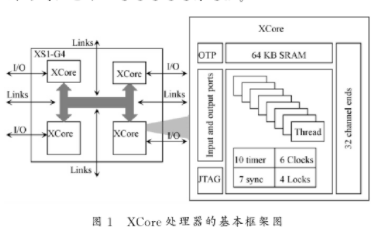

1 XCore处理器的基本构架

图1为XCore处理器的基本框架图。如图所示,每个处理器(以XS1-G4为例)有4个内核(XCore),XCore之间通过一种称之为X-link的技术连接,可以实现XCore之间的数据通信。XCore内部有丰富的硬件资源:8 KB的OTP ROM,64 KB的RAM,10个计算器,6个时钟模块,7个同步单元和4个硬件锁。除此之外,XCore最特别的是具有8个硬件线程和32个通道端(Channel Ends)以及1个事件驱动管理器。每个硬件线程具有独立的专有寄存器组,同时可以访问所在核内的共享硬件资源。

通道(Channel)是线程之间通信的主要方式,一个通道可以连接几个通道端。这样,使用各个通道端的硬件线程就可以相互通信了。通道可以在不同的Xcore之间建立,依托强大的X-link功能,甚至不同处理器之间的线程也可以通过通道进行通信。

2 XCore处理器特点

2.1 硬件多线程技术

硬件多线程技术是XCore处理器能够硬件设计软件化的关键。有别于传统的操作系统实现的多线程,硬件多线程是通过特有的硬件单元来调度。每个硬件线程的时间片精确到1个时钟周期(对应于处理器工作在400 MHz主频的情况下,就是2.5 ns)。传统的操作系统分配给线程的时间片都是在ms级。线程调度的实时性保证了多个硬件线程可以组成高性能的处理流水线。每个Xcore拥有8个硬件线程,如果这个8个线程全部运行,在400 MHz的CPU主频的情况下,理论上可以组成一条8级的主频为50 MHz的流水线;如果处理器内的4个XCore全部运行,则可以组成4条这样的并行流水线。这足以完成大部分中低性能的FPGA实现的功能。

2.2 多功能智能IO模块

多功能智能IO模块是XCore处理器的另一大特色,该模块可以对IO数据进行处理,然后再将数据缓存后送CPU内核处理,这样,可以减轻IO操作对CPU内核的负担。使得流水线设计瓶颈可以缓解。设计者可以适当延长处理流水线每一级的长度,使得软件设计更加灵活,功能更加强大。

多功能智能IO模块具有以下几个功能:端口宽度可编程;带时钟、片选的IO接口;可编程时序IO接口;序列化IO接口;可编程FIFO缓存接口;可编程条件IO接口。灵活运用这些功能,可以轻易的实现MII,ULPI等高速总线接口。

2.3 事件驱动运算

相对于操作系统管理下的软件线程,XCore处理器的硬件线程具有同样的灵活性。每个硬件线程可以被阻塞,当硬件线程被阻塞时处于睡眠状态,它所占用的时钟周期可以释放给其他的硬件线程。举个例子,如果某个XCore以400MHz的工作频率运行8个线程,那么每个硬件线程的实际工作频率是50 MHz。当其中4个线程被阻塞时,剩下的4个硬件线程的工作频率就能够提升到100MHz。当线程被阻塞时,需要等待指定的事件将它唤醒,这些事件可以由定时器、智能IO模块和线程之间通信的通道产生。基于事件驱动运算的机制,可以极大地减少XCore处理器的功耗并显着地提升XCore处理器的效能。

3 实例介绍

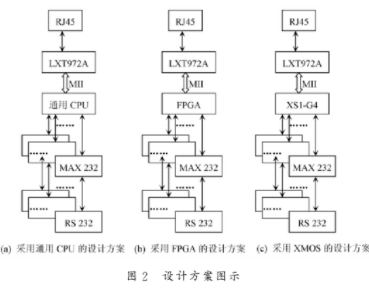

串口服务器是在工业控制领域经常用到的一类设备,其作用是实现UART与以太网之间的协议转换,下面给出了3个不同的设计方案:采用通用嵌入式CPU实现的设计方案;采用FPGA实现的设计方案;以及采用XCore处理器设计方案,如图2所示。

这3个方案比较类似,基本上都是单核心处理芯片加外围接口芯片的SOC解决方案。不同的是,第1个方案的处理核心是集成了以太网MAC和UART的通用处理器。第2个方案的处理核心是FPGA器件。第3个方案的处理核心是XCore处理器。

第1个方案的优点是设计起来容易、功能灵活;在通用嵌入式CPU上运行操作系统,使用标准的TCP/IP协议和UART协议,能够实现各种复杂的控制功能。缺点也很明显:CPU内部集成的串口有限,一般只能实现不超过4个串口的串口服务器;实时性差、由于软件处理能力有限,当串口数据流量较大时,CPU会来不及处理,只能将数据放入缓存,待CPU空闲时处理。这样导致数据转发的延迟增大。

第2个方案的优点是扩展能力强、实时性高;由于FPGA具有硬件可编程的特点,理论上器件内部可以实现任意个数目的串口(实际受所选FPGA器件容量大小的影响)。FPGA采用硬件流水线处理串口数据转以太网数据,因此,数据处理的速度很快,基本上不产生延迟,实时性好。这种方案的缺点是:设计难度比较大,需要获得授权使用以太网MAC和UART的IP模块,并且需要设计控制模块来协调各个接口,然后进行系统级的仿真和测试,整个设计开发周期长、设计难度大;灵活性差,功能不强。由于采用硬件实现的机制,FPGA只能实现简单的底层网络报文,无法实现TCP/IP等高层次的网络协议转发。同样,一些诸如流量控制、报文路由、IP管理之类的功能也无法实现。这样、导致这个方案的可用性以及可维护性差。

第3个方案综合了2个方案的优点并弥补了它们的不足。首先,XCore处理器的IO管脚像FPGA一样是可以编程设计的。设计者可以分配足够多的管脚给UART。使用标准XCore处理器函数库,每个UART模块需要1个硬件线程来实现,每个以太网MAC模块需要4个硬件线程来实现。这样,使用4个核的Xcore处理器,可以实现具有16个串口的串口服务器。除实现UART和以太网MAC需要的20个硬件线程外,处理器内还剩下12个硬件线程的资源,这些硬件线程可以用来运行TCP/IP协议,还可以用来实现流量控制、报文路由、IP管理等诸多功能。由于XCore处理器具有实时多线程的特点,能够保证处理IO数据的硬件线程实时运行,从而保证了数据转发的实时性。同时,XCore处理器设计属于软件编程的范畴,使用C语言就可以方便地实现各种控制管理功能,这使得开发周期缩短,开发难度降低。

4 结语

从上面的研究分析、实例介绍可以看出:相对于传统的控制器件,XCore处理器具有优异的性能和充分的灵活性,很适合用在一些对处理器功能要求多、实时性要求高的场合。同时,XCore处理器采用C语言编程的特点可以使开发难度以及开发周期大大降低,再考虑到XCore处理器丰富的硬件资源,采用XCore处理器的硬件设计软件化方案是一种能够广泛应用的低成本、高效率解决方案。

责任编辑:gt

-

龙芯处理器支持WINDOWS吗?2025-06-05 6828

-

调节多核处理器硬件适应软件设计方法2008-09-25 3850

-

工业应用理想选择多核处理器2018-09-04 1946

-

数字信号处理器的特点2020-12-09 2107

-

求一个ARM处理器高效异常处理的解决方案?2021-02-23 1509

-

嵌入式微处理器的发展和特点2021-12-22 1364

-

网络处理器软件开发模型的研究2009-04-15 421

-

视频处理器软硬件协同设计2011-08-04 1010

-

Supermicro(R)利用新处理器和高速互连技术拓展高性能解决方案2011-11-14 1412

-

Stellaris处理器的硬件设计参考2017-10-13 1400

-

基于LM3S8962微处理器的网络化智能遥控家电系统的设计方案的概述2018-05-10 1252

-

FPGA Nios嵌入式处理器的硬件开发2021-01-15 1241

-

“硬件软件化”,32位处理器的开发与8位处理器的开发资料下载2021-04-22 1188

-

通过利用现代处理器架构的并行性提高SDR的性能2022-06-14 1799

-

XMOS xcore-voice 解决方案2024-06-12 1427

全部0条评论

快来发表一下你的评论吧 !