sparc处理器的特点和系统架构

描述

1.前言

前几天我看到知乎上的一篇文章《时代的眼泪:繁华落尽的SPARC处理器》,大致上讲述了一下Sun公司的UltraSPARC处理器,那时左批HP,右打IBM,俨然一副高高在上的气势。我觉得关于SPARC如何一步一步从繁荣走向平淡,又是如何在历史长河中发挥出浓墨重彩的一笔,我就不赘述了。这篇文章主要想讲一些sparc体系相关的问题。目前,sparc出现在我们视野中并不多见,其实利用sparc处理器一直是航天上面在使用,由于其特殊的架构以及目前美国对中国的态势,sparc架构在航天、飞机、雷达领域的利用也是越来越重要了。目前北京微电子技术研究所出来几款SPARC V8架构的芯片。其中BM3803是基于SPARC V8体系结构的32位精简指令集的国产嵌入式芯片,其特点是功能强、可靠性高、低功耗等等。下面从系统启动、窗口寄存器、中断处理这三部分看一看sparc v8处理器的特点。

2.sparc 芯片启动

一般我们做嵌入式开发都是用C语言编写实现,但是实际情况是在系统上电的之后,一般往往会执行一段初始化的汇编代码,可以理解为系统的BIOS。对于sparc v8架构的bm3803处理器来说,地址分配的空间如下:

一般芯片启动后,执行的代码都是在0地址处,所以固话的代码放在PROM的0地址空间。

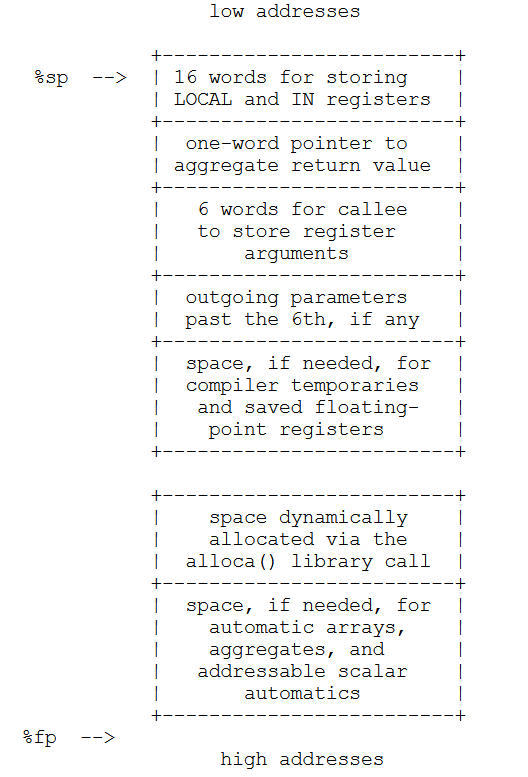

需要设置C语言可以执行的栈空间以及清除bss段。其中栈的布局可以参考如下:

3.寄存器

3.1 窗口寄存器

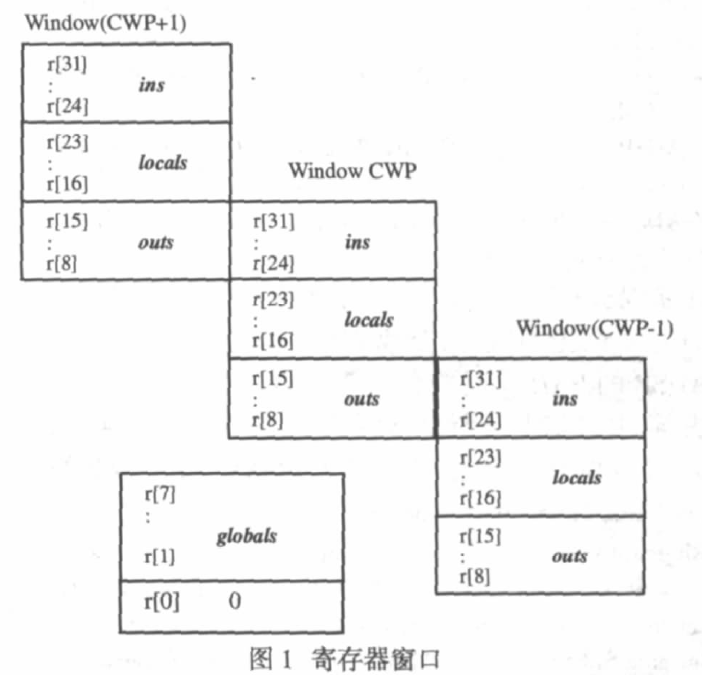

由于sparc架构集成伯克利RISC结构,所以窗口寄存器是一个非常重要的特性。也就是说,一个窗口寄存器组只对当前的程序可见。而一个寄存器窗口又包括32个无浮点的寄存器。

其中SPARC结构规定了一共可以有N个寄存器的窗口,N=2^n(1=

当执行SAVE指令的时候,会分配一个全新的串口CWP-1。当RESTORE指令的时候,则CWP+1。其中比较有特点是,两个窗口是有8个寄存器公用的,也就是上一个窗口的out为下个窗口的in。这样可以提高程序的执行效率,不用每次都处理所有的寄存器。

3.2 特殊寄存器

一般来说,sparc上的特殊寄存器需要注意的是处理器状态寄存器(Processor State Register),名称为%PSR。以及无效窗口标识(Widows Invalid Register),名称为%WIM。

其中PSR主要控制CWP窗口操作、中断处理开关、以及Trap的处理。

WIM是无效窗口,BIT0~BIT7分别对应窗口0~7,在CPU的8个寄存器窗口中只能存在一个窗口为无效窗口。

4.中断处理

在sparc处理中断和陷阱的时候,也是首先需要一个trap的地址。一般进入中断后,会进入另外的一个模式,也就是说会开辟一个新的窗口,比如我们做任务切换的时候。sparc是由软中断(TA指令)实现。SPARC架构是不支持直接对PC指针进行操作的,而是CPU在发生中断的时候会将当前的PC、NPC写到寄存器%l1,%l2寄存器中。在中断结束返回的时候,CPU自动将%l1,%l2内容写到PC、NPC。这样就实现了一个任务的切换过程。

当发生中断的嵌套的时候,也是需要通过中断栈来实现当前现场的保存。

5.总结

上述简单的介绍了一下sparc处理器的一些特点,熟悉处理器架构的朋友可以看一下和arm、mips、risc-v体系架构的设计的异同。通过学习和理解不同处理器架构的设计思想,从而更好的掌握程序设计的最佳思路。

-

jf_83900168

2024-11-22

0 回复 举报好看 收起回复

jf_83900168

2024-11-22

0 回复 举报好看 收起回复

-

ARM处理器的结构和特点2024-09-10 5016

-

欧空局为何从SPARC换成了RISC-V2022-12-21 2833

-

基于SPARC64架构的Arm超级处理器2022-12-20 1767

-

ARM微处理器的特点及其架构解析2022-04-13 6957

-

ARM处理器的特点有哪些2021-12-14 1452

-

ARM处理器的三大特点2021-12-13 1476

-

sparc v8架构的异常处理2020-09-25 3845

-

抗辐射SPARC处理器在航天应用中有什么优势?2019-08-28 2598

-

怎么通过sparc了解intel homologos处理器2018-11-06 1801

-

关于SPARC微处理器综述2017-11-01 1790

-

SPARC V8结构嵌入式微处理器的软件集成开发环境总体设计2017-10-31 1540

-

SPARC微处理器综合介绍2010-06-23 3417

-

REMS操作系统在SPARC-V8处理器上的应用2010-01-25 516

-

什么是SPARC处理器2009-12-17 1146

全部0条评论

快来发表一下你的评论吧 !